1 设计可靠性

为了增加可编程逻辑器件电路工作的稳定性,一定要加强可编程逻辑器件设计的规范要求,要尽量采用同步电路设计。对于设计中的异步电路, 要给出不能转换为同步设计的原因, 并对该部分异步电路的工作可靠性(如时钟等信号上是否有毛刺 建立-保持时间是否满足要求等)作出分析判断,提供分析报告。

2 时序分析基础

电路设计的难点在时序设计,而时序设计的实质就是满足每一个触发器的建立/保持时间的要求。

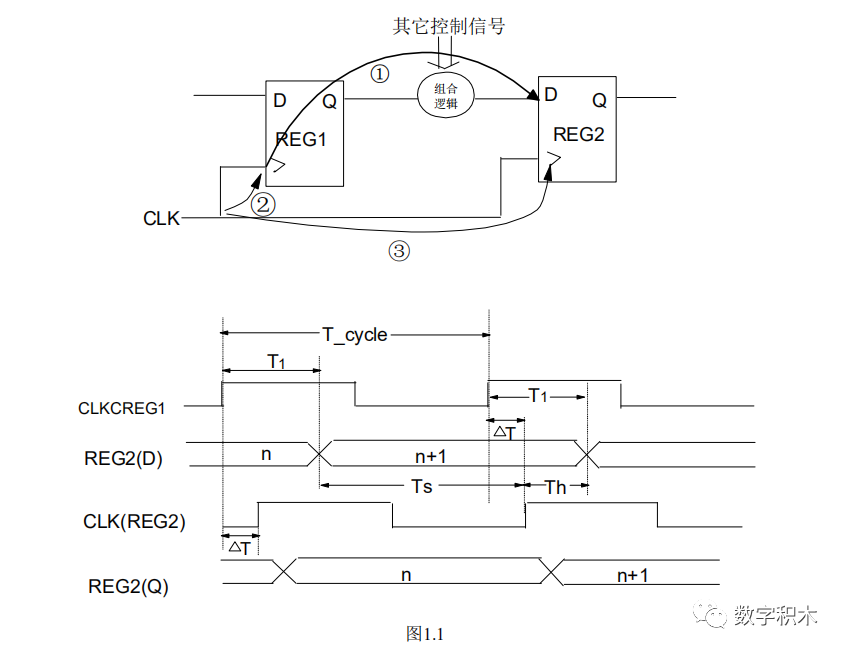

如上图所示,以REG2为例,假定 触发器的建立时间要求为:T_setup 保持时间要求为:T_hold 路径(1)延时为 T1,路径(2)延时为 T2,路径(3)延时为 T3,

时钟周期为 T_cycle,

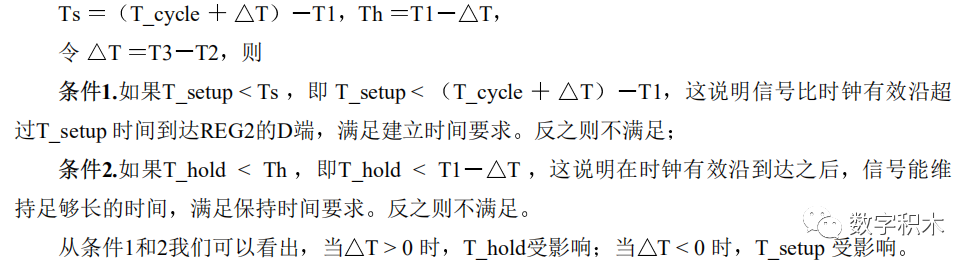

如果我们采用的是严格的同步设计电路,即一个设计只有一个CLK,并且来自时钟PAD或时钟BUFF (全局时钟),则 T对电路的影响很小,几乎为0.如果采用的是异步电路,设计中时钟满天飞, 无法保证每一个时钟都来自强大的驱动BUFF (非全局时钟),如下图所示,则 T影响较大,有时甚至超过人们想象,这就是为什么我们建议采用同步电路进行设计的重要原因之。

在这里插入图片描述

3 同步电路设计

3.1 同步电路的优越性

1.同步电路比较容易使用寄存器的异步复位/置位端,以使整个电路有一个确定的初始状态。

2.在可编程逻辑器件中,使用同步电路可以避免器件受温度,电压,工艺的影响,易于消除电路的毛刺,使设计更可靠,单板更稳定。

3.同步电路可以很容易地组织流水线,提高芯片的运行速度,设计容易实现。

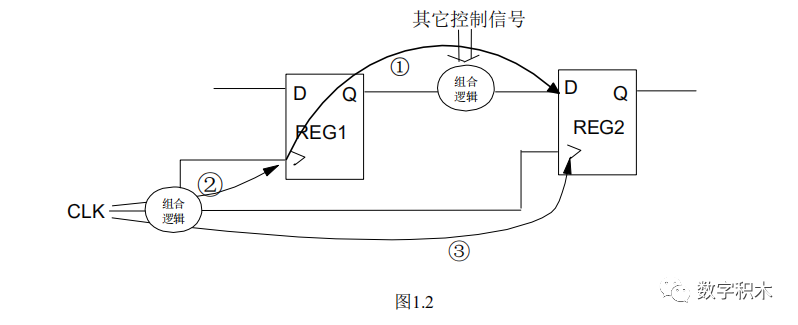

下图是一个设计中所要准备采用的电路,该设计采用Xilinx的FPGA器件4062xla来实现,工作频率是32.768MHz,即图中CLK频率。设计原打算在每隔60ns输出一个数据,即DATA 然而我们在设计之前 ,考虑到256x7的同步RAM延时可能比较大, 如果在加上其后的同步RAM延时的话 ,估计在60ns之内很难完成。该部分电路是整个设计中的一个关键路径, 因此, 我们在进行具体设计之前 ,先对这种电路结构进行了验证 ,事实证明我们的担心是对的 。正确的做法是。采用流水线方法, 在256x7的RAM之后再加一个触发器, 每个RAM都按60ns的速度读取数据 ,整个流程滞后60ns输出DATA ,其它相关信号(在其它模块中)也随之滞后60ns输出。

在这里插入图片描述

4.同步电路可以很好地利用先进的设计工具,如静态时序分析工具等,为设计者提供最大便利条件,便于电路错误分析,加快设计进度。

3.2 同步电路的设计规则

1.尽可能在整个设计中只使用一个主时钟,同时只使用同一个时钟沿,主时钟走全局时钟网络 。

2.在FPGA设计中 推荐所有输入,输出信号均应通过寄存器寄存,寄存器接口当作异步接口考虑。

3.当全部电路不能用同步电路思想设计时,即需要多个时钟来实现,则可以将全部电路分成若干局部同步电路,尽量以同一个时钟为一个模块,局部同步电路之间接口当作异步接口考虑 。

4.当必须采用多个时钟设计时,每个时钟信号的时钟偏差 T 要严格控制。

5.电路的实际最高工作频率不应大于理论最高工作频率,留有设计余量,保证芯片可靠工作 。

6.电路中所有寄存器,状态机在单板上电复位时应处在一个已知的状态。

3.3 异步设计中常见问题及其解决方法

异步电路设计主要体现在时钟的使用上,如使用组合逻辑时钟,级连时钟和多时钟网络,另外还有采用异步置位,复位,自清零,自复位等,这些异步电路的大量存在。一是增加设计难度 ,二是在出现错误时 ,电路分析比较困难 ,有时会严重影响设计进度。

很多异步设计都可以转化为同步设计 ,对于可以转化的逻辑必须转化, 不能转化的逻辑 ,应将异步的部分减到最小。而其前后级仍然应该采用同步设计, 下面给出一些异步逻辑转化为同步逻辑的方法。

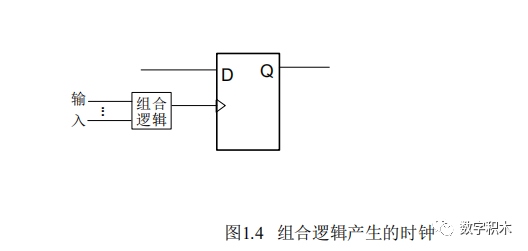

1.组合逻辑产生的时钟

组合逻辑的时钟如果产生毛刺,易使触发器误翻转。

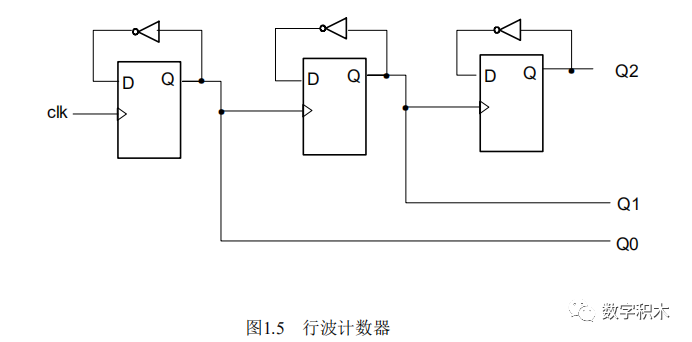

2.行波计数器/行波时钟

在这里插入图片描述

行波记数器虽然原理简单 ,设计方便 ,但级连时钟 ,行波时钟, 最容易造成时钟偏差 ,T级数多了, 很可能会影响其控制的触发器的建立/保持时间, 使设计难度加大 ,转换的方法是采用同步记数器 。同步计数器用原理图描述可能较难 ,但用VHDL很简单就可以描述一个4位计数器。Counter4: Process(nreset,clk) Begin If nreset = ‘0’ then Cnt <= ( others => “0” ); Elsif clk = ‘1’ and clk’event then Cnt <= cnt + 1; End if; End process counter4; 通常逻辑综合工具都会对上述描述按不同器件的特点进行不同的优化, 我们并不需要关心它是逐位进位计数器还是超前进位计数器。

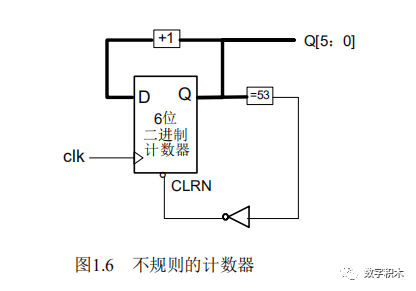

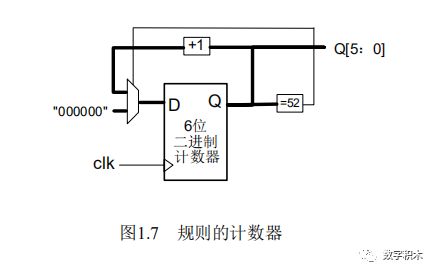

4.不规则的计数器

这是一个53计数器, 采用计到53后产生异步复位的办法实现清0 ,产生毛刺是必然的 ,然而最严重的是 ,当计数器所有bit或相关bit均在翻转时 ,电路有可能出错 。例如, 计数器从 110011> 110100 ,由于电路延时的原因, 中间会出现 110101 状态, 导致计数器误清0采用同步清0的办法 ,不仅可以有效地消除毛刺 ,而且能避免计数器误清0 ,电路如下图所示。

在这里插入图片描述

5.分频器

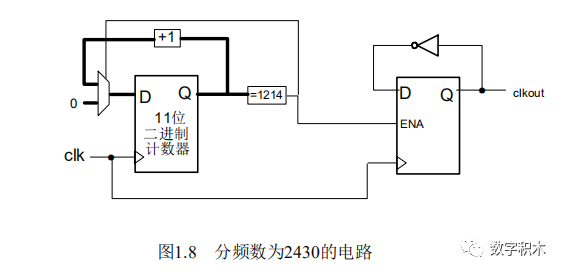

这是3和4的特例 ,我们推荐使用同步计数器最高位的方法, 如果需要保证占空比, 可以使用图1.8所示电路进行最后一次二分频 。下图是19.44MHz分频到8kMHz(分频数为2430)的电路。

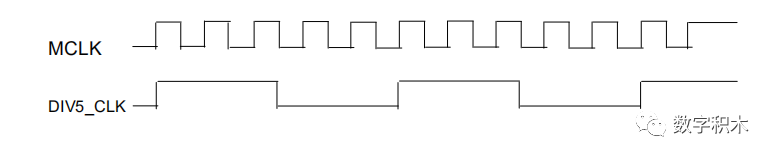

若是奇数分频, 则处理比较特殊, 以5分频器为例 ,其要求产生的时序关系如下图所示。

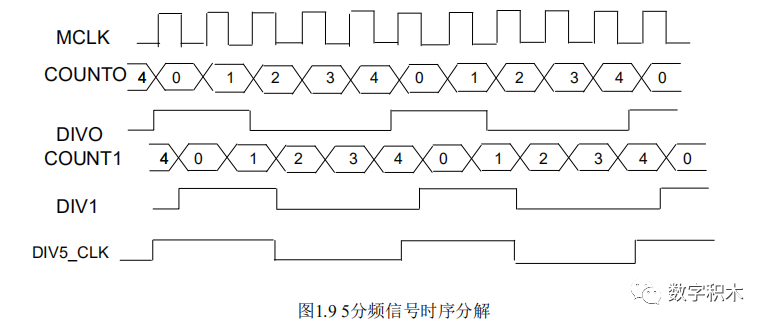

很显然 ,该电路要用上MCLK的上沿和下沿 ,对上图时序进行分解 ,得下图。

图中, COUNT0采用上沿计数, COUNT1采用下沿计数 ,DIV0和DIV1是分别是上沿触发器和下沿触发器的输出, DIV5_CLK是DIV0和DIV1的或门输出, 读者可根据该时序图, 画出相应的原理图, 或者用HDL语言进行描述在使用该电路时, 需要注意。1 DIV0和DIV1到DIV5_CLK的约束要严, 越快越好 ,不然, 无法保证1:1的占空比。2 MCLK频率要求较高, 尽量不要出现窄脉冲 ,尤其是在高频电路里。3 COUNT1可有可无 视时钟频率高低而定 ,频率越高 ,COUNT1越需要。

未完待续!!

往期精彩

【华为】可编程ASIC设计方法简介(三)

【华为】可编程ASIC设计方法简介(二)

【华为】可编程ASIC设计方法简介(一) 【华为】verilog语言编写规范(三) 【华为】verilog语言编写规范(二) 【华为】verilog语言编写规范(一) 【华为】Verilog HDL入门教程(5-10章) 【华为】Verilog HDL入门教程(4章) 【华为】Verilog HDL入门教程(3章) 【华为】Verilog HDL入门教程(1-2章) 【华为】FPGA设计设计规范本文完!!! 欢迎关注,更精彩的内容等着你!

最后

以上就是尊敬黄蜂最近收集整理的关于verilog编程规范(华为)_【华为】同步电路设计技术及规则(一)的全部内容,更多相关verilog编程规范(华为)_【华为】同步电路设计技术及规则(一)内容请搜索靠谱客的其他文章。

发表评论 取消回复