1.目标:使用verilog编写三分频电路,要求占空比大小为50%。

2.方法:分别使用上升沿和下降沿计数cnt_p以及cnt_n,并且计数从0到N-1(N为分频的次数,此时为3);分别对clk_p以及clk_n做复位初始化为0,这样当它们计数到0或者(N-1)/2的时候分别进行信号的翻转;如果clk_p以及clk_n初始化为0,结果是clk_p | clk_n,如果初始化为1则是clk_p & clk_n。

3. three_div_Freq.v

`timescale 1ns / 1ps

//

// Company: Shanghaitech

// Engineer: Junluoyu

//

// Create Date: 2021/11/02 22:48:53

// Design Name:

// Module Name: three_div_Freq

// Project Name:

// Target Devices:

// Tool Versions: vivado 2020.1

// Description: 三分频电路

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module three_div_Freq #(

parameter N = 3

)

(

input clk_in,

input rst_n,

output clk_out

);

/*----------------------------------------------------------------------------------------------*/

reg [3:0] cnt_p , cnt_n ;

reg clk_p , clk_n ;

/*----------------------------------------------------------------------------------------------*/

always @(posedge clk_in or negedge rst_n) begin

if(!rst_n)

cnt_p<=4'b0000;

else if(cnt_p==N-1)

cnt_p<=4'b0000;

else

cnt_p<=cnt_p+1'b1;

end

always @(negedge clk_in or negedge rst_n) begin

if(!rst_n)

cnt_n<=4'b0000;

else if(cnt_n==N-1)

cnt_n<=4'b0000;

else

cnt_n<=cnt_n+1'b1;

end

always @(posedge clk_in or negedge rst_n) begin

if(!rst_n)

clk_p<=1'b0;

else if(cnt_p==(N-1)/2)

clk_p<=~clk_p;

else if(cnt_p==4'b0000)

clk_p<=~clk_p;

else

clk_p<=clk_p;

end

always @(negedge clk_in or negedge rst_n) begin

if(!rst_n)

clk_n<=1'b0;

else if(cnt_n==(N-1)/2)

clk_n<=~clk_n;

else if(cnt_n==4'b0000)

clk_n<=~clk_n;

else

clk_n<=clk_n;

end

assign clk_out = clk_p | clk_n;

endmodule

4.testbench

`timescale 1ns / 1ps

//

// Company: Shanghaitech

// Engineer: Junluoyu

//

// Create Date: 2021/11/02 22:59:59

// Design Name:

// Module Name: tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tb();

/*---------------------------------------------------------------------------------------------*/

reg clk_in;

reg rst_n;

wire clk_out;

/*---------------------------------------------------------------------------------------------*/

three_div_Freq #(

.N(3)

)

three_div_Freq_inst

(

.clk_in (clk_in ),

.rst_n (rst_n ),

.clk_out(clk_out)

);

/*----------------------------------------------------------------------------------------------*/

initial clk_in = 1'b0;

always #5 clk_in = ~clk_in; // 10ns,50MHz

/*----------------------------------------------------------------------------------------------*/

initial begin

rst_n = 1'b0;

#100;

rst_n = 1'b1;

#1000;

$stop;

end

endmodule

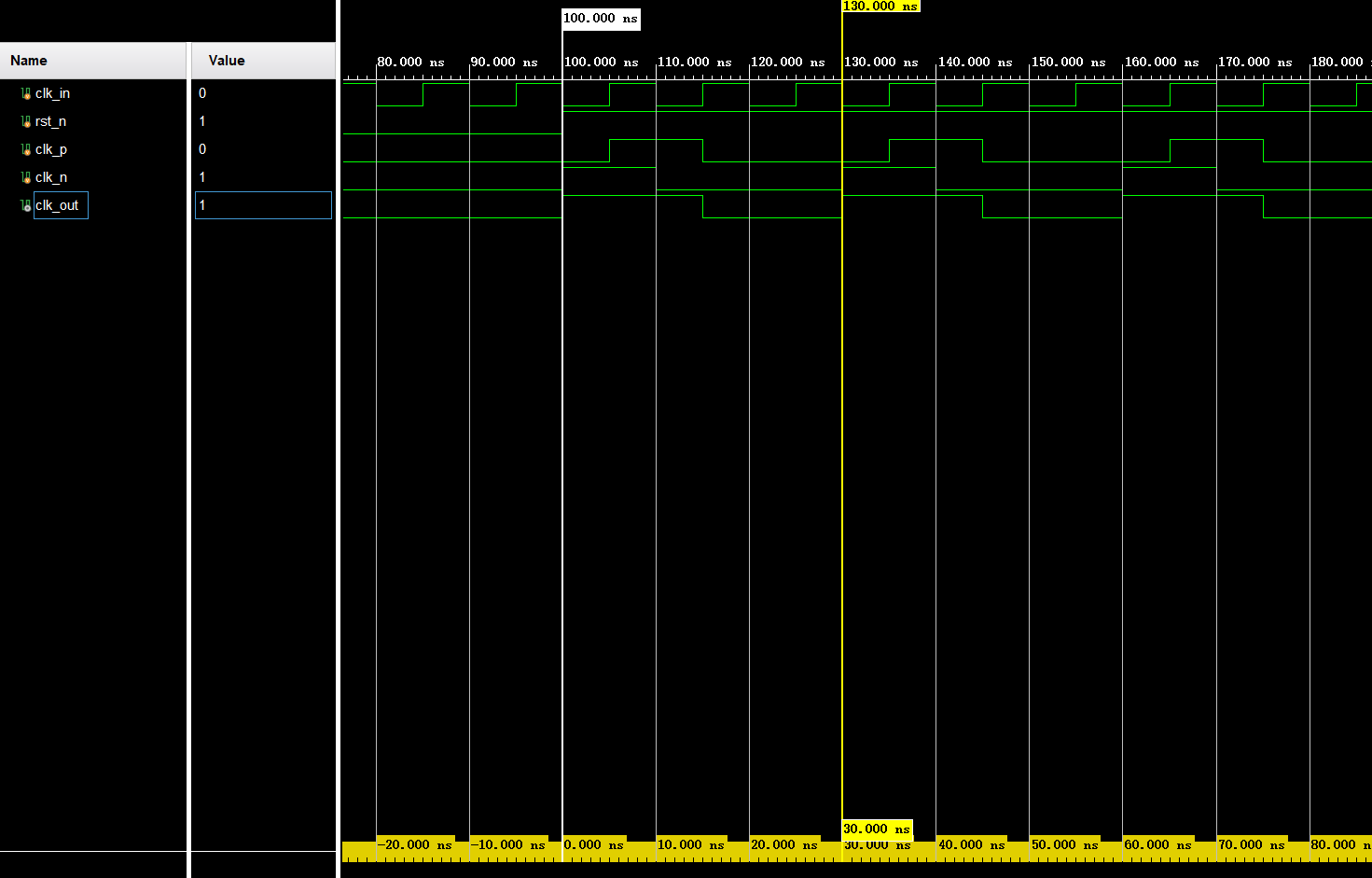

5.仿真波形

可见,生成的波形时钟周期为30ns,三分频即周期扩大三倍,故实现了三分频的功能。

6.扩展

如果实现其他奇数分频,只需要修改参数N为对应奇数即可。那么如果想得到占空比不是50%的应该怎么操作呢?

最后

以上就是英俊方盒最近收集整理的关于一、verilog编写三分频电路的全部内容,更多相关一、verilog编写三分频电路内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复