VIVADO实现AM调制信号(不带载波)

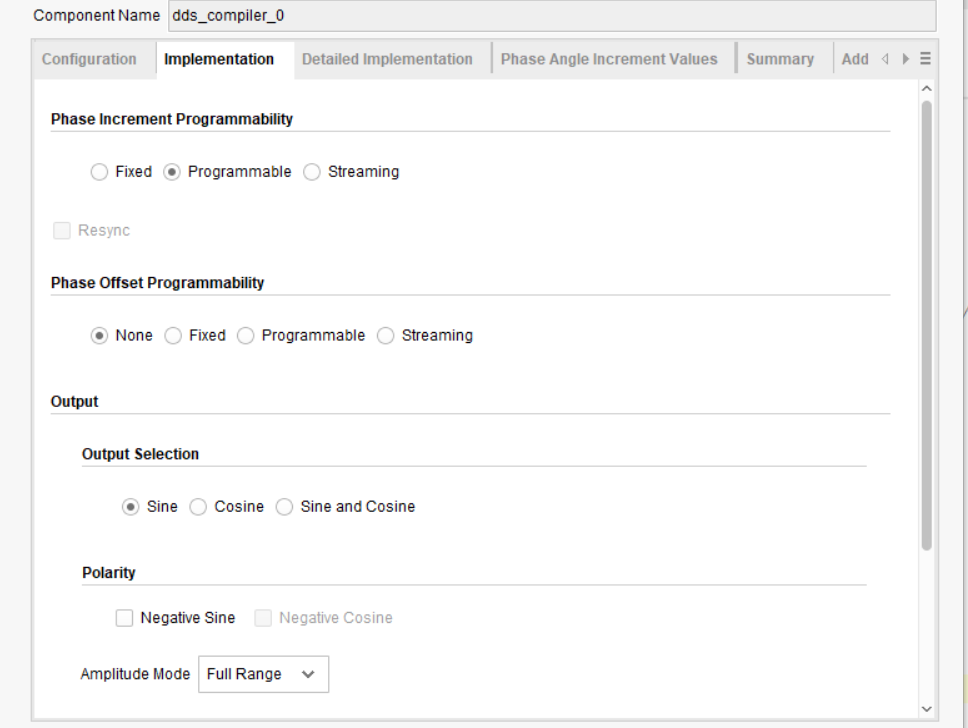

- 在上节中说了如何使用DDS的IP核,但是我们需要注意一点的事,我们㤇用频率控制字来控制频率的大小,所以在第二页的时候我们需要设置为可编程的。图如下

- 参数如上图设置,具体的频率设置在第一页,你需要多少频率就在fclk中设置。步进值就在设置频率的字宽中设置。f(步进)=fclk/2^字宽。

- 这就控制了我们的一个载波,当然本地信号也是用dds产生。

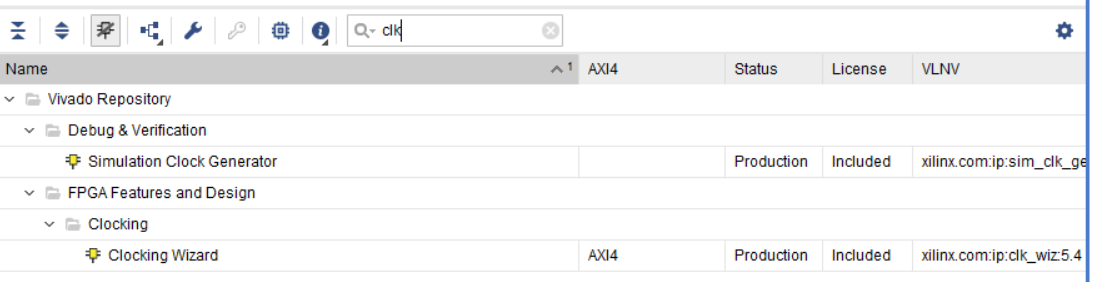

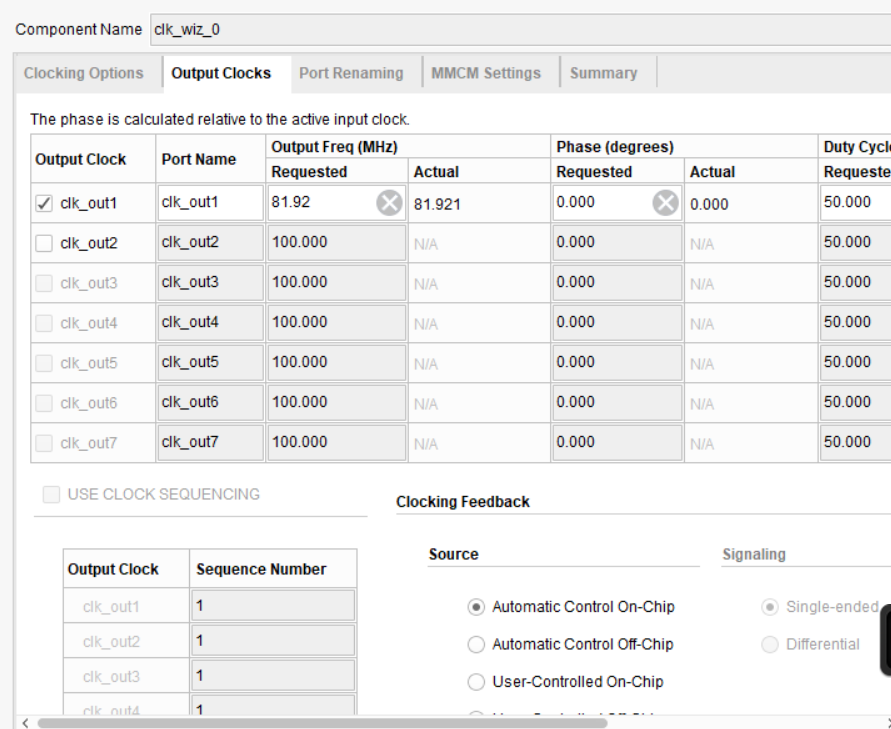

- fclk的提供由一个系统时钟分频模块产生,我们可以在IP核那一块搜索CLK,点击建立IP核

- 设置这个IP核我们需要注意一点,信号频率很低,无法直接由时钟模块得到,所以我们需要将时钟分频之后再供给调制信号的DDS内核

- 下面是分频模块

// 分频器

module count_xinhao(

input xinhao,

output clk

);

reg [6:0]count=1;

reg tran_clk=1;

assign clk=tran_clk;

always@(posedge xinhao) begin

if(count==50) begin //分频一百

tran_clk=~tran_clk;

count=0; //归零还是归一

end

else

count=count+1;

end

endmodule

- 我们需要做的是将CLK时钟产生的信号分频之后,供给DDS的内核,在我的设计中载波的DDS内核频率为81.92MHZ,而调制信号的内核为81.92KHZ,所以我们需要将它一千分频(我上面就是实验一下)

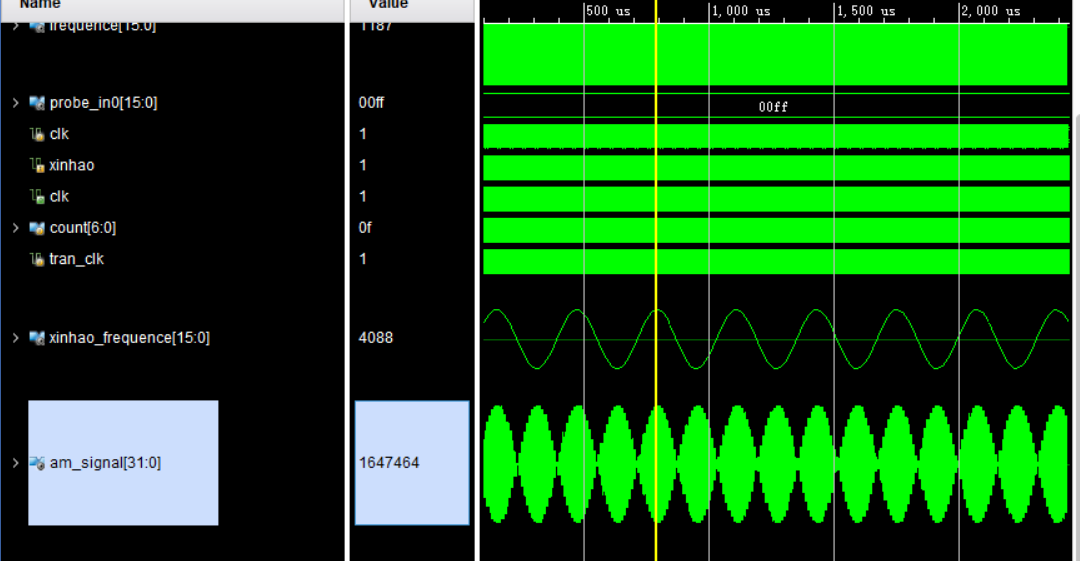

- 使用两个信号,目前我是直接用乘法器相乘,不能够调节参数ma,如果需要调节请接着看下面的章节。解调也会慢慢做完

信号调制

- 信号调制我们采用的是乘法器,在IP核里面搜索mul即可,我们使用最简单的IP核

- 用上面的IP核,调节数据宽度即可,我们,只需要将载波信号与调制信号相乘即可。

这个图是调制完的图,文件可以上传,接下来会做一下解调跟改变频率以及ma。

最后

以上就是威武水蜜桃最近收集整理的关于FPGA实现AM调制VIVADO实现AM调制信号(不带载波)的全部内容,更多相关FPGA实现AM调制VIVADO实现AM调制信号(不带载波)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复