提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

- 前言

- 一、异步FIFO

- 二、读写指针、空满判断、格雷码

- 三、异步FIFO中的时钟同步

- 三、FIFO的深度

- 四、Verilog设计代码

前言

异步FIFO用来处理跨时钟域的读写,知识点涉及跨时钟域、同步、读写指针、空满判断、格雷码等。

一、异步FIFO

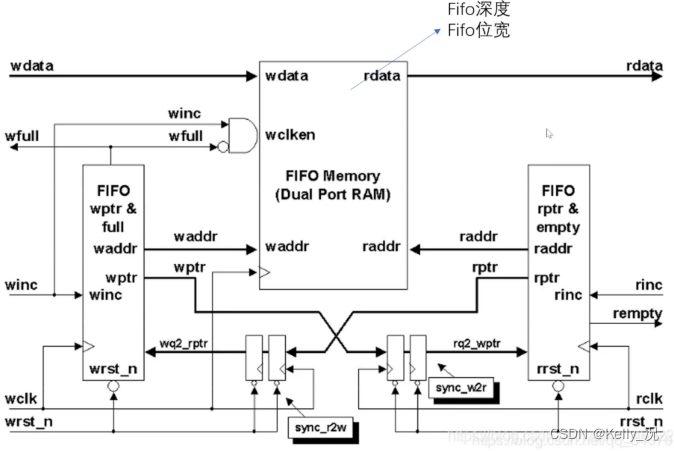

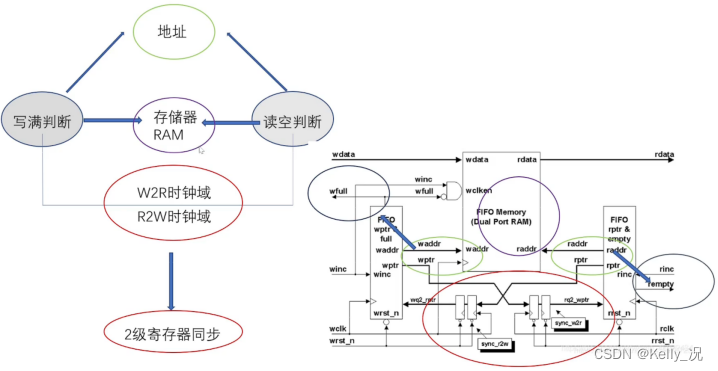

异步FIFO的结构如图所示。由读时钟域、写时钟域、Mermory模块和跨时钟域同步组成。

二、读写指针、空满判断、格雷码

读写指针随着读写操作在内存区域内循环移动。

写满:最高位不同,其余位相同

(可以理解为,写指针比读指针多跑一圈)

读空:所有位相同

(可以理解为,读指针赶上写指针)

二进制→格雷码:第一位不变,后面每位都是对应二进制码当前位和其左位的异或。

为什么使用格雷码?

如图红色地址跳变情况,对于二进制第2/3/4位都需要变化,而格雷码只有第2位需要变化,。信号在变化的过程中会成功/失败,二进制就会引发很多种情况,包含地址跨跳,使“空满”判定出现问题;格雷码则保持原位置/跳变成功,不会使“空满”判定出现问题。

三、异步FIFO中的时钟同步

先上结论:

同步rd_cntr至clk_write时钟域,再与wr_cntr进行对比来决定FIFO是否满;(判断满是wr_cntr - rd_cntr)

同步wr_cntr至clk_read时钟域,再与rd_cntr进行对比来决定FIFO是否空;(判断空是rd_cntr == wr_cntr)

其中缘由:

对于fifo来说,无论是写地址在读时钟下同步,还是读地址在写时钟下同步,被同步地址都会是延迟两个时钟周期之前的地址,所以在进行比较判断的时刻,参与判断的同步地址总是小于等于当前时刻的真实地址。

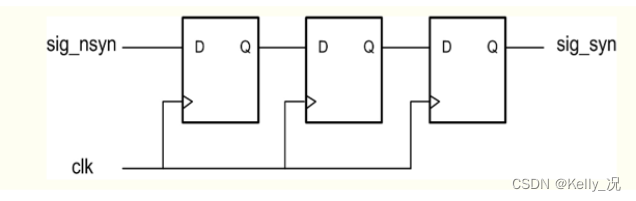

增加两个寄存器来实现时钟同步

判满:满信号判断条件为写地址是否超读地址一圈,为了避免继续超前写,(写太快了)将读指针同步到写时钟域;

判空:空信号判断条件为读地址是否追上写地址,为了避免超前读,(读太快了)将写指针同步到读时钟域。

FIFO满是对于写操作有用的(因为满了就不可以写了),所以满信号必须同步到写时钟之下。而FIFO空是对读操作有用的(因为空了就不可以读了),所以空信号必须同步到读时钟之下。

三、FIFO的深度

在求解之前需要验证一下在允许的最大时间长度内写入的数据量是否等于读出的数据量,保证有解;

•求FIFO深度需要考虑最坏的情形,读写的速率应该相差最大,也就是说需要找出最大的写速率和最小的读速率;

•不管什么场景,要确定FIFO的深度,关键在于计算出在突发读写这段时间内有多少个数据没有被读走;

•由于FIFO空满标志位的判断延迟,在实际应用中需要预留一些余量。

下面我们来推导一下FIFO深度的求解公式,假设:

•写时钟频率为fwr

•读时钟频率为frd

•在写时钟周期内,每m个周期内就有n个数据写入FIFO

•在读时钟周期内,每x个周期内可以有y个数据读出FIFO

那么:

•首先必须满足(1/fwr)(m/n) ≥ (1/frd)(x/y)

•”背靠背“的情形下是FIFO读写的最坏情形,burst长度 B = 2n

•写完burst长度数据最快所需时间 T = (1/fwr)B

•从FIFO中读出一个数据至少需要时间 t= (1/frd)(x/y)

•在T时间内能够从都走的数据个数 = T/t = B * (frd/fwr)(y/x)

•在T时间内还没有读走的数据个数 = B-B* (frd/fwr)(y/x)

•因此FIFO的最小深度为 B-B * (frd/fwr) (y/x)

•注意保留一些余量

四、Verilog设计代码

待更新

最后

以上就是积极汽车最近收集整理的关于IC验证:异步FIFO前言一、异步FIFO二、读写指针、空满判断、格雷码三、异步FIFO中的时钟同步三、FIFO的深度四、Verilog设计代码的全部内容,更多相关IC验证:异步FIFO前言一、异步FIFO二、读写指针、空满判断、格雷码三、异步FIFO中内容请搜索靠谱客的其他文章。

发表评论 取消回复