1.同步复位和异步复位的区别:

同步复位是复位信号随时钟边沿触发有效。异步复位是复位信号有效和时钟无关。、

2.同步逻辑和异步逻辑的区别:

同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系

3.同步电路和异步电路区别:

同步电路有统一的时钟源,经过PLL分频后的时钟驱动的模块,因为是一个统一的时钟源驱动,所以还是同步电路。异步电路没有统一的时钟源。

异步电路:

a) 电路核心逻辑有用组合电路实现;

b) 异步时序电路的最大缺点是容易产生毛刺;

c) 不利于器件移植;

d) 不利于静态时序分析(STA)、验证设计时序性能。

同步电路:

a) 电路核心逻辑是用各种触发器实现;

b) 电路主要信号、输出信号等都是在某个时钟沿驱动触发器产生的;

c) 同步时序电路可以很好的避免毛刺;

d) 利于器件移植;

e) 利于静态时序分析(STA)、验证设计时序性能。

4. 同步时钟:当两个时钟间的相位是固定关系的,则可以称这两个时钟为同步时钟(synchronous clock)。经过一个 PLL 产生相位不同,但相位固定的两个时钟,他们依旧是同步时钟。

异步时钟:如果是两个晶振产生的时钟,因为两个晶振在上电时相位差是随机的,而且不同晶振时钟漂移抖动也不一样,所以相位是不固定的。当无法判断两个时钟间的相位时,则可以称这两个时钟为异步时钟(asynchronous clocks)

5.同步FIFO与异步FIFO:

概念:同步 FIFO 的写时钟和读时钟为同一个时钟, FIFO 内部所有逻辑都是同步逻辑,常常用于交互数据缓冲。 异步 FIFO 的写时钟和读时钟为异步时钟, FIFO 内部的写逻辑和读逻辑的交互

需要异步处理,异步 FIFO 常用于跨时钟域交互。

异步FIFO:数据流的传输与指示信号不同在于:数据流大多具有连续性,及背靠背传输;数据流要求信号具有较快的传输速度。 主要的方案是利用 FIFO 进行传输。

6.异步FIFO的设计:

组成:

• FIFO Memory 双口 RAM 存储数据

• sync_r2w 同步读数据指针到写时钟域

• sync_w2r 同步写数据指针到读时钟域

• wptr_full 处理写指针和满信号的逻辑

• rptr_empty 处理读指针和空信号的逻辑

设计原则:能写满而不溢出,能读空而不多读。

在写时钟域下,判断读写指针的关系,生成满标志。在读时钟域下,判断读写指针的关系,生成空标志。

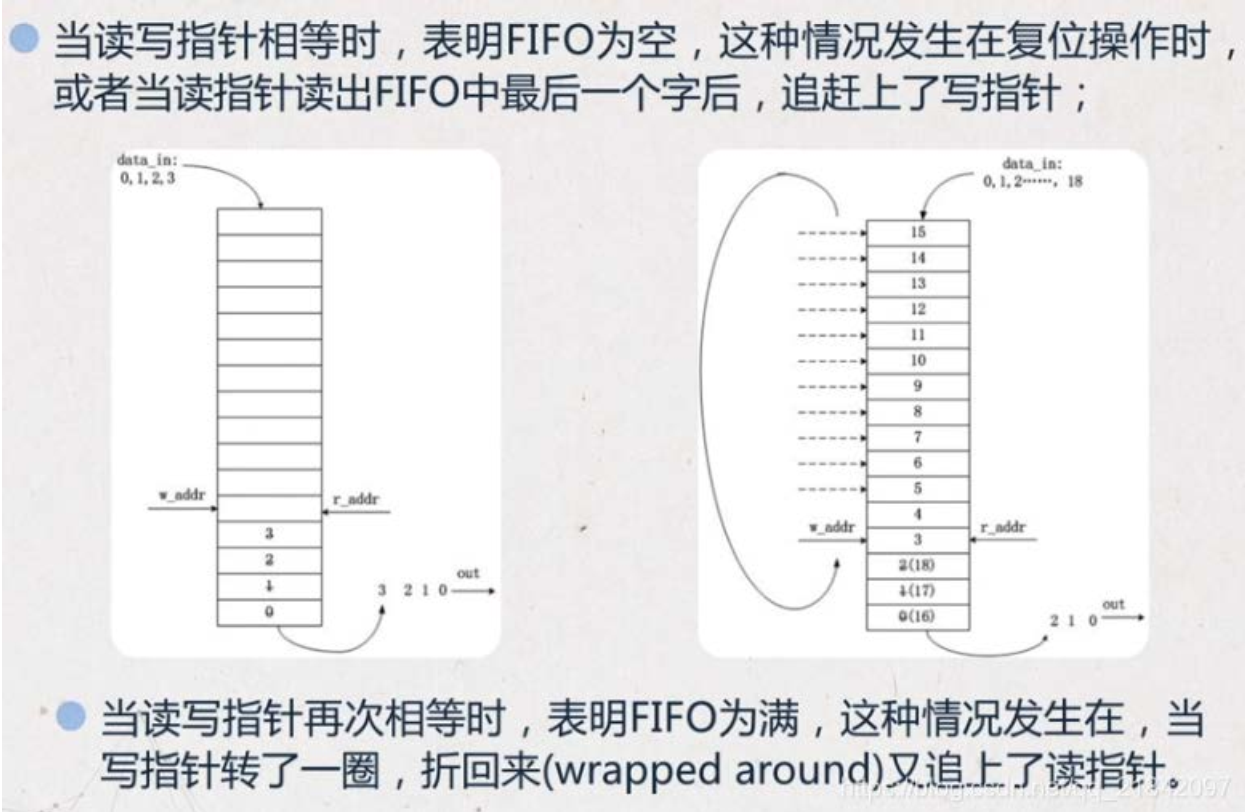

7.读写指针相等时如何判断空还是满呢?

在地址中额外添加一个位,当写指针增加并越过最后一个地址位时,就将这个额外的位(MSB)

加一,其他位回 0。读指针也进行同样的操作。 额外的位作为折回标志位。如果两个指针的

MSB 不同,其余位相等,说明读指针比写指针少折回了一次,这种情况下, FIFO 为满。而

读写指针所有位都相等,说明折回次数相等,此时 FIFO 为空。

8.读写指针同步

二进制的读写指针通常位宽超过了 1bit,而多比特信号是不可以直接使用两级同步器的。

这时,考虑到 FIFO 地址是连续变化的,我们使用格雷码来进行传输。格雷码相邻两个数值只有一位发生变化, 0 和最大数之间也只有一位不同。

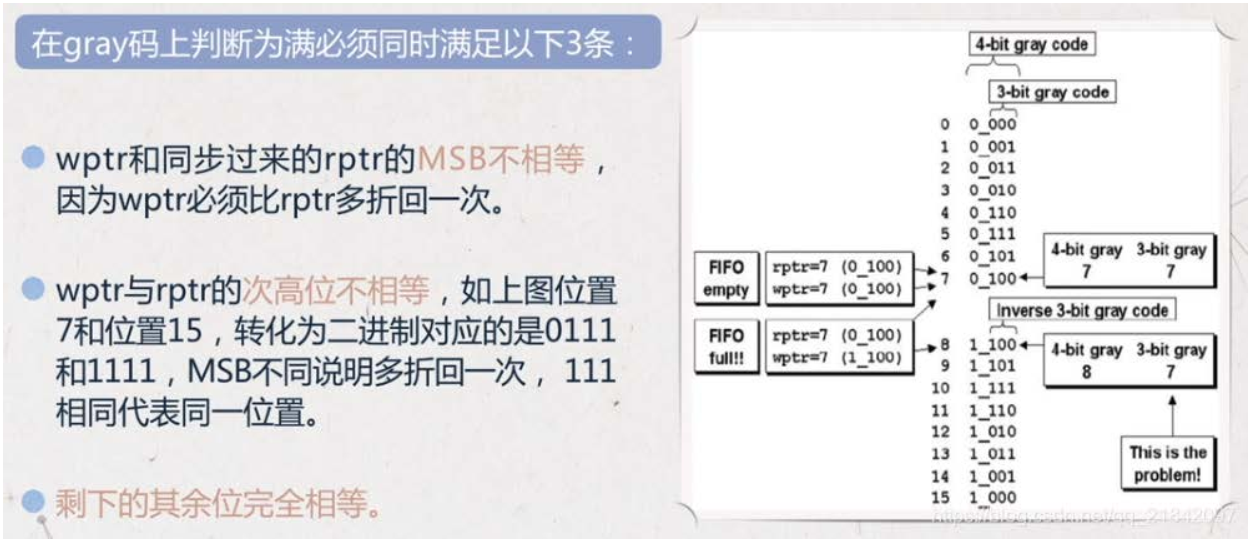

9.格雷码空满判断

格雷码的值只需要在原来的二进制的基础上右移一位再加上原来的二进制值即可得到。

连续的格雷码之间只有单比特信号变化,多用在异步时钟域处理上,如异步FIFO中地址指针的索引就采用格雷码编码。

最后

以上就是苹果百褶裙最近收集整理的关于5.同步与异步,FIFO的全部内容,更多相关5内容请搜索靠谱客的其他文章。

发表评论 取消回复