FPGA项目设计中,通常会遇到多时钟处理。即一个PLL输出多个时钟,根据条件选择合适的时钟用作系统时钟。

方案一:

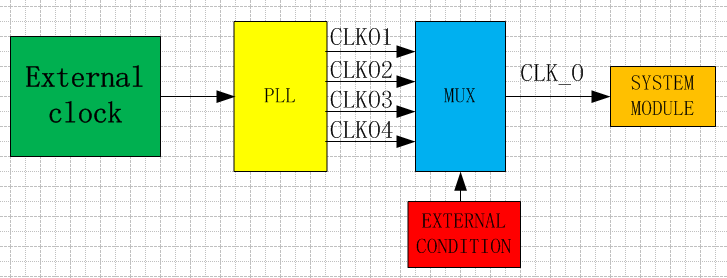

外部晶振时钟进入PLL,由PLL输出多个时钟,MUX根据外部条件选择时钟输出做为系统使用。

方案在时钟频率比较低的情况下是可行的。设计时注意MUX使用组合逻辑实现的,注意case语句中default选项必须有输出,否则会出现锁存器。

当输出时钟频率较高时,这种方案的时序约束就比较麻烦。除了使用creat_clock命令约束PLL输入时钟,使用creat_generate_clock约束PLL输出时钟外,还要根据PLL输出的多个时钟之间的关系,使用set_clock_groups约束。set_clock_groups:

-

-

asynchronous表示时钟同时有效,但没有相位关系。

-

exclusive 表示时钟是互斥的

-

group,group之内的时钟相关,group之间的时钟互不相关。

-

这种设计使得时钟约束变得繁琐,时序变得紧张。

同时PLL输出时钟后使用MUX进行选择输出,会增加时钟布线延时,高速情况下并不可靠。

时序是设计出来的,不是约束出来的。

设计出好的时序一般不需要约束。

方案二:

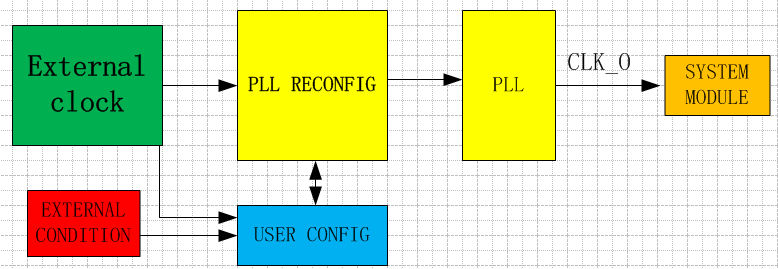

在高速情况下,应该更改设计,提高电路速度。ALTERA FPGA提供PLL重配功能。可根据条件对PLL进行重配。

调用ALTERA提供的PLL重配模块,根据官方资料,可以动态的对PLL重新配置。这样PLL输出时钟直接驱动系统模块,将多时钟域转换到单时钟域上。不需要添加附加约束电路都可以正常工作。

方案三:

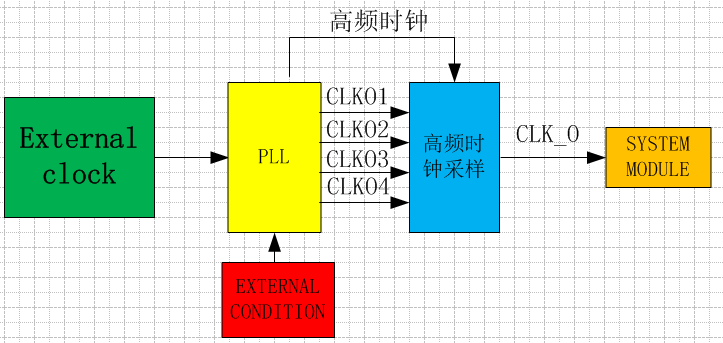

第三种方案,这里稍微介绍一下。

PLL输出一个高频时钟HCLK,其他时钟作为HCLK的使能端,用HCLK采样其他时钟,这也是一个可以考虑的方案,这个方案也不会造成多时钟处理及约束。但此方案也有限制,要求HCLK时钟频率至少是PLL输出其他时钟最高频率的两倍以上,这样才能满足采样定理,即奈奎斯特定理。在时钟频率比较低时,亦可以考虑此方案。

文章来源:FPGA极客空间微信公众号

版权所有权归卿萃科技,转载请注明出处。

作者:卿萃科技ALIFPGA

原文地址:bbs.alifpga.com

扫描二维码关注FPGA极客空间。

转载于:https://www.cnblogs.com/alifpga/p/7493996.html

最后

以上就是细心荷花最近收集整理的关于FPGA多时钟处理应用的全部内容,更多相关FPGA多时钟处理应用内容请搜索靠谱客的其他文章。

发表评论 取消回复