题目要求

设计基于FPGA的低频方波频率、占空比测量仪。实时测量输入方波信号的频率与占空比。

指标要求

1) 输入方波频率1Hz~1kHz;幅度VH=3V, VL=0V

2) 测量误差优于10-4;显示分辨率0.1Hz

3) 采用4位数码管显示,其中3位整数,1位小数

4) 拨码开关控制测频率与测占空比的功能转换

- 设计原理:

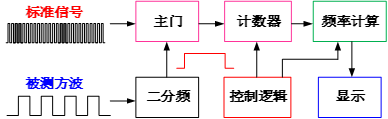

设计原理流程图如图 1:

图 1设计原理流程图

将低频被测信号通过I/O口送入,通过一个二分频单元,二分频后作为计数器的使能信号;延时两个标准信号周期作为读信号,读取计数器计数值,传给数据处理模块;延时四个标准信号周期作为清零信号,将计数器置零,重新计数;最后经过数据处理计算出频率值与占空比值,再传给数码管显示模块,显示出频率或占空比。

- 测频率

- 测频法

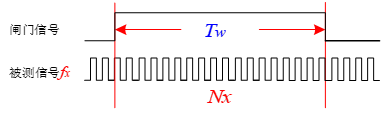

在确定的闸门时间 Tw 内,记录被测信号的变化周期数(或脉冲个数) Nx。如图 2所示。

图 2测频法原理图

被测信号频率为: fx = NxTw (1)

- 测周法

在待测信号的一个周期Tx内,记录频率为fs的标准信号周期数Ns。如图 3。

图 3测周法原理图

被测信号频率为:fx = fsNs (2)

因为测频法和测周法都会产生±1个字误差, 且测量精度与Nx或Ns有关。为保证精度, 一般低频信号采用测周法, 高频信号采用测频法。题目要求测量范围属于低频范围,所以测量频率选用测频法较好。

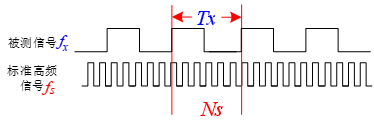

- 时序分析

如图 4所示,输入被测信号后,经过二分频模块得到信号En,在En为高电平时,计数标准信号周期个数Ns,Em同被测信号;当En与Em同时为高时,计数标准信号周期个数Nh;

En延时2个标准信号周期后读取Ns,Nh的值送入数据处理模块,延时4个标准周期后清零信号对计数器计数值进行清零。

图 4时序分析图

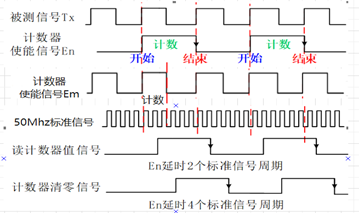

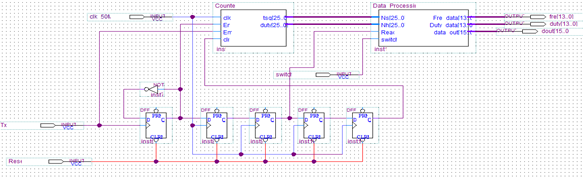

- 模块设计

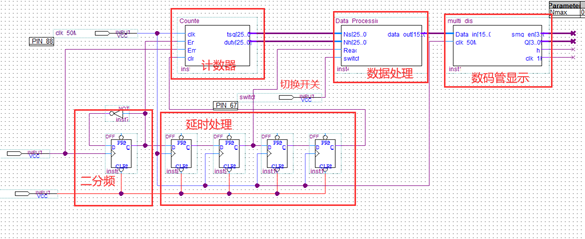

如图 5所示,计数器模块同时计数频率Ns值与占空比Nh值,数值传给数据处理模块,由数据模块switch信号切换频率数值或占空比数值输出,数值传给数码管显示模块显示。

由反相器与一个D触发器设计二分频单元,触发信号为Tx,后面四个D触发器为读信号和清零信号延时,由50Mhz标准信号触发,延时两个标准信号单元为Read信号,延时四个标准单元为clr信号;复位信号控制五个D触发器的使能信号。

图 5系统总体设计图

模块代码展示:

1.计数器

module Counter(clk,En,Em,clr,tsq,duty);

input clk,clr,En,Em;

output reg [25:0] duty;

output reg [25:0] tsq;

always@(posedge clk or negedge clr)

begin

if(!clr)

begin

tsq<=26'd0;

duty<=26'd0;

end

else

begin

if(En)

begin

tsq<=tsq+1;

if(En&Em)

duty<=duty + 1;

end

end

end

endmodule

2.数据处理

module Data_Processing(Ns,Nh,Read,switch,data_out);

input Read,switch;//读信号与频率占空比切换开关

input [25:0] Ns;//计数clk周期数输入

input [25:0] Nh;//高电平clk周期数输入

reg [13:0] Fre_data;//频率

reg [13:0] Duty_data;//占空比

output reg [15:0] data_out;//输出数据

reg [30:0] Ns_data;//计数clk周期数

reg [30:0] Nh_data;//高电平clk周期数

always@(negedge Read)

begin

Ns_data <= Ns+4;//修正

Nh_data <= Nh;

end

always@(Ns_data)

begin

if(switch)

begin//计算评率

Fre_data = 500000000/Ns_data;

data_out[15:12] = Fre_data/1000;

data_out[11:8] = (Fre_data%1000)/100;

data_out[7:4] = (Fre_data%100)/10;

data_out[3:0] = Fre_data%10;

end

if(!switch)

begin//计算占空比

Duty_data = (Nh_data*1000)/Ns_data+1;

data_out[15:12] = 0;

data_out[11:8] = (Duty_data%1000)/100;

data_out[7:4] = (Duty_data%100)/10;

data_out[3:0] = Duty_data%10;

end

end

endmodule

3.数码管显示模块

module multi_disp(Data_in,clk_50M,smg_en,Q,h,clk_1k);

input clk_50M;

input[15:0] Data_in;

output reg[3:0] smg_en=0;

output reg[3:0] Q=0;

output reg h=0;

output reg clk_1k=0;

reg [31:0] counter=0;

reg [1:0] cnt=0;

parameter Nmax=32'd25_000; //1k

always@(posedge clk_50M)

begin

if(counter==Nmax-1)

begin

counter<=0;

clk_1k<=~clk_1k;

end

else

counter<= counter + 1;

end

always@(posedge clk_1k)

begin

if(cnt==3)

cnt<=0;

else

cnt <= cnt + 1;

end

always@(posedge clk_1k)

begin

case(cnt)

0:begin smg_en<=4'b0001; Q<=Data_in[15:12];h<=0; end

1:begin smg_en<=4'b0010; Q<=Data_in[11:8]; h<=0; end

2:begin smg_en<=4'b0100; Q<=Data_in[7:4]; h<=1; end

3:begin smg_en<=4'b1000; Q<=Data_in[3:0]; h<=0; end

endcase

end

endmodule

- 仿真分析

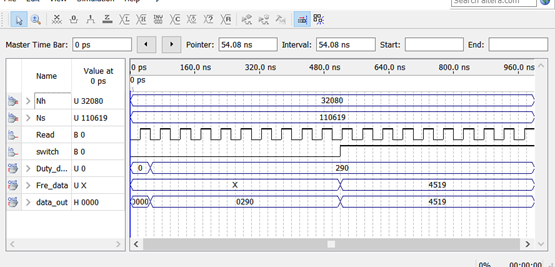

- 计数模块:

在计数模块中tsq为频率计数值,duty为占空比计数值,并非占空比值。

计算公式tsq=50_000_000/fre duty=fre*占空比

用quartus自带仿真,仿高频信号,由于测周法实用于测低频,如果高频信号也能满足,则低频信号也能满足。

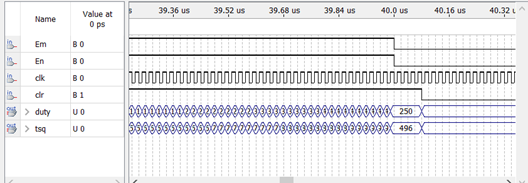

- 测量100Khz频率占空比为50%的信号。

设置Em为100Khz,En为Em的二倍频200Khz,clk为标准50Mhz,clr为En信号延时80ns信号(即4个标准信号周期)。

理论测得tsq=500,duty=250。

实际仿真测得duty=250,tsq=496,由于clr信号延时四个标准信号周期,所以tsq=500-4,后期数据处理模块会将Ns补4,符合理论结果,如图 6所示。

图 6计数器模块第一组数据仿真图

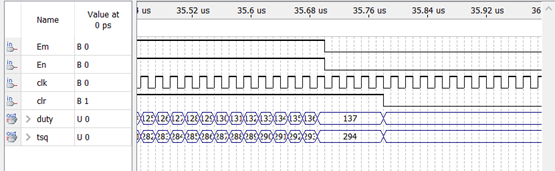

- Em设置为168Khz,占空比为46%的信号,En设置为336Khz占空比为50%,clr为En延时80ns。

理论测得tsq=298(297.6四舍五入),duty=137(136.9四舍五入)

实际仿真测得tsq=294,duty=137,tsq补4后符合理论结果,如图 7所示。

图 7计数器模块第二组数据仿真图

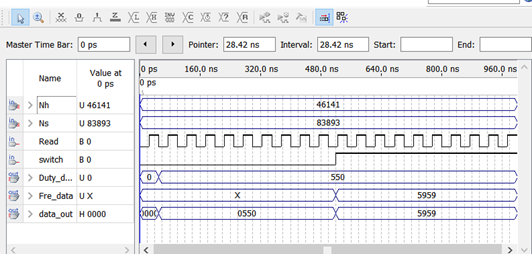

- 数据处理模块:

Nh为占空比计数值,Ns为频率计数值,Read为读信号,switch为占空比频率输出转换开关,Duty_data为占空比值*10,Fre_data为频率值*10(因为测量精度为小数点后一位),

Data_out为输出数据。

A、为了随机性,随机选择一个低频信号,596Hz,占空比为55%的信号。

根据公式Ns=50_000_000/频率,Nh=Ns*占空比。将Ns设为83893,Nh为46141。

理论测得Duty_data=550,fre_data=5960

实际仿真测得Duty_data=550,fre_data=5959频率与理论测量值相差1,但误差满足设计要求。

由于在仿真与实际测试中发现,Duty_data在低频范围内测量均存在与实际值少1的误差,索性在data_out的最后一位+1,优化测量误差,但这只是一个不严谨的方法,只是在题目要求中可以满足。如图 8。

图 8数据处理模块第一组仿真图

B、随机选择452hz、占空比29%的信号,将Ns设为110619,Nh设为32080。

理论测得Duty_data=290,Fre_data=4520。

实际仿真测得Duty_data=290,Fre_data=4519。频率与理论值相差1,误差符合设计要求。

图 9数据处理模块第二组仿真图

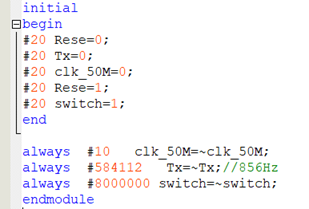

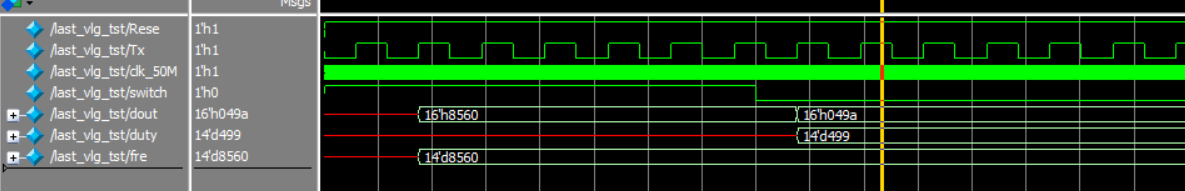

- 总体仿真:

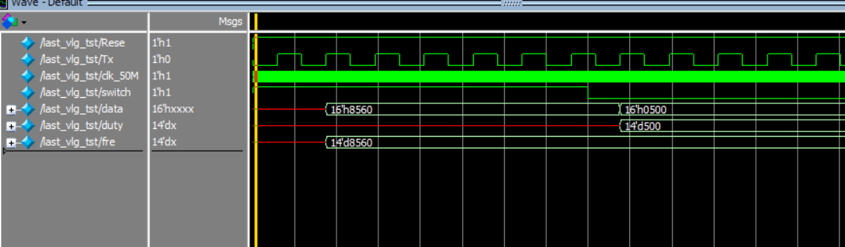

总体仿真电路图如图 10所示,随机选取了856Hz占空比为50%的信号测试,仿真结果如下图所示。频率仿真得到fre_data=8650,占空比为499,dout补1后输出得500符合题目设计要求。

图 10总体仿真电路图

测试文件设置如图 11

单位1ns,精度1ns。

图 11测试文件图

图 12总体仿真测试图(错误版)

Switch为1时输出频率值8560,为0时输出低电平049a即500。如上图 12所示。

此仿真为错误,原因是为了弥补误差,我在数据处理模块中dout[3:0]处+1,所以dout[3:0]本为9时,+1后变成了a,由于数码管译码只能译0—9,所以在数码管上无显示a,在实测中最后一位就无法显示。

图 13总体仿真测试图(修正版)

发现错误后,将Duty_data+1后再分配给dout,将错误改正。如上图 13所示。

- 实测展示

- 最终版

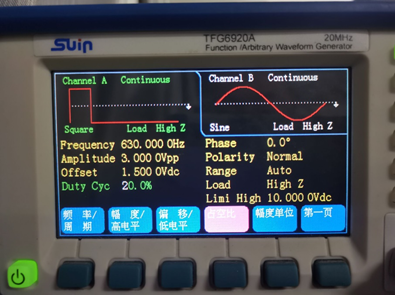

最终版本,测量630hz,占空比20%信号。

图 14信号发生器界面

图 15占空比测量 图 16频率测量

- 初版

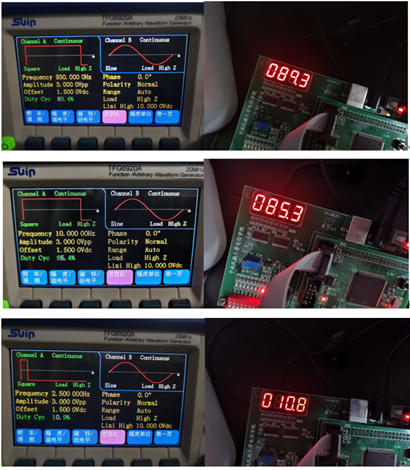

初次测试中出现的问题如图 17:在1~1000hz范围内占空比总是少0.1。

图 17三组初版设计实际测量结果

将设计改良后,测试时扭动信号发生器旋钮改变被测信号频率发现,频率测量实际值与信号发生器一致,扭动信号发生器改变被测信号占空比发现,占空比测量实际值也与信号发生器均一致。(扭动频率旋钮步进为10hz,扭动占空比旋钮步进0.1%与1%)。

最后

以上就是高兴小蘑菇最近收集整理的关于基于FPGA低频方波测量-频率与占空比的全部内容,更多相关基于FPGA低频方波测量-频率与占空比内容请搜索靠谱客的其他文章。

发表评论 取消回复