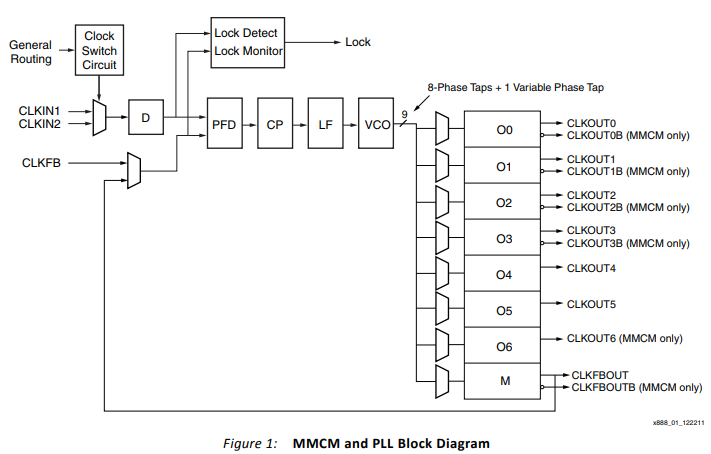

1、结构:MMCM和PLL

mixed-mode clock manager (MMCM),phase-locked loop (PLL)

这两种primitive架构不同,MMCM实现更复杂一些,具有更多的features。

MMCM可以实现Spread Spectrum和差分输出,最多可以出7个clock,PLL最多6个。倍频分频的方式也不同。

2、动态配置:Dynamic Reconfig

允许user通过控制接口改变clock

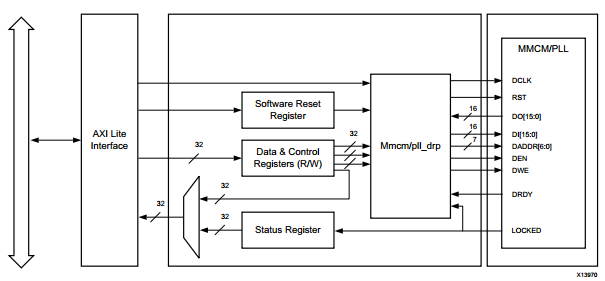

3、配置接口:AXI4Lite和DRP

控制接口可以是AXI总线的,也可以是厂家的DRP接口。根据逻辑设计需要选择。

dynamic reconfiguration port (DRP)

4、其他Options

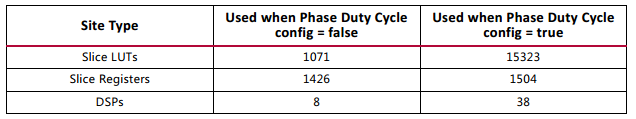

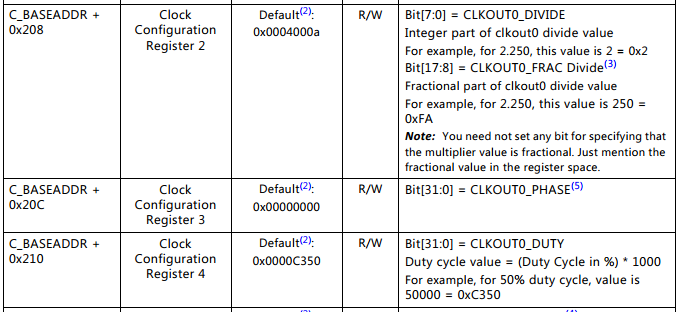

a、Phase Duty Cycle Config

相位和占比也可以配置,代价是资源占用成倍增加。

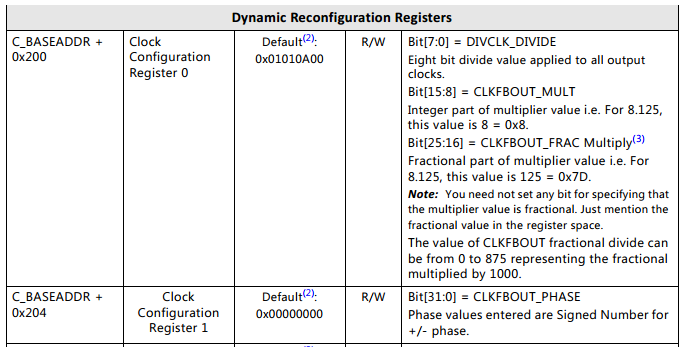

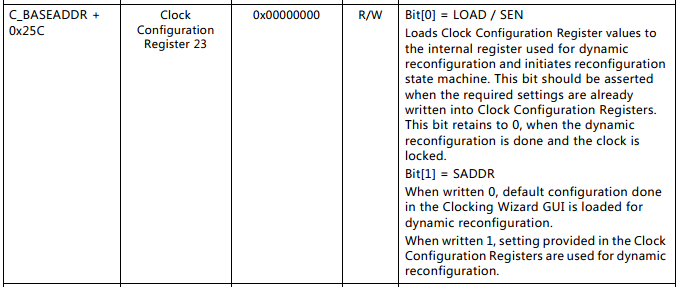

b、Write DRP registers

相当于用AXI接口直接控制DRP的寄存器,主要优点是在接口这块可以不使用DSP资源。

但是也会缺少一些可选配置,同时偏移地址不同。比如AXI-0x200位置对主频的重新配置,在DRP-0x300中就没有。

对clkout的三项配置都一样。

reg配置完成了,往使能寄存器中写0x03,让配置生效。

我的需求:通过ps动态配置,频率档位越细越好,占比可变,但同时也希望资源占用尽量少点。

所以选择:DynamicReconfig、AXI4Lite、Phase Duty Cycle Config。

转载于:https://www.cnblogs.com/kevinchase/p/8686106.html

最后

以上就是活力豆芽最近收集整理的关于【vivado】clocking wizard 时钟配置的全部内容,更多相关【vivado】clocking内容请搜索靠谱客的其他文章。

发表评论 取消回复