奇数分频器

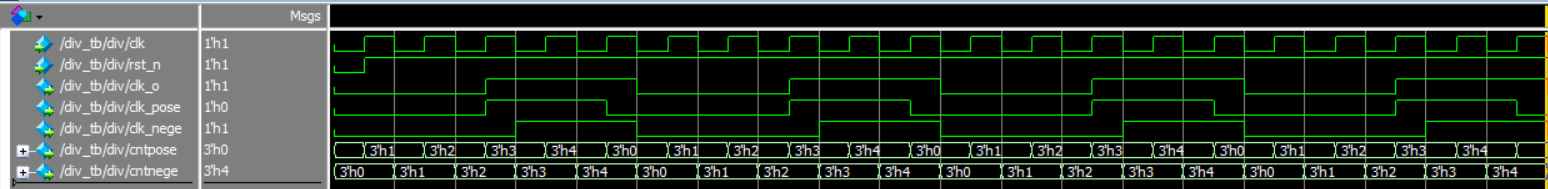

在Verilog中,偶数频分频较容易实现,只需要设定一个计数器,计数器值为分频数的一半,当计数记满后,输出信号取非,计数值清零。但这样并不能奇数分频,因为奇数分频数的一半包含0.5,无法只通过上升沿得到。但是设置两个不同的偶数分频时钟,通过上升沿和下降沿一同触发的模式,可以实现奇数分频。

在下面的代码中,需要修改div1,div2两个参数的值以实现分频,div1为分频数除以二的商,div2为余数。

module divfreq(clk, clk_o, rst_n, clk_pose, clk_nege, cntpose, coutnege);

input clk;

input rst_n;

output clk_o;

output clk_pose;

output clk_nege;

output [2:0] cntpose;

output [2:0] cntnege;

reg clk_pose;

reg clk_nege;

reg [2:0] cntpose;

reg [2:0] cntnege;

parameter div1 = 2, div2 = 4; //div1 = 5/2, div2 = 5-1

assign clk_o = clk_pose | clk_nege;

always@(posedge clk or negedge rst_n)

begin

if(rst_n)

clk_pose = 0;

else if(cntpose == div1)

clk_pose = ~clk_pose;

else if(cntpose == div2)

clk_pose = ~clk_pose;

else

clk_pose = clk_pose;

end

always@(negedge clk or negedge rst_n)

begin

if(rst_n)

clk_nege = 0;

else if(cntnege == div1)

clk_nege = ~clk_nege;

else if(cntnege == div2)

clk_nege = ~clk_nege;

else

clk_nege = clk_nege;

end

always@(posedge clk or negedge rst_n)

begin

if(rst_n)

cntpose = 0;

else if(cntpose == div2)

cntpose = 0;

else

cntpose = cntpose + 1;

end

always@(negedge clk or negedge rst_n)

begin

if(rst_n)

cntnege = 0;

else if(cntnege == div2)

cntnege = 0;

else

cntnege = cntnege + 1;

end

endmodule

上述方法是通过时钟或实现分频,另外,可以通过时钟与和时钟异或实现奇数分频。

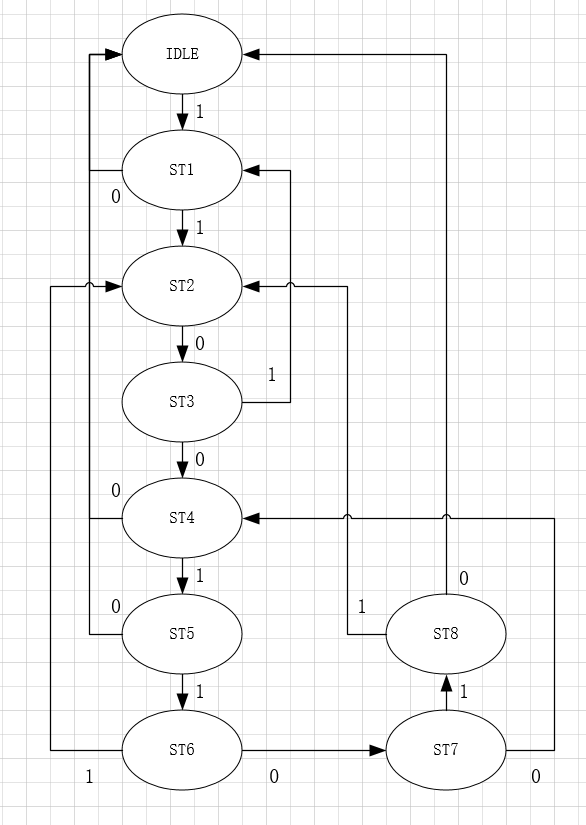

序列检测器

用状态机检测序列为 11001101,输出为 1,否则输出为 0。

序列检测器实质上为一个状态机。序列检测器的难点在于对序列重叠的处理。

module Detector(clk, rst_n, din, dout);

input clk, rst_n;

input din;

output dout;

parameter IDLE=0;

parameter ST1=1;

parameter ST2=2;

parameter ST3=3;

parameter ST4=4;

parameter ST5=5;

parameter ST6=6;

parameter ST7=7;

parameter ST8=8;

reg [3:0] current_state, next_state;

reg dout;

always @ (posedge clk or negedge rst_n)

if(!rst_n)

current_state <= IDLE;

else

current_state <= next_state;

always @ (next_state or current_state or din or dout)

begin

case(current_state)

IDLE: if(din) next_state = ST1; else next_state = IDLE;

ST1: if(din) next_state = ST2; else next_state = IDLE;

ST2: if(!din) next_state = ST3; else next_state = ST2;

ST3: if(!din) next_state = ST4; else next_state = ST1;

ST4: if(din) next_state = ST5; else next_state = IDLE;

ST5: if(din) next_state = ST6; else next_state = IDLE;

ST6: if(!din) next_state = ST7; else next_state = ST2;

ST7: if(din) next_state = ST8; else next_state = ST4;

ST8: if(din) next_state = ST2; else next_state = IDLE;

default: next_state = IDLE;

end

always @ (posedge clk)

if(next_state = ST8)

dout <= 1'b1;

else

dout <= 1'b0;

endmodule

最后

以上就是舒服河马最近收集整理的关于两道典型的Verilog面试题奇数分频器序列检测器的全部内容,更多相关两道典型内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复