✅作者简介:大家好我是:嵌入式基地,是一名嵌入式工程师,希望一起努力,一起进步!

????个人主页:嵌入式基地

????系列专栏:FPGA Verilog 习题专栏

????网上关于嵌入式的面试练习网站很少,这里给大家推荐一款Verilog 在线刷题神器,从基础到大厂面试题????点击跳转刷题网站进行注册学习

微信公众号:嵌入式基地

FPGA硬件工程师Verilog面试题(一)

- 习题一:四选一多路器

- 习题二:异步复位的串联T触发器

- 习题三:奇偶校验

- 习题四:移位运算与乘法

- 习题五:位拆分与运算

- 结束语

习题一:四选一多路器

- 点击进行在线练习

描述 - 制作一个四选一的多路选择器,要求输出定义上为线网类型

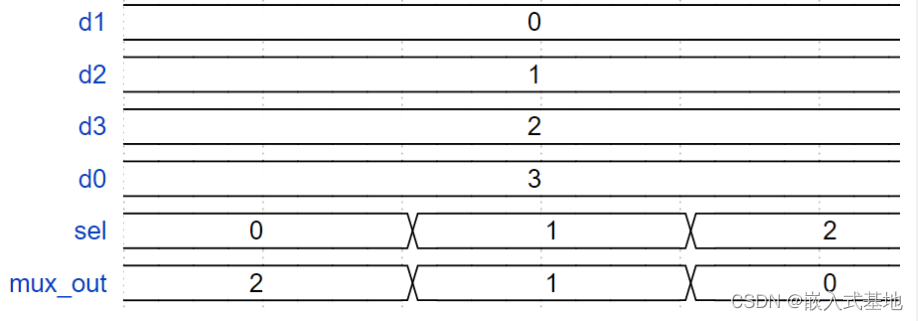

状态转换:

d0 11

d1 10

d2 01

d3 00

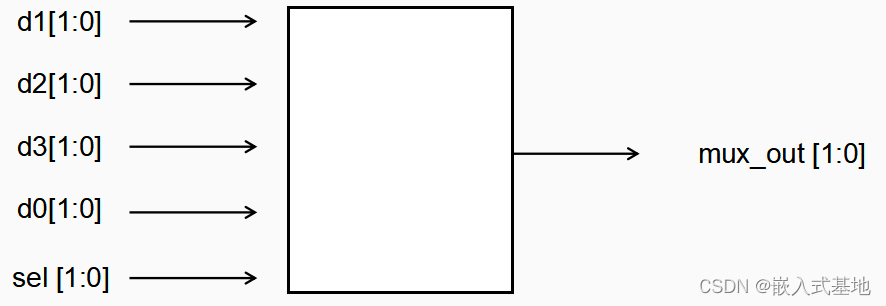

- 信号示意图:

- 波形示意图:

输入描述

- 输入信号 d1,d2,d3,d4 sel

- 类型 wire

输出描述

- 输出信号 mux_out

- 类型 wire

代码实现

`timescale 1ns/1ns

module mux4_1(

input [1:0]d1,d2,d3,d0,

input [1:0]sel,

output[1:0]mux_out

);

assign mux_out = sel[0]?(sel[1]?d0:d2):(sel[1]?d1:d3);

endmodule

习题二:异步复位的串联T触发器

-

点击进行在线练习

描述 -

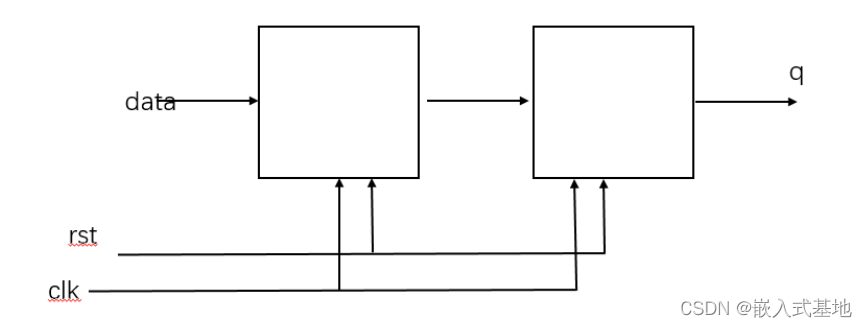

用verilog实现两个串联的异步复位的T触发器的逻辑,结构如图:

-

信号示意图:

-

-

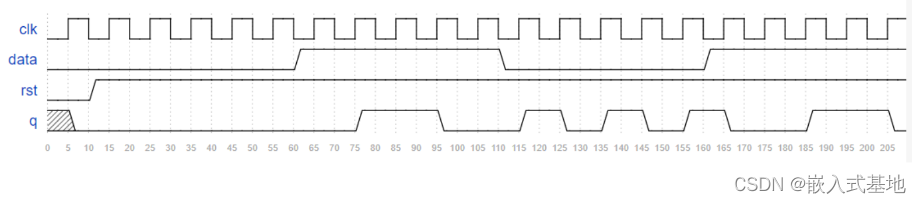

波形示意图:

-

输入描述

- 输入信号 data, clk, rst

- 类型 wire

- 在testbench中,clk为周期5ns的时钟,rst为低电平复位

输出描述

- 输出信号 q

- 类型 reg

代码实现

`timescale 1ns/1ns

module Tff_2 (

input wire data, clk, rst,

output reg q

);

reg q1;

always @ ( posedge clk or negedge rst)

if (~rst) begin

q1 <= 1'b0;

q <= 1'b0;

end

else begin

if (data) begin

q1 <= !q1;

end

if (q1) begin

q <= !q;

end

end

endmodule

习题三:奇偶校验

-

点击进行在线练习

描述 -

现在需要对输入的32位数据进行奇偶校验,根据sel输出校验结果(1输出奇校验,0输出偶校验)

-

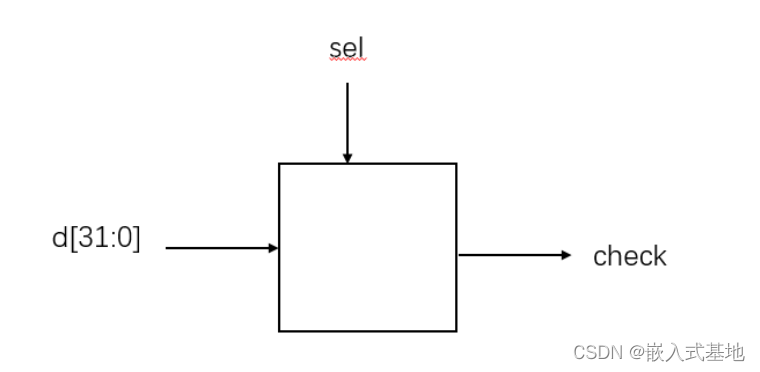

信号示意图:

-

-

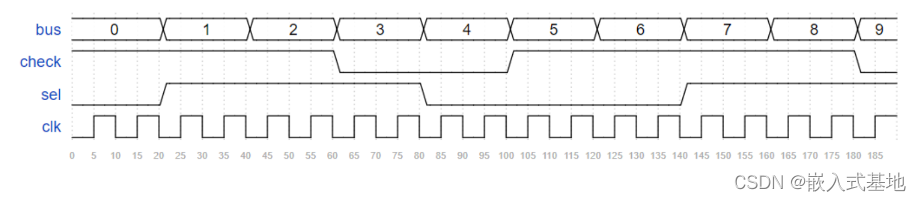

波形示意图:

-

输入描述

- 输入信号 bus sel

- 类型 wire

输出描述

- 输出信号 check

- 类型 wire

代码实现

`timescale 1ns/1ns

module odd_sel(

input [31:0] bus,

input sel,

output check

);

wire odd;

assign odd = ^bus;

assign check = sel?odd:~odd;

endmodule

习题四:移位运算与乘法

-

点击进行在线练习

描述 -

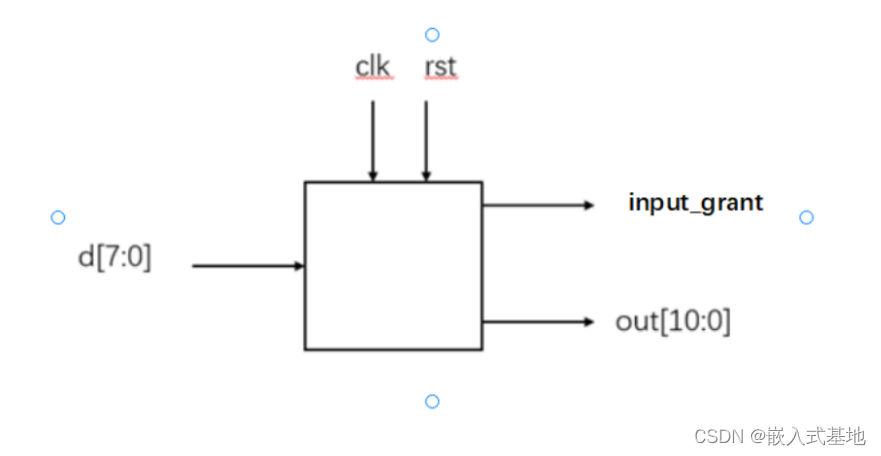

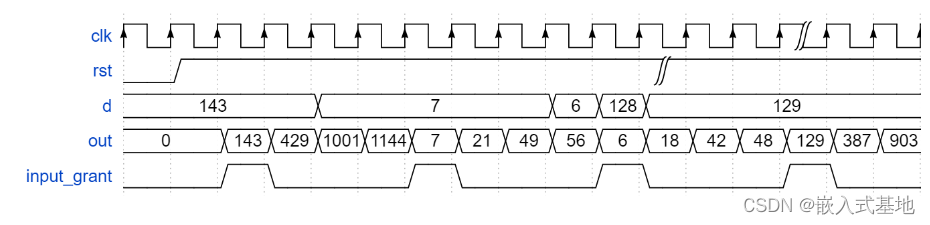

已知d为一个8位数,请在每个时钟周期分别输出该数乘1/3/7/8,并输出一个信号通知此时刻输入的d有效(d给出的信号的上升沿表示写入有效)

-

信号示意图:

-

-

波形示意图:

-

输入描述

- 输入信号 d, clk, rst

- 类型 wire

- 在testbench中,clk为周期5ns的时钟,rst为低电平复位

输出描述

- 输出信号 input_grant out

- 类型 reg

代码实现

`timescale 1ns/1ns

module multi_sel(

input [7:0]d ,

input clk,

input rst,

output reg input_grant,

output reg [10:0]out

);

reg [1:0]cnt;

reg [7:0]din;

always@(posedge clk or negedge rst) begin

if(!rst) begin

cnt <= 0;

out <= 0;

input_grant <= 0;

din <= 0;

end

else begin

cnt <= cnt+1;

case (cnt)

0: begin

din <= d;

input_grant <= 1;

out <= d;

end

1: begin

input_grant <= 0;

out <= (din<<2)-din;

end

2: begin

input_grant <= 0;

out <= (din<<3)-din;

end

3: begin

input_grant <= 0;

out <= (din<<3);

end

endcase

end

end

endmodule

习题五:位拆分与运算

- 点击进行在线练习

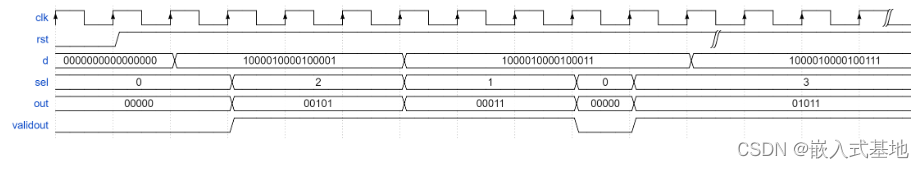

描述

现在输入了一个压缩的16位数据,其实际上包含了四个数据[3:0][7:4][11:8][15:12],

现在请按照sel选择输出四个数据的相加结果,并输出valid_out信号(在不输出时候拉低)

0: 不输出且只有此时的输入有效

1:输出[3:0]+[7:4]

2:输出[3:0]+[11:8]

3:输出[3:0]+[15:12]

-

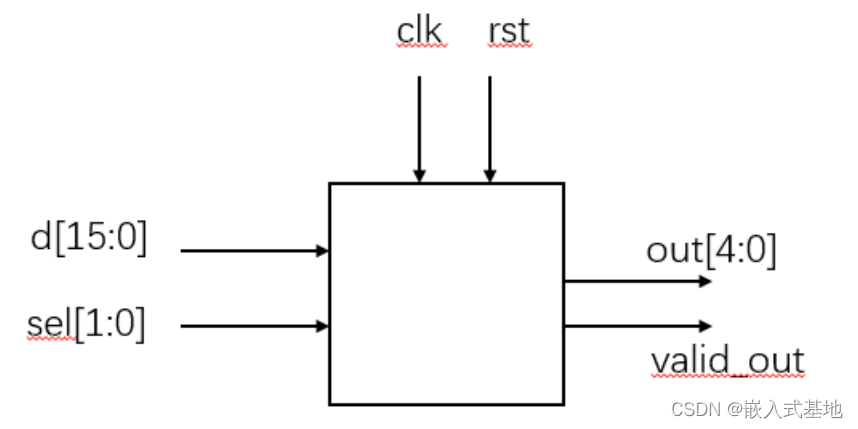

信号示意图:

-

-

波形示意图:

-

输入描述

- 输入信号 d, clk, rst

- 类型 wire

- 在testbench中,clk为周期5ns的时钟,rst为低电平复位

输出描述

- 输出信号 validout out

- 类型 reg

代码实现

`timescale 1ns/1ns

module data_cal(

input clk,

input rst,

input [15:0]d,

input [1:0]sel,

output reg[4:0]out,

output reg validout

);

reg [15:0]data_lock;

always@(posedge clk or negedge rst) begin

if (!rst)

data_lock <= 0;

else if(!sel)

data_lock <= d;

end

always@(posedge clk or negedge rst) begin

if (!rst) begin

out <= 'b0;

validout <=0;

end

else begin

case(sel)

0:begin

out <= 'b0;

validout <=0;

end

1:begin

out <= data_lock[3:0]+data_lock[7:4];

validout <=1;

end

2:begin

out <= data_lock[3:0]+data_lock[11:8];

validout <=1;

end

3:begin

out <= data_lock[3:0]+data_lock[15:12];

validout <=1;

end

endcase

end

end

endmodule

结束语

你想要的牛客都有,各种大厂面试真题在等你哦!快快通过下方链接注册加入刷题大军吧!

????刷题神器,从基础到大厂面试题????点击跳转刷题网站

最后

以上就是温婉茉莉最近收集整理的关于FPGA硬件工程师Verilog面试题(基础篇一)习题一:四选一多路器习题二:异步复位的串联T触发器习题三:奇偶校验习题四:移位运算与乘法习题五:位拆分与运算结束语的全部内容,更多相关FPGA硬件工程师Verilog面试题(基础篇一)习题一:四选一多路器习题二:异步复位内容请搜索靠谱客的其他文章。

发表评论 取消回复