本篇文章介绍一下在数电中经常使用到得各种分频模式。

这里写目录标题

- 偶数分频

- 奇数分频

- 半整数分频

偶数分频

奇数分频

半整数分频

偶数分频

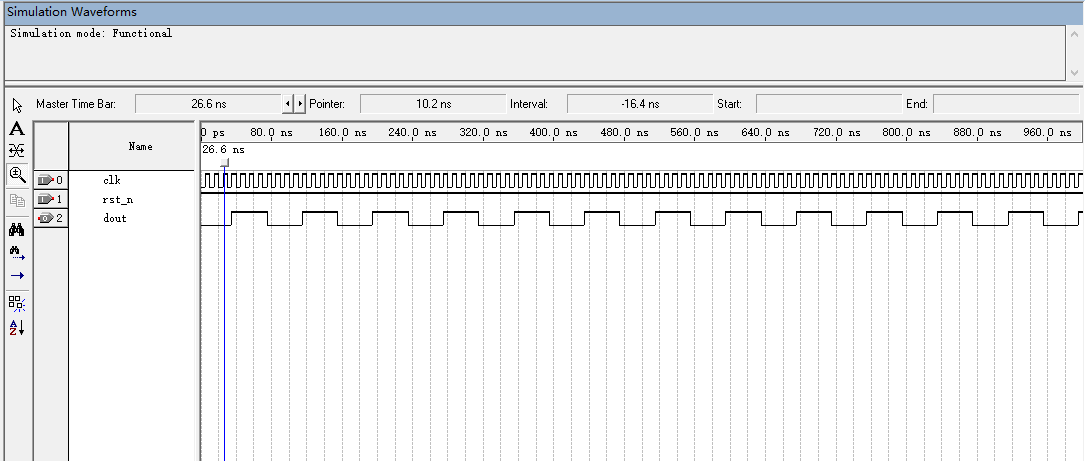

最简单二分频,在输入时钟上升沿翻转即可。N分频(N为偶数),计数器计数到N/2-1翻转。如进行4分频,count=4/2-1=1时翻转,对计数器一般然后进行信号翻转即可。程序如下,经过实测验证,正确。

下面展示一些 偶数分频。

// An highlighted block

module test1(

clk ,

rst_n ,

//其他信号,举例dout

// N ,

dout

);

//参数定义

parameter DATA_W = 1;

//输入信号定义

input clk ;

input rst_n ;

// input N ;

//输出信号定义

output dout ;

//输出信号reg定义

reg dout ;

reg div_clk1;

reg div_clk2;

//中间信号定义 4分频

reg [3:0] cnt ;

wire add_cnt;

wire end_cnt;

reg [3:0] cnt1 ;

wire add_cnt1;

wire end_cnt1;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt <= 0;

end

else if(add_cnt)begin

if(end_cnt)

cnt <= 0;

else

cnt <= cnt + 1;

end

end

assign add_cnt = 1;

assign end_cnt = add_cnt && cnt==4-1 ; //3

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

dout <= 0;

end

else if(end_cnt)begin

dout <= ~dout;

end

else begin

dout <= dout;

end

end

// assign dout = div_clk1 | div_clk2;

endmodule

上图中所展示的为8分频

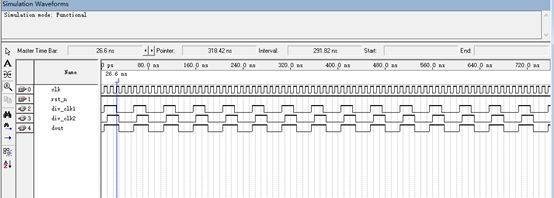

下面展示一些 奇数分频。

// An highlighted block

module test1(

clk ,

rst_n ,

//其他信号,举例dout

// N ,

dout

);

//参数定义

parameter DATA_W = 1;

//输入信号定义

input clk ;

input rst_n ;

// input N ;

//输出信号定义

output dout ;

//输出信号reg定义

wire dout ;

reg div_clk1;

reg div_clk2;

//中间信号定义

reg [3:0] cnt ;

wire add_cnt;

wire end_cnt;

reg [3:0] cnt1 ;

wire add_cnt1;

wire end_cnt1;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt <= 0;

end

else if(add_cnt)begin

if(end_cnt)

cnt <= 0;

else

cnt <= cnt + 1;

end

end

assign add_cnt = 1;

assign end_cnt = add_cnt && cnt==5-1 ; //3

always @(negedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt1 <= 0;

end

else if(add_cnt1)begin

if(end_cnt1)

cnt1 <= 0;

else

cnt1 <= cnt1 + 1;

end

end

assign add_cnt1 = 1;

assign end_cnt1 = add_cnt1 && cnt1==5-1 ; //3

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

div_clk1 <= 0;

end

else if((cnt == 0) || (cnt == 2))begin

div_clk1 <= ~div_clk1;

end

else begin

div_clk1 <= div_clk1;

end

end

always @(negedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

div_clk2 <= 0;

end

else if((cnt1 == 0) || (cnt1 == 2))begin

div_clk2 <= ~div_clk2;

end

else begin

div_clk2 <= div_clk2;

end

end

assign dout = div_clk1 | div_clk2;

endmodule;

在修改分频的数值时候可以直接修改2哥计数器的计数值即可。

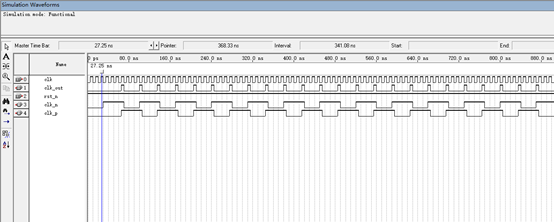

下面展示一些 半整数分频。

// An highlighted block

module half(

clk ,

rst_n ,

clk_out

);

//参数定义

parameter N = 3;

//输入信号定义

input clk ;

input rst_n ;

//输出信号定义

output clk_out ;

//输出信号reg定义

wire clk_out ;

reg [31:0] cnt1 ;

reg clk_p ;

reg clk_n ;

//中间信号定义

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

cnt1 <= 0;

end

else if(cnt1 == 2* N)begin

cnt1 <= 0;

end

else begin

cnt1 <=cnt1 + 1;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

clk_p <= 0;

end

else if(cnt1 == 2*N )begin

clk_p <= 1;

end

else if(cnt1 == N)begin

clk_p <= 0;

end

end

always @(negedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

clk_n <= 0;

end

else if(cnt1 == 0 )begin

clk_n <= 0;

end

else if(cnt1 == N)begin

clk_n <= 1;

end

end

assign clk_out = clk_p & clk_n;

endmodule

最后

以上就是大方花瓣最近收集整理的关于一文搞定面试笔试中(Verilog)的所有分频器偶数分频奇数分频半整数分频的全部内容,更多相关一文搞定面试笔试中(Verilog)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复