文章目录

- 提高工作频率的本质

- 电路延迟

- 常用技术

- 降低功耗

- 题目

提高工作频率的本质

提高工作频率的本质就是减少寄存器到寄存器的时延,简言之,降低各种延时

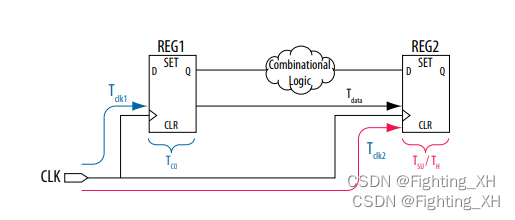

电路延迟

-

电路延迟主要包括三个:

寄存器延迟Tco(时延是由器件物理特性决定)、走线延迟和组合逻辑延迟。 -

走线延迟:

1、加入时钟约束(一般以加5%裕量较为合适)

2、将相关的逻辑的布线时尽量靠近,从而减少走线时延。 -

组合逻辑延迟:

1、切割组合逻辑,减少LUT级联,当输出判断条件大于四个输入的话,一般采用多LUT级联的方式,那么就会引入更多的延迟,因此我们要尽可能减少输入条件,从而级联LUT也减少。切割组合逻辑常采用流水线技术,通过各级之间插入寄存器来实现,从而各级之间的组合逻辑减少。

2、将计数器移除FSM。当我们在进行状态机设计的时候,有时也会将计数器作为判断条件,但是输入常为四输入,而计数器数值较大,比如111100,那么就需要LUT级联,所以我们这里将计数器写到状态机外。

3、当状态机中有几十个状态的时候,也可以切割,在某状态又可跳转到一个新的小状态机。

总结: 提高时钟频率最有效的方法是避免出现大的组合逻辑(尽量去满足四输入的条件,减少LUT级联数量)。

常用技术

通过加约束、流水线技术、切割状态的方法提高工作频率。

降低功耗

了解各种功耗

低功耗,简单来说——减少0和1的翻转。

题目

题目1:

下面哪些措施对提高设计的频率有帮助( AD )。

A 组合逻辑拆分 B 减少不必要的寄存器复位

C ram/fifo输出寄存 D减少信号扇出数

分析:组合逻辑拆分和减少信号扇出数可降低组合逻辑延时。

扇出:FPGA里面,扇出是一个输出端连接/驱动的后级资源的个数,比如驱动10个LUT查找表;

题目2:

关于时序逻辑电路Pipeline设计(流水线设计)说法正确是( ACD )?

A.Pipeline可以提高吞吐率

B.Pipeline可以降低单个任务的latency

C.Pipeline可以提高时钟频率

D.Pipeline需要对流水线进行切割,设计时要对流水线进行均衡,以保证时序的接近

题目3:

下面降低功耗的方法中,属于降低静态功耗的有 ABE

A:门级电路的功耗优化

B:多阈值电压

C:门控时钟电路

D:操作数分离

E:多个供电电压

CMOS管功耗 = 动态功耗 + 静态功耗 静态功耗:是时钟不工作的状态下所需的功耗

题目4:

题目1:下列功耗措施哪个可以降低峰值功耗? ——A

A 静态模块级Clock Gating

B Memory Shut Down

C Power Gating

D 大幅度提高HVT比例

A:由于峰值损耗一般出现在时钟翻转的瞬间,而A选项是加入时钟门控,当我们不需要时钟翻转时可将其关闭。

B:存储关闭,当不被访问的时候,关闭存储器,属于降低静态功耗。

C:电源门控,即模块不工作的时候,关闭电源,模块睡眠,工作时候再启动电源,也属于降低静态功耗。

D:采用高阈值电压的晶体管,阈值电压增加的效果在于降低亚阈值漏电电流,属于降低静态功耗。

该题有争议,从两个角度来看答案不同,我认为A正确,这里暂选择A。

题目5:

以下哪些手段可以降低SRAM的动态功耗( BC)。(大疆FPGA逻辑岗B卷)(多选)

A 不访问SRAM时,关闭时钟

B 不访问SRAM时,地址线不翻转

C 不访问SRAM时,写数据线不翻转

D 不访问SRAM时,将其Power down

D:首先对于SRAM来说,它属于静态随机存取存储器,静态是指只要通电,数据即可保持,当断电的时候,数据丢失。因此D选项不能作为降低损耗的方法。

.

A:影响动态功耗的主要变量是电容充电、工作电压和时钟频率。因此在SRAM不工作时,关闭控制SRAM的时钟,SDRAM中的数据并不会丢失,而且可以降低动态损耗。

.

BC:不访问SRAM时,地址线和写数据线不翻转,相当于减少了CMOS管的翻转,因此能降低动态损耗。

题目6:

对于90nm制程芯片,合法的电压,环境温度范围内,以下哪种情况内部信号速度最快:B

A:温度低,电压低

B:温度低,电压高 (CPU 液氮 加压 可以实现超频)

C:温度高,电压低

D:温度高,电压高

题目7:

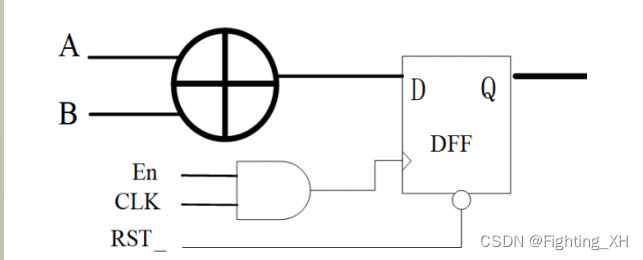

解释什么叫clock gating?并说明一下通常情况下为什么要做clock gating?简单列举通常实现的方法有哪些?

首先掌握降低功耗的知识。

clock gating:时钟门控,它是一种简单且有效的降低功耗的方法。

.

时钟门控的好处:时钟门控通过组合逻辑门来生成时钟,从而可以实现开关性,因此就可将暂时用不到的时钟关闭,避免无用时钟翻转带来的功耗。,从而起到降低功耗的作用。

.

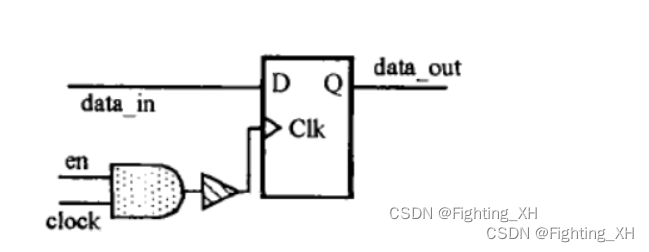

实现方法:设置一个en信号,让clock和en信号与运算。

题目8:

关于流水线设计的理解,错误的是:A

A. 流水线设计会消耗较多的组合逻辑资源.

B. 流水线设计会导致原有通路延时增加.

C. 流水线设计的思想,是使用面积换取速度.

D. 关键路径中插入流水线,能够提高系统时钟频率.

解析:流水线技术通过插入寄存器来分割大的组合逻辑,因此会消耗更多的时序逻辑资源,理论上组合逻辑资源不变;由于插入了寄存器,且每增加一级寄存器就会对数据寄存一个时钟周期,所以原有通路延时增加。

题目9:

对芯片静态功耗影响最大的是哪一项 D

A. 工作模式. B. 频率. C. 负载. D. 电压.

题目10:

在不增加pipeline的情况下,如何解决一条critical path的setup时序不满足的问题

A. 使用更先进工艺的工艺库.

B. 在这条path上插入寄存器.

C. 将部分组合逻辑电路搬移到前级path上.

D. 降低时钟频率.

解析:B是流水线技术

题目11:

下列优化方法中那些是速度优化方法: BC

A. 资源共享. B. 关键路径优化. C. 流水线. D. 串行化.

题目12:[NVIDIA]

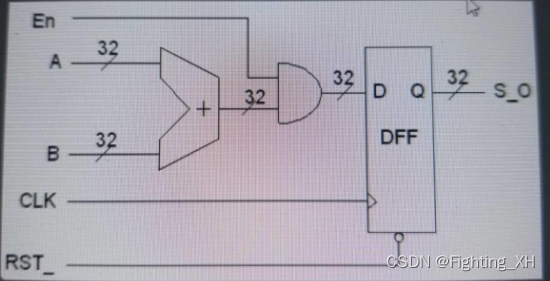

请为下面电路降低功耗:

解题:

首先功耗主要是高低电平翻转引起的,该题考察时钟信号翻转造成的功耗,我们常用时钟门控的方式来解决。

时钟门控:采用组合逻辑,来控制时钟,从而不使用时钟的时候可关断。

下图可看到,加入en信号进行与操作,我们即可根据en信号来控制时钟信号。

题目13:

Which of the following items can help reduce test time(AB)

A. Increase Operation Voltage.

B. Increase scan shift clock frequency.

C. Utilize more scan IOs.

D. Insert gating logic.

解析:增大电压能缩短延时,提高时钟频率,可降低工作时间。扇出越多延时越大,组合逻辑越多延时越大。

题目14:

电子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化)以及提高运行速度(即速度优化) ,下列方法 ( A)不属于面积优化。

A、流水线设计——牺牲面积换速度

B、资源共享

C、逻辑优化

D、串行化

题目15:

[多选题]超大规模集成电路设计中,为了高速设计,采取以下哪些措施(AB)

A.流水线设计

B.并行化设计

C.资源共享

D.串行化设计

题目16:

[多选题]低功耗电路实现的方法有(AC)

A.降低工作电压

B.增加负载电容

C.降低电路面积

D.尽可能提高电路性能

题目17:

说出面积和速度优化的方法

面积优化:资源共享,逻辑复制,串行化;

速度优化:流水线,关键路径法,寄存器配平;

题目18:

Cell Delay can be calculated based on:( AD)

A. input transition. B. input load. C. output transition. D. output load.

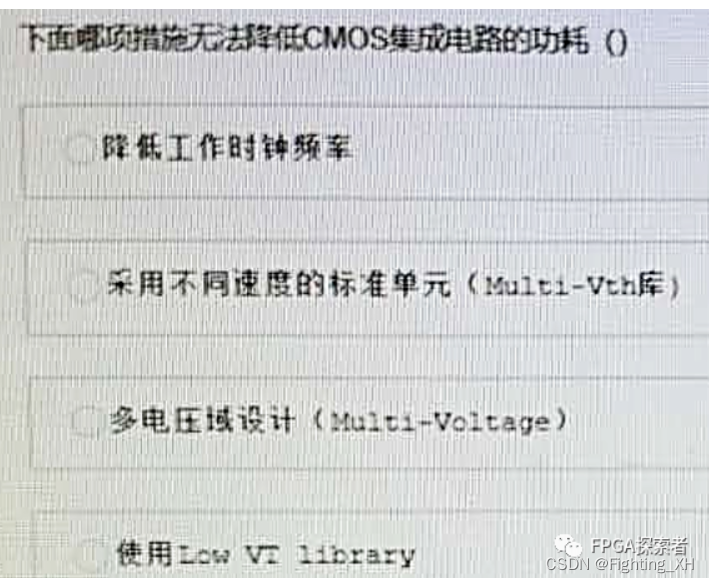

题目19:

D

CMOS集成电路低功耗:降频; 降压;多电压;多阈值;门控时钟;

D 中的 Low VT libaray,低阈值库,漏电流大,运算速度快,静态功耗大

最后

以上就是阔达蜜蜂最近收集整理的关于FPGA设计中提高工作频率及降低功耗题目合集提高工作频率的本质电路延迟常用技术降低功耗题目的全部内容,更多相关FPGA设计中提高工作频率及降低功耗题目合集提高工作频率内容请搜索靠谱客的其他文章。

发表评论 取消回复