题目描述:

用VHDL语言设计一个同步复位、置位的D触发器

原理:D触发器是能够存储1位二进制码的逻辑电路,它有两个互补输出端,其输出状态不仅与输入有关,而且还与原先的输出状态有关。触发器有两个稳定状态,用以表示逻辑状态“1”和“0”。在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存储器件,是构成各种时序电路的最基本逻辑单元。

VHDL源代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity trigger_d is

port(clk,d,sreset,sset:in std_logic;

q,qb:out std_logic);

end entity;

architecture art of trigger_d is

begin

process(clk,d,sreset,sset)

begin

if clk'event and clk='1' then

if sreset='1' then q<='0';qb<='1';

elsif sset='1' then q<='1';qb<='0';

else q<=d;qb<=not(d);

end if;

end if;

end process;

end architecture art;

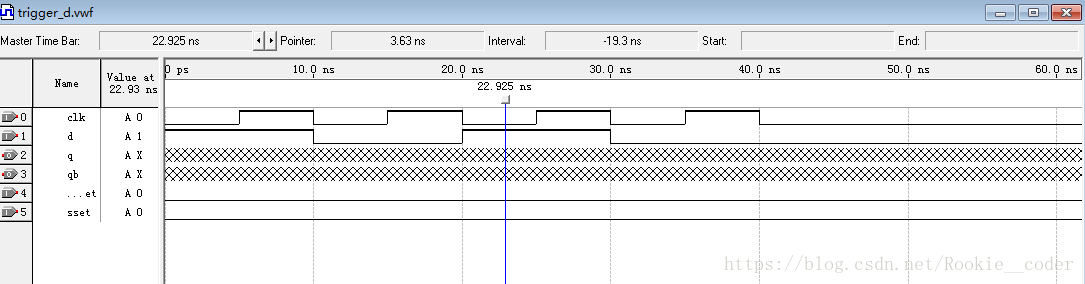

波形图如下:

原始波形图

原始波形图

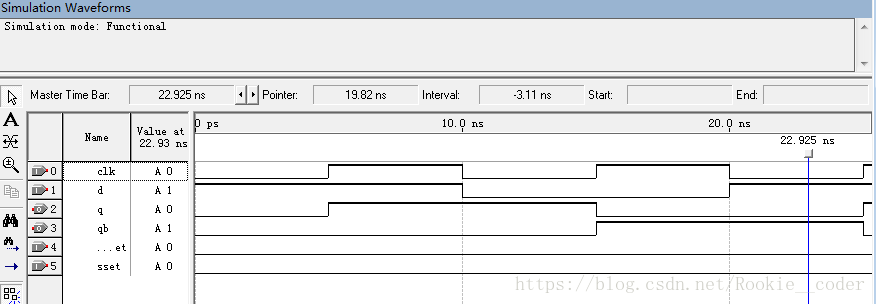

功能仿真图

功能仿真图

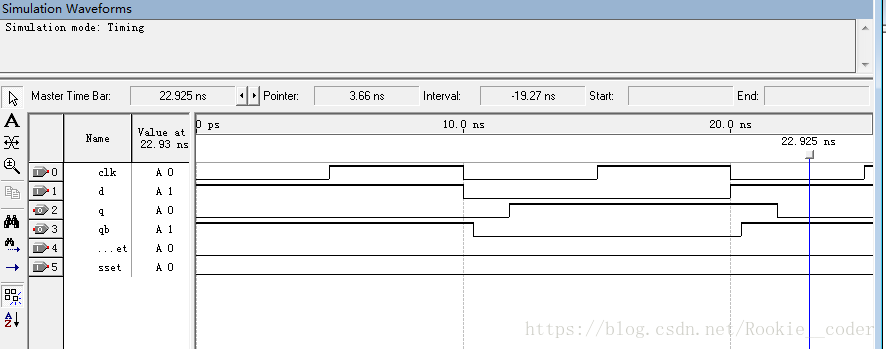

时序仿真图

时序仿真图

最后

以上就是甜甜铃铛最近收集整理的关于【VHDL】同步复位、置位的D触发器设计的全部内容,更多相关【VHDL】同步复位、置位内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复