文章目录

- 1. 异步复位

- 2. 同步复位

- 3. 异步复位同步释放

今天好好理一理异步复位,同步复位,以及亚稳态中的异步复位同步释放。

1. 异步复位

一般让复位信号低电平有效

复位信号不受时钟的控制,只要复位信号有效,那么电路就会复位。对应的写法为:

always @ (posedge clk or negedge rst_n) begin

if (!rst_n)

xxxx;

else if (xx) begin

xxxx;

xxxx;

end

end

注意,在此always块中,敏感量为两个,一个是clk的上升沿(posedge clk),一个是复位信号rst_n的下降沿(negedge rst_n),当复位信号下降沿出现时,不论clk在什么状态,都执行always块,即复位!

2. 同步复位

同步复位,即如果复位信号有效,则只能在时钟上升沿让电路复位。对应写法为:

always @ (posedge clk) begin

if (!rst_n)

xxxx;

end

注意,在此always块中,敏感量只有一个,即clk的上升沿,此含义是,只有在clk的上升沿才能执行always块,否则不执行。于是如果复位信号有效,也只能等到clk上升沿才能执行always块,才能使电路复位!

3. 异步复位同步释放

什么同步释放不同步释放之类的,说得那么高大上的,搞得云里雾里的,其实也下面一行字就能解释清楚:

为了避免亚稳态,让拉高的复位信号打两拍,达到与时钟clk边沿同步的目的

注意,是时钟边沿!!!边沿,边沿,边沿

以上就是同步释放,可见只是拉高的信号打两拍,拉低的信号,也就是复位信号有效的时候,该复位就复位,该干嘛干嘛,我们不用去管它。

以下是解释:

假设复位信号低电平有效rst_n,当复位信号无效时,也就是复位信号拉高时,即为复位信号的释放。

由于异步复位信号与时钟无必然联系,两者都是独立的,所以复位信号的拉高将有一定的概率导致电路出现亚稳态。

对于亚稳态的处理,通常是利用同步器进行同步,使其输出能够受到时钟clk的控制。也就是说,同步器的输出最终与时钟clk同步。另外,同步器的另一个口语化表达为:“打两拍”,通过两个D触发器,最终得到与时钟同步的信号。

至于为什么需要两个

D触发器而不是一个,请移步论文《异步复位设计中的亚稳态问题及其解决方案》,提取码ejjr

至于为什么需要两个D触发器而不是更多,是因为通过一系列的数学计算,发现如果有亚稳态的发生,且两个D触发器将此亚稳态传递到了主电路,大约需要100年的时间(具体时间我忘记了),在这么长时间内,使用者就真的不来一下复位操作吗?真就让程序一直跑下去吗?不可能吧,一个小游戏都需要停机维护,何况更加高大上的物件。所以说,两个已经够用了。

那么将异步的复位信号打两拍,不就能够解决亚稳态的问题了吗?换句话说,复位信号有效的时候,我们不去管任何东西,系统复位让它复位就好了;之后在复位信号拉高的时候可能导致亚稳态的出现,那直接将拉高的信号打两拍,不就完事了吗?就是这么简单。

经典的异步复位同步释放代码如下

module asyn_reset(

clk ,

rst_n ,

rst_s2

);

input clk ;

input rst_n ;

output reg rst_s2;

reg rst_s1;

always @ (posedge clk or negedge rst_n) begin

if (!rst_n) begin

rst_s1 <= 1'b0;

rst_s2 <= 1'b0;

end

else begin

rst_s1 <= 1'b1 ;

rst_s2 <= rst_s1 ;

end

end

endmodule

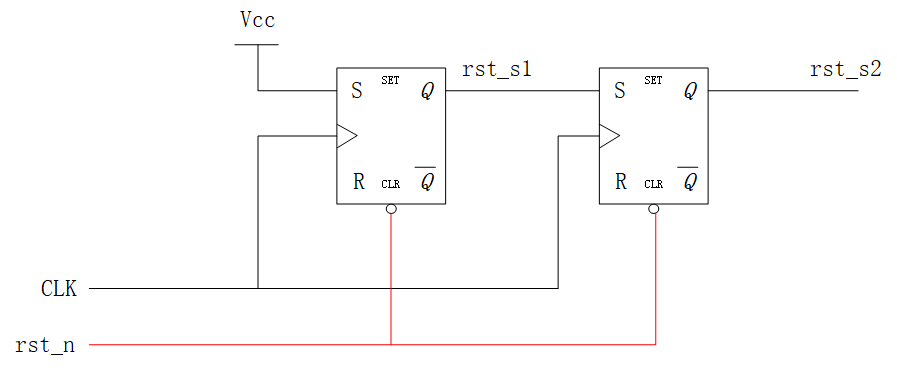

综合出的电路如下:

复位信号拉高,相当于rst_n对高电平进行采样;

由于异步复位需要在时钟上升沿进行释放,故在rst_n=1后,让信号rst_s1对电平1进行采样,之后再打一拍到寄存器rst_s2。相当于高电平被打了两拍才输出到rst_s2,达到了复位信号的释放与时钟clk同步的目的。

最后

以上就是腼腆短靴最近收集整理的关于关于“异步复位,同步复位,异步复位同步释放”的理解的全部内容,更多相关关于“异步复位,同步复位,异步复位同步释放”内容请搜索靠谱客的其他文章。

发表评论 取消回复