ModuleSim Verilog同步置数、同步清零的计数器实验

#全文复制可运行,经验证无错

你好! 这是你第一次使用 ModuleAim同步置数、同步清零的计数器实验

如果这是你第一次项目,推荐一个哔站10分钟的视频,手把手带你从建立到完成,看完后再复制我代码即可运行。

【【教学】modelsim独立仿真】 https://www.bilibili.com/video/BV1Eg4y1z7Hf?share_source=copy_web&vd_source=7ad1628d08bfd89388ae0ec2897cffc3

count.v文件

module count (out,data,load,rest,clk);

output[7:0]out;

input[7:0]data;//注意不能对输入进行赋值操作

input load,rest,clk;

reg[7:0]out;

always@(posedge clk)//clk上升沿触发

begin

if(!rest)out=8'h00;//h16进制,同步清零,低电平有效

/*当时钟是上升沿,且rest是低电平时,将out置零*/

else if(load)out=data;//同步预置

/*当时钟是上升沿,且rest是高电平,load是高电平,out=data*/

else out=out+1;//计数

end

endmodule

count_tb.vt文件

`timescale 1ns/1ns

module count_tb();

reg clk,rest,load;

reg [7:0] data;

wire [7:0] out;

count count_inst(.clk(clk),.rest(rest),.data(data),.out(out),.load(load));//?????

initial

begin

clk = 0;

rest = 0;

load = 0;

data = 2;//???????4

end

always #10 clk = ~clk;//?10ns????

always @(posedge clk)

begin

load = 1;

rest = 1;

end

always @(negedge clk)

begin

load = 0;

if(out==5)load=1;

end

endmodule

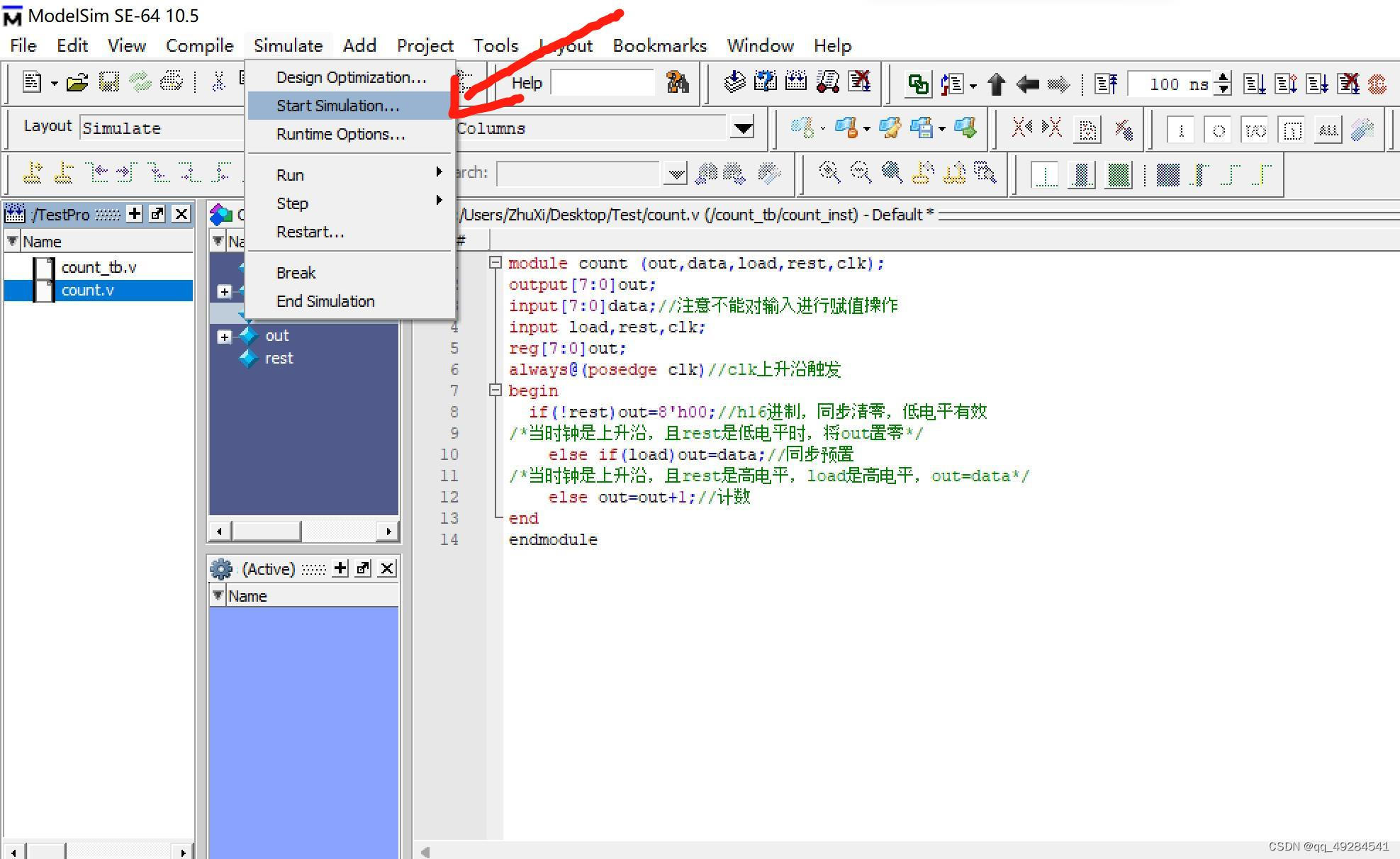

编译运行

1,找到文件

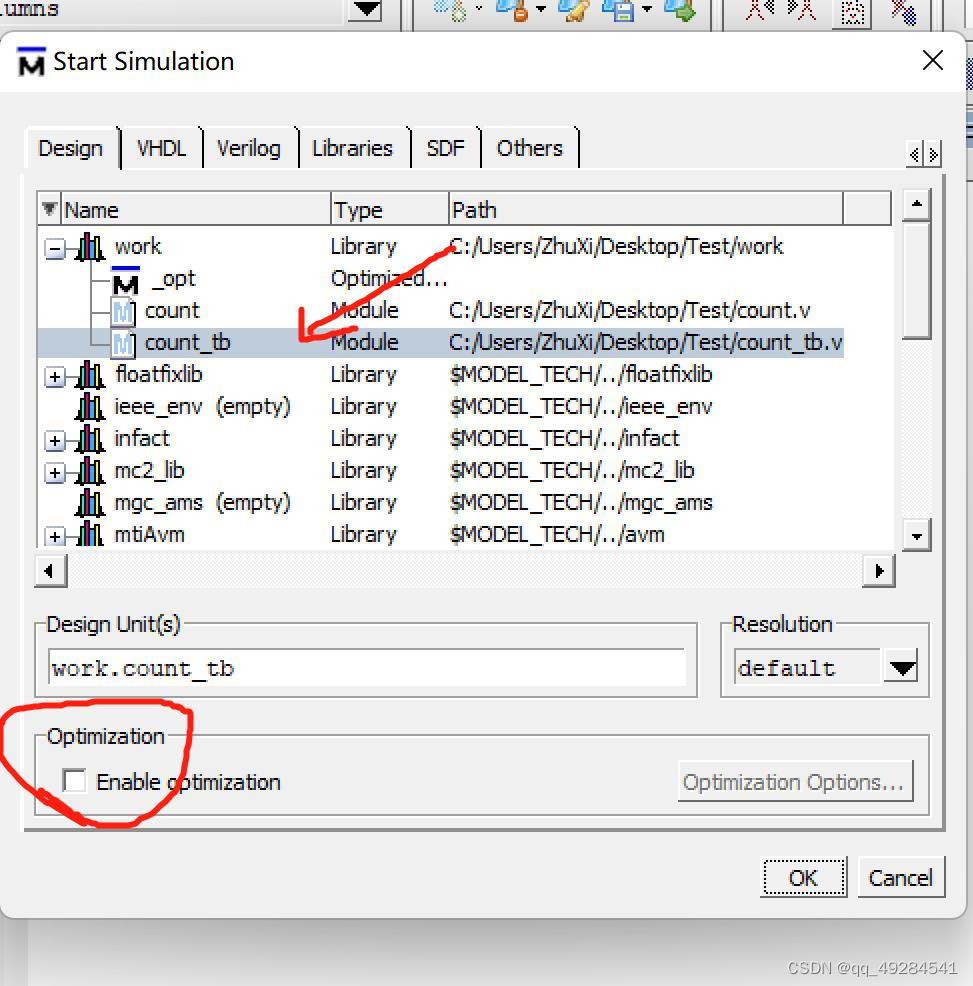

2,运行

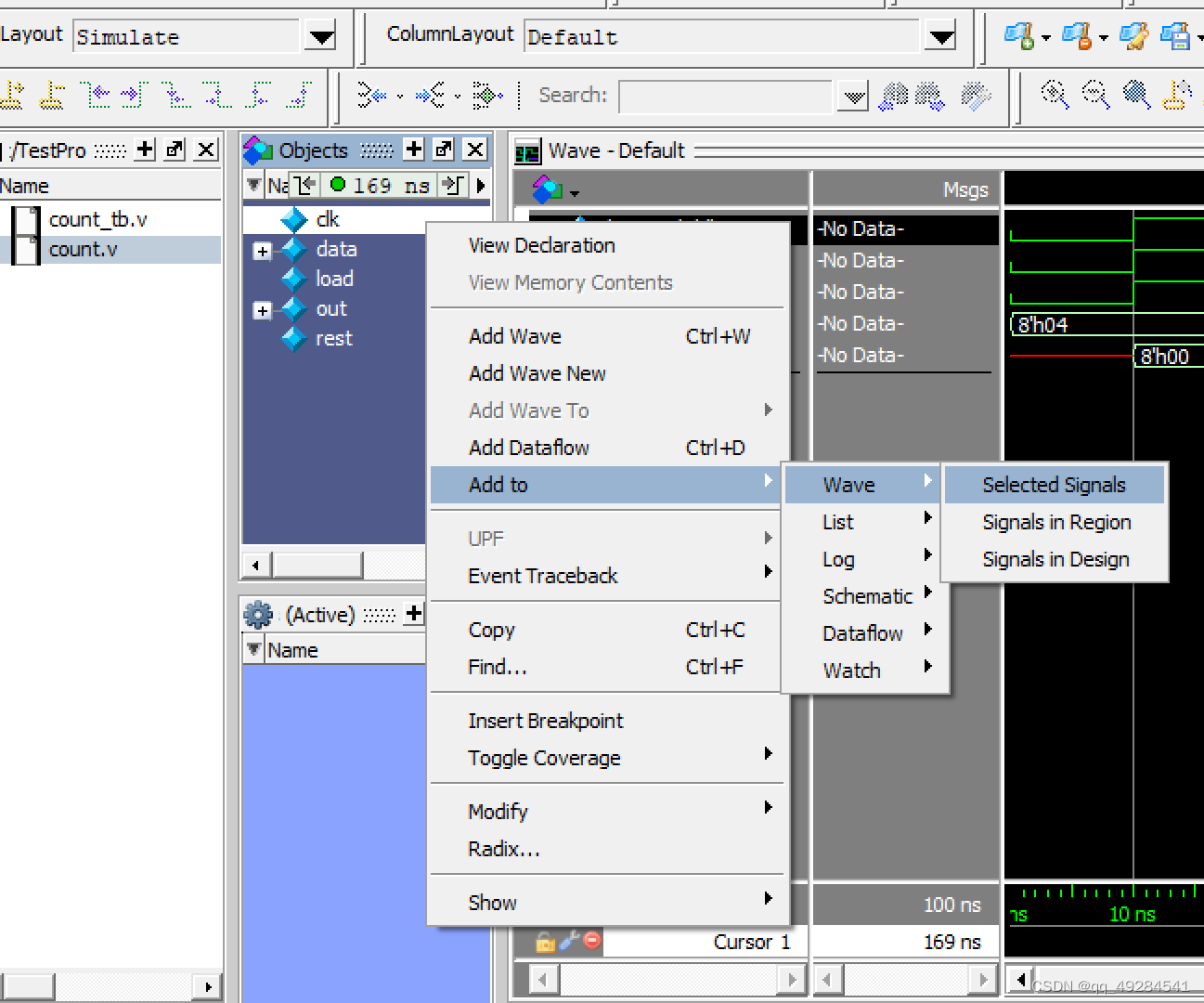

3,把每个信号加入到波形显示窗口

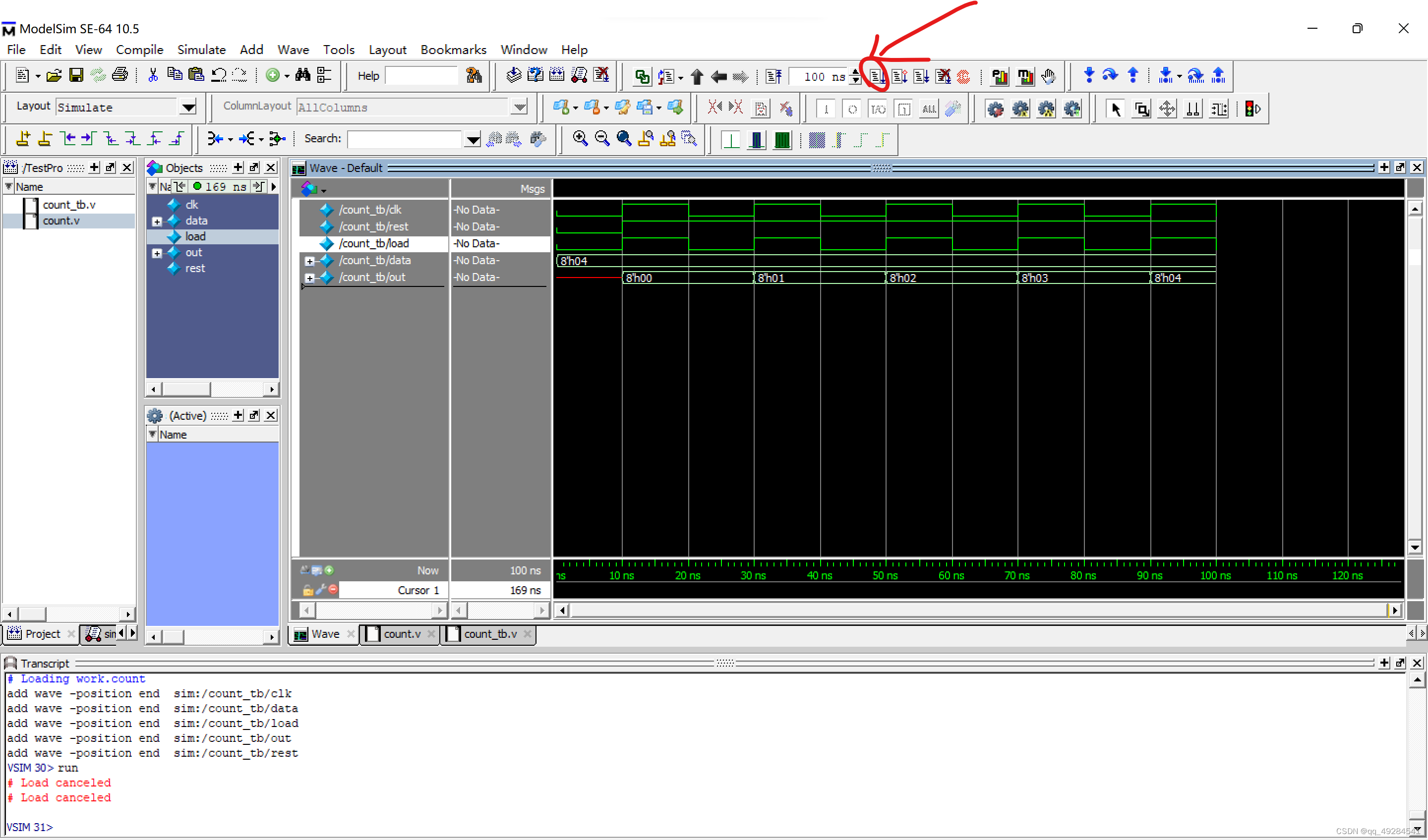

4,波形显示成功

最后

以上就是美丽小蘑菇最近收集整理的关于ModuleAim Verilog同步置数、同步清零的计数器实验的全部内容,更多相关ModuleAim内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复