同步:必须要等待时钟信号的有效沿(上升或下降)时,再判断复位(清零)信号是否有效,两个必须保持同步才能保证复位(清零)。

异步:不管时钟信号状态如何,只要复位(清零)信号为有效,立即复位(清零)。

在同步时PROCESS敏感列表中只需要有时钟信号即可,然而在异步时则需要加上复位信号。

详情可以见VHDL代码。

下面以一个简单的计数器 为例实现同步和异步的功能:

输入端:时钟信号(CLK),复位端;

输出端:输出信号;

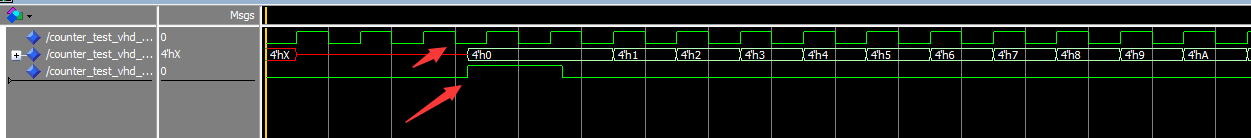

异步code:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_unsigned.ALL;

USE ieee.numeric_std.ALL;

ENTITY counter_test IS

PORT(

clk : IN std_logic;

Reset : IN std_logic;

Q : OUT std_logic_vector(3 downto 0)

);

END counter_test;

ARCHITECTURE TB OF counter_test IS

signal Q1 :std_logic_vector(3 downto 0);

BEGIN

process(clk,reset)

begin

if reset='1' then Q1<=(others=>'0');--复位为高电平有效

elsif clk'event and clk='1' then Q1<=Q1+1;

end if;

end process;

Q<=Q1;

END TB;

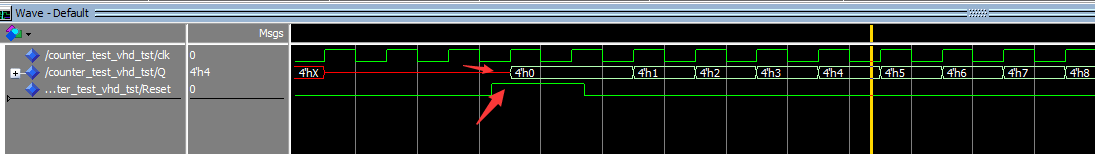

同步code:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_unsigned.ALL;

USE ieee.numeric_std.ALL;

ENTITY counter_test IS

PORT(

clk : IN std_logic;

Reset : IN std_logic;

Q : OUT std_logic_vector(3 downto 0)

);

END counter_test;

ARCHITECTURE TB OF counter_test IS

signal Q1 :std_logic_vector(3 downto 0);

BEGIN

process(clk,reset)

begin

if clk'event and clk='1' then

if reset='1' then Q1<=(others=>'0');--复位为高电平有效

else Q1<=Q1+1;

end if;

end if;

end process;

Q<=Q1;

END TB;

test bench:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

ENTITY counter_test_vhd_tst IS

END counter_test_vhd_tst;

ARCHITECTURE counter_test_arch OF counter_test_vhd_tst IS

SIGNAL clk : STD_LOGIC:='0';

SIGNAL Q : STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL Reset : STD_LOGIC:='0';

COMPONENT counter_test

PORT (

clk : IN STD_LOGIC;

Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

Reset : IN STD_LOGIC

);

END COMPONENT;

constant T: time := 10ns;

BEGIN

i1 : counter_test

PORT MAP (

clk => clk,

Q => Q,

Reset => Reset

);

clk_test : PROCESS

BEGIN

wait for T/2;

clk <= not clk;

END PROCESS clk_test;

rst_test : PROCESS

BEGIN

reset<='0';

wait for 32ns;

reset<='1';

wait for 15ns;

reset<='0';

wait for 45ns;

wait;

END PROCESS rst_test;

END counter_test_arch;

最后

以上就是受伤大侠最近收集整理的关于VHDL同步复位(清零)与异步复位(清零)的简易区分的全部内容,更多相关VHDL同步复位(清零)与异步复位(清零)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复