数电复试复习笔记

数制与码制

逻辑函数及其表示方法

由原码写出补码步骤

1、原码至反码:保持符号位不变,其它位取反;

2、反码至补码:将反码末位+1;

逻辑代数基础

逻辑代数基本定理

1、代入定理:以逻辑函数式代替项

2、反演定理又称摩根定理(求原函数反函数):连变量也取反

3、对偶定理(求原函数对偶式:YD ):变量不取反

若干常用公式

吸收律:A+A’B=A+B(若两个乘积项相加时,其中一项的部分因子是另一项的补,则该部分因子是多余的)包含律:AB+A’C+BC=AB+A’C(若两个乘积项中分别包含A和A',而其余因子组成第三个乘积项,则第三个乘积项是多余的)交叉互换律:AB+A’C=(A+C)(A’+B)(首尾加,中间加,再相乘)、加对乘的分配律原理就是这个!

逻辑函数表示方法

1、逻辑函数真值表

2、逻辑函数式

3、逻辑图

4、波形图:按时间顺序,也称为时序图;

逻辑函数表示之间转换:真值表到函数式:

1、找出逻辑函数值为1 的组;

2、“1”保持,“0”写反,组成乘积项;

3、列乘积项相加。

(因为若取一组值使得选中项都不为0,则逻辑函数本身也为0;若取一组值使得选中项最少有一项为1,则逻辑函数值半身也为1.)

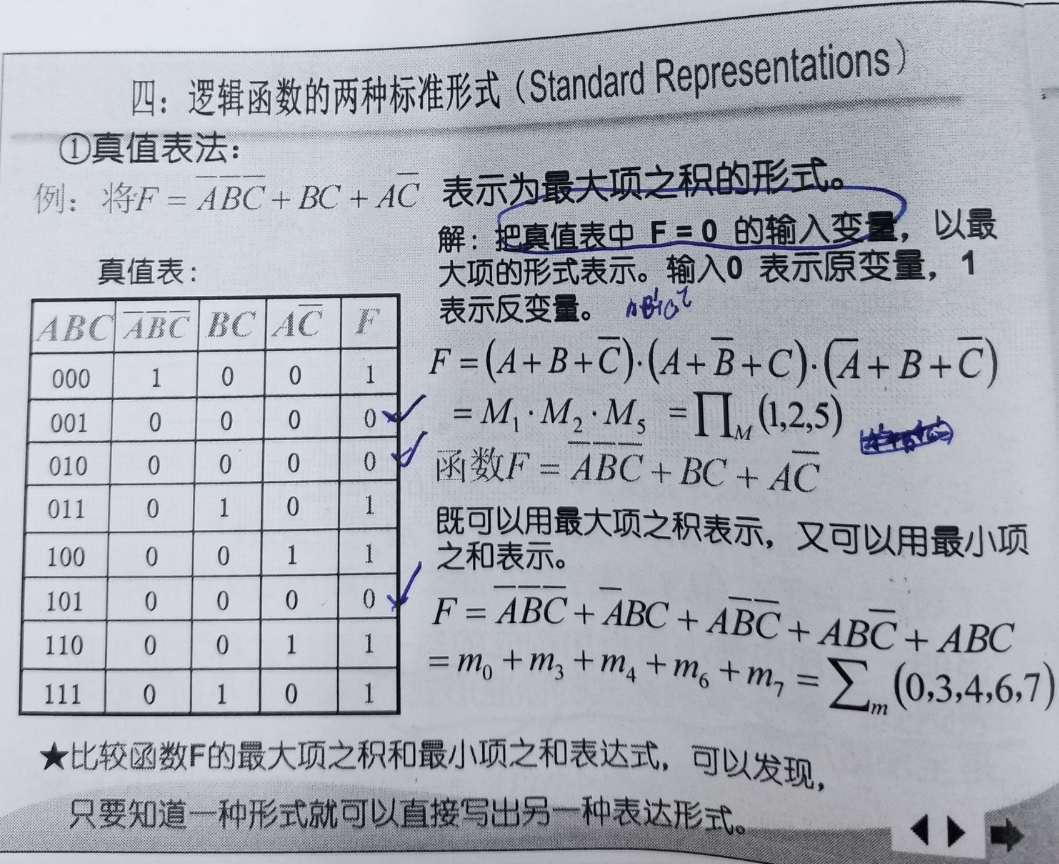

逻辑函数两种标准形式

最小项m(是一个与项)

性质:

- 输入变量任何一组值都能且只能使一组最小项值为

1; - 所有最小项之和为

1; - 任意两项最小项积为

0:mi·mj=0,i≠j; - 编号规则:

A’BC'编号为m2;(原取“1”,反取“0”)

将逻辑函数式用最小项表示

- 真值表法:将逻辑函数式用真值表表示,然后找出函数值为1的项相加;

- 配项法:应用摩根定理后,将缺失的项用(A+A’)表示。

最大项M(是一个或项)

性质

- 输入变量任何一组值都能且只能使一组最大项值为

0; - 所有最大项之积为

0,之和为1; - 任意两最大项之和为

1:Mi+Mj=1,i≠j; - 编号规则:

A’BC'编号为M5;(原取“0”,反取“1”)

将逻辑函数式用最大项表示 - 真值表法:

- 加对乘的分配律及配项法

最小项与最大项关系

- 脚号相同,互为反演:mi’=Mi;

- 因子相同,互为对偶:若m9=AB’C’D,m9D=A+B’+C’+D=M6;脚标之和为15。

逻辑函数的代数化简法

代数法

- 合并项法

- 吸收法:包含吸收律和包含律;

- 消去法:包含吸收律和吸收法;

- 配项法:A+A’=1;A+A=A;

- 将或-与表达式化简为最简与-或式:先利用对偶定理将或-与式变成与-或式,再利用上述方法化简成最简与-或式,再利用一次对偶定理变成最简或-与式。

卡诺图法

卡诺图表示逻辑函数

真值表法:将真值表为“1”的填入卡诺图中;直接观察法:如F=ABC’+A’BC+AC 可直接找出A=B=1,C=0填入“1”,以此类推;利用卡诺图将最小项之和化简为最大项之积:卡诺图中“0”格表示最大项也是最小项的非,因此1、写出F‘=“0”格,2、两边取反利用对偶法写出最大项

按照要求形式化简逻辑函数

与非逻辑形式Look at this

1、填“1”,圈“1”得出F=与-或式

2、两次取反F=F’‘,利用一次反演(与作为整体)得出与非式 (共两次取反,一次反演)或非逻辑形式Ahahah

1、填“1”,圈“0”得出F’与或式

2、对F两边取反利用反演定理,得出或与式

3、对F两次取反一次反演(或式作为整体)得出F或与式

(共三次取反,两次反演)与或非逻辑形式aiyouwei

1、圈“0”得到F‘的与或式

2、F’两边取反得到与或非式(共一次取反0次反演)

Tips:将形式变化时比如:或与变成与或就要用到反演定理!

卡诺图化简逻辑函数方法

步骤

1、将函数化简成最小项之和,填入卡诺图

2、画合并圈,圈内格子个数为2n格

化简原则

- 合并圈远大,因子越少;

- 合并圈个数越少,与项越少;

- 同一个“1”格可以圈多次;

- 每一个合并圈须有新的“1”格。

Tips

- ·若要求利用卡诺图写出最简或-与式:则填“1”格,圈“0”格,写出F’=“0”格,最后两边取反;利用对偶定理。例题

- 将或-与式填入卡诺图,需要先取反成为F‘,再填入“0”。例题

包含无关最小项逻辑函数化简

Yoo Man

由约束式得出无关最小项,一般在卡诺图中记为“X”,对化简有用记为“1”,无用记为“0”。

多输出函数化简

哼!!!

不能只追求单一函数最简,应该考虑多输出之间的公共项!

门电路

待更。。。

组合逻辑电路

分析与设计方法

组合逻辑电路:任意时刻的输出仅仅取决于该时刻的输入,与电路原来状态无关。无记忆性。

分析方法:

一击致命:通过分析找出电路逻辑功能表。

步骤

- 先逐级写出输入到输出的逻辑函数式;

- 通过公式法或者卡诺图化简函数表达式;

- 有必要列出真值表总结规律。

设计方法:

步骤:

- 抽象、确定输入输出变量、赋值“0”和“1”;

- 根据给定描述写出真值表;

- 根据真值表写出逻辑函数式;

- 化简成所规定的器件形式,如:用与非门、与或门、与或非门实现(与或到与非 两次取反包含一次反演,与或非则需要在卡诺图上圈“0”);

- 画出逻辑图。

常用组合逻辑电路

编码器

一、普通编码器:同一时刻只允许一个输入端有信号。如何写出逻辑函数式:根据真值表写逻辑函数式时选出值为“1”里为正的变量(快速化简法)。

二、优先编码器:按优先权排队。

1、8线–3线优先权编码器(74HC148):

- 有选通输入端S’(

低电平有效)、选通输出端Ys’(高电平有效)、扩展端YEX’(高电平有效、就是高电平时扩展)看吧; - 利用Ys’和YEX’可以实现扩展功能、不选通时默认输出高电平。

扩展时一般高位编码位放在高位片选通端

译码器

1、2–4译码器:有个选通信号ST’(低电平有效)

2、3线–8线译码器(74HC148):

- 完全译码器,有三个“片选”输入端S1=1、S2’+S3’=0时选通;

- 将S1作为数据输入端时,可做为数据分配器

- 扩展时要找准片选端口、线选端口

3、二–十进制译码器:超过10的是伪码,可以变成3线–8线译码器

4、用译码器实现组合逻辑电路:

最小项:将式子化成最小项之和,然后利用Y0’=m0’转化,其中用到两次取反包含一次反演,最终用到与非门实现最大项:将式子化成最大项之积形式(可通过与最小项的关系一步写成),然后利用M0’=m0写成Y0’…与的形式,最终用与门实现。

数据选择器

- 数据选择:74HC153为例,双4选1数据选择器。有地址输入端A0、A1,数据输入端,还有控制端S’(低电平有效)

- 设计组合逻辑电路(同译码器原理类似):将地址输入端赋给所要实现的变量,而数据输入端为适当状态(原、反变量、“0”,“1”)。

加法器

一:一位加法器

- 半加器:不考虑来自低位的进位CI,但有进位输出CO。S=A异或B,CO=AB。

- 全加器:考虑低位进位CI,相当于三位相加

二:多位加法器

- 串行进位加法器:将两位加法器串联起来,低位进位CO作为高位进位输入CI,最低位CI接地。缺点是速度慢。

- 超前进位加法器:写啥呀,没看懂。

三:设计组合逻辑电路:有数值相加的逻辑电路比较好用加法器设计。比如将8421BCD码转换成余3码输出。你瞅瞅

数值比较器

- 一位数值比较器:利用逻辑关系比较AB大小表示

- 多位数值比较器:由高向低逐一比较,可以分为高位比较、低位比较(三种结果可以记为I(A<B)、I(A>B)、I(A=B)),若是没有低位比较信息时,令I(A<B)=I(A>B)=0,I(A=B)=1。

组合逻辑竞争–冒险现象

竞争:门电路两个输入信号同时向相反的逻辑电平跳变(一个是1到0,一个是0到1)的现象称为竞争。由于竞争现象产生的脉冲尖峰–竞争冒险

-

成因:由于竞争的存在而在电路输出端可能产生脉冲尖峰。称为竞争–冒险。

-

检查方法

-

消除方法

奶潇

最后

以上就是快乐外套最近收集整理的关于数电复试复习笔记(上)数电复试复习笔记的全部内容,更多相关数电复试复习笔记(上)数电复试复习笔记内容请搜索靠谱客的其他文章。

发表评论 取消回复