目录

一、实验要求:

二、实验步骤分析:

三、核心程序代码、仿真分析

3.1 CNT30

3.2 TZKZQ 调整控制端

3.3 DISPLAY_CONTROL 扫描控制端

3.4 DISPLAY 显示控制

3.5 引脚锁定:

3.6 波形仿真图

四、实验现象:

五、部分程序源码:

5.1 DISPLAY_CONTROL (扫描控制端)

5.2 DISPLAY (动态显示端)

5.3 CNT30(月份对应天数)

5.4 TZKZQ (调整控制端)

5.5 SHJSQSYSTEM(综合计数器系统顶层文件)

本次计时系统设计综合以往实验,达到更好的显示功能和效果。

本次实验代码量是巨大的,并且每个模块之间紧密联系,理解整个系统的电路和设计是花费较多时间的 ,所以将个人理解和设计思路与大家分享。

一、实验要求:

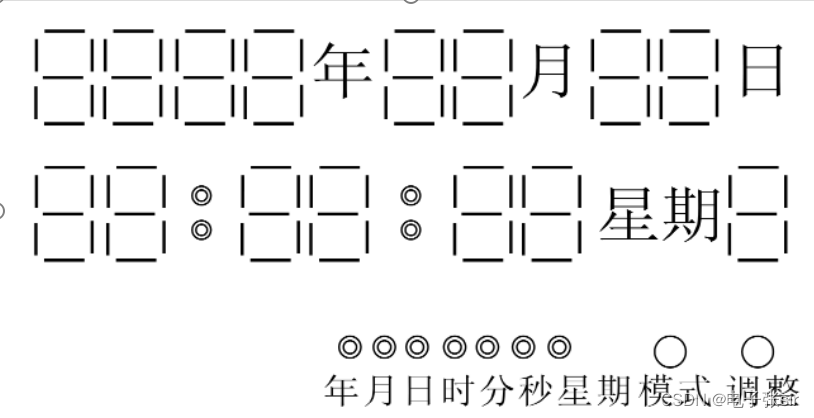

设计一个综合性的计时系统,要求能实现年、月、日、时、分、秒及星期的计数等综合计时功能,同时将计时结果通过15个七段数码管显示,并且可通过两个设置键(4个按键),对计时系统的有关参数进行调整。具体系统功能面板如下图所示

二、实验步骤分析:

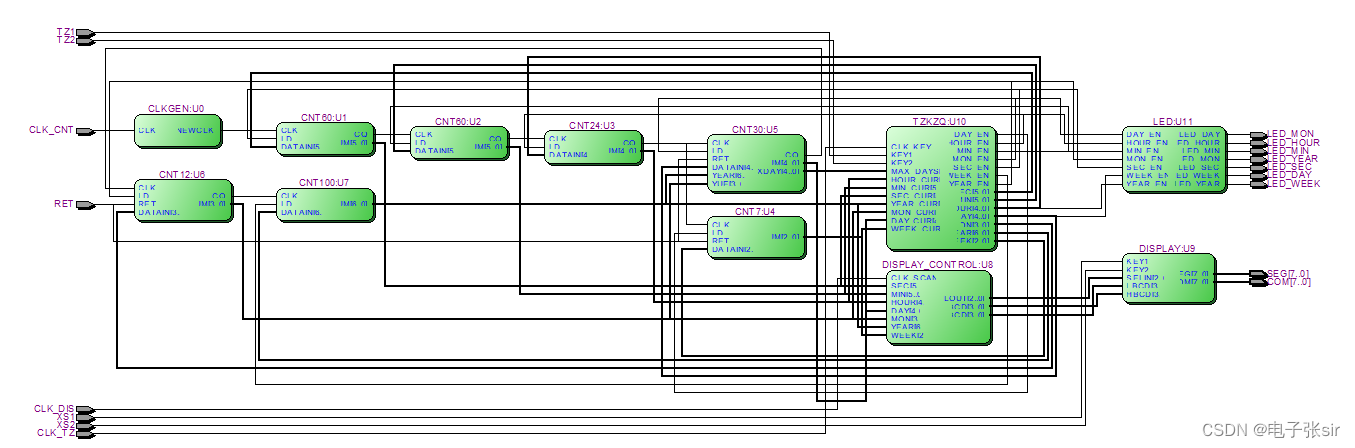

对整个设计电路进行分析可知主要由三个模块构成:计时模块、显示控制模块、调整控制模块

2.1 计时模块:就是以往的计数器CNT,实现的功能从年到秒,所以需要用CNT60、CNT24、CNT7、CNT30、CNT12、CNT100分别对应秒、分(都是CNT60) 、小时、周几、多少号、月、年。

要知道日、月、星期是从1开始计数的,其他的是从0开始计数的。并且对于在一年中,每一个月的天数是不一样的。大家都知道顺口溜:

一三五七八十腊,三十一天永不落;于是四、六、九、十则是三十天一个月。

对于二月极为特殊,在闰年二月是29天,不在闰年时则是28天。

2.2 显示控制模块:将计数的结果分三批显示至FPGA开发板上,其中需要显示控制和动态显示俩个组成。

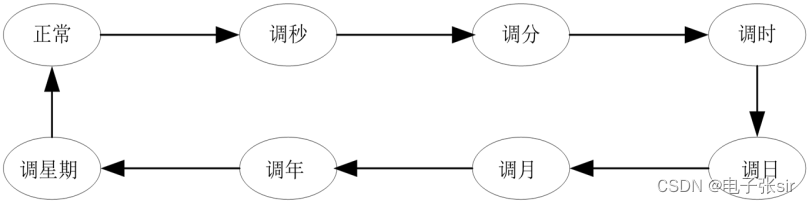

2.3 调整控制模块:为了和手表的功能一样可以调整时间来对应现在的时间,所以需要调整控制模块去调整对应时间的各个模块。如下图所示:

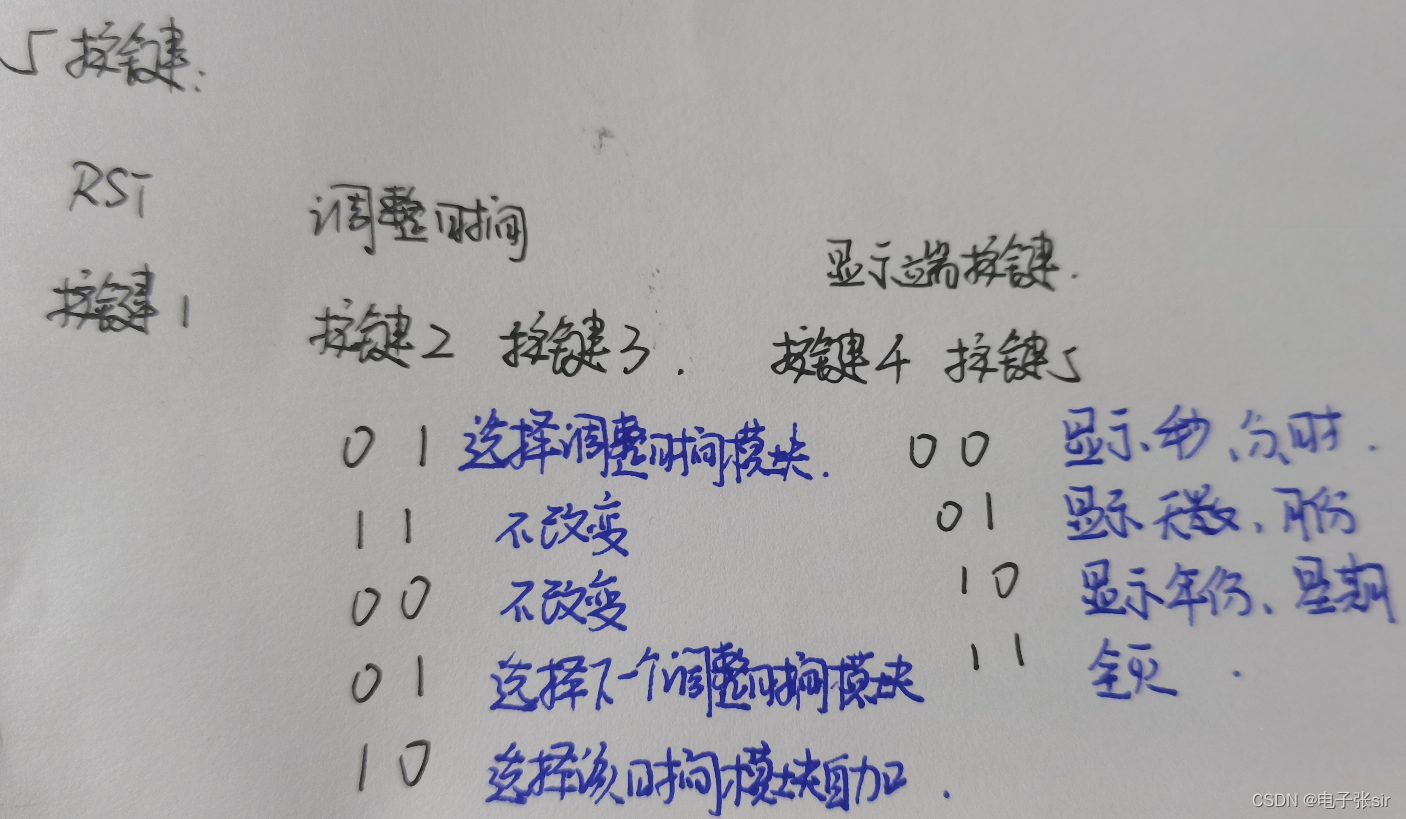

利用按键实现如下图所示,当按键跳到不同的位置后可以对显示和调整的部分进行选择。

(可以将该系统当成万年历 例:你可以清楚的知道现在是2022年5月16号 00:07:14 星期一

如果系统不是表示现在的时间,那么通过调整使之对应该时间)

可以看到整体的RTL图,对应的模块都已显示。

RTL图

三、核心程序代码、仿真分析

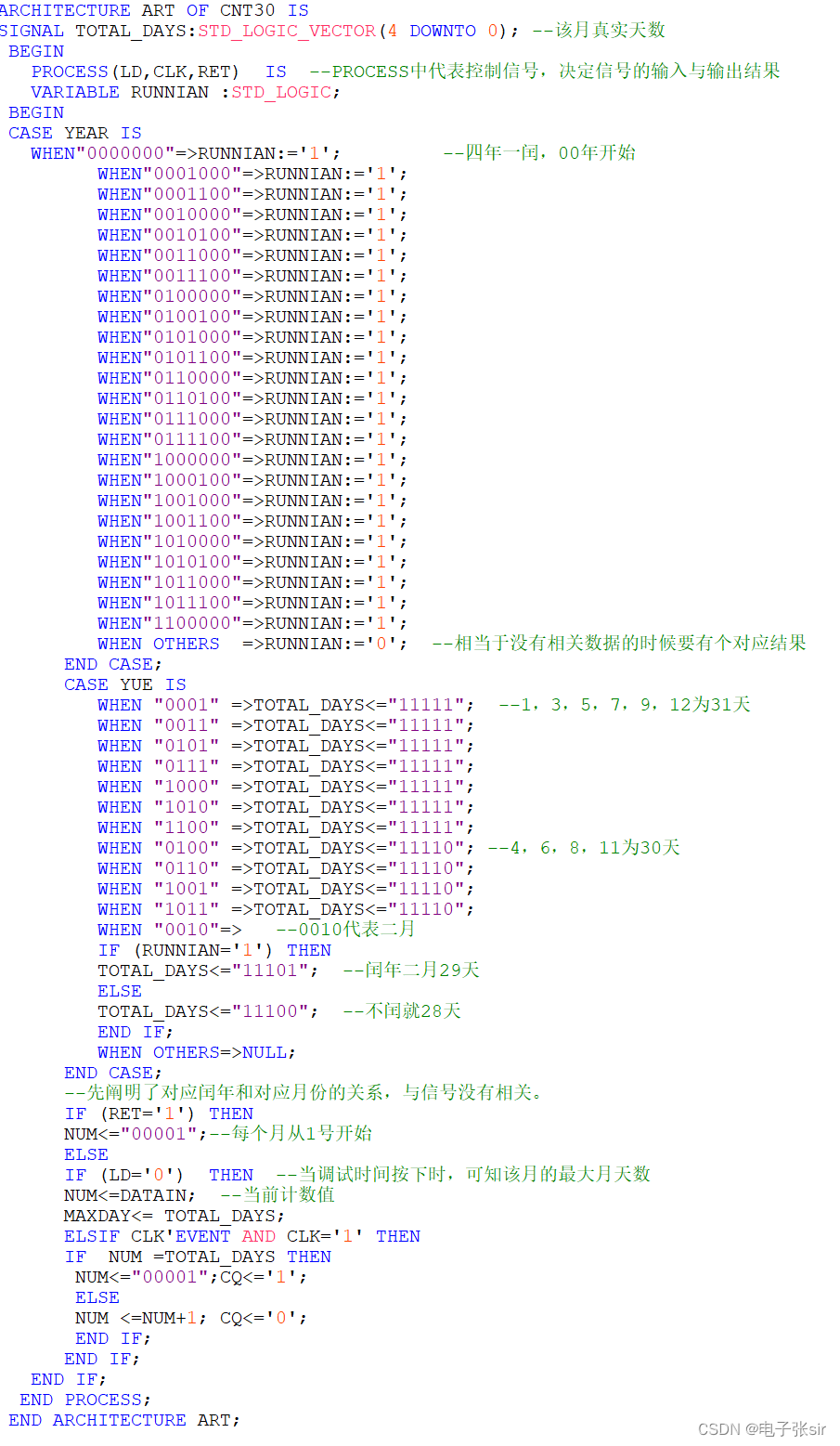

3.1 CNT30

由于月份的天数对于不同年和不同月其天数是不同的,所以思考需要详细,对于闰年的特殊情况都需要列出,我们熟知的月天数列出,对于极为特殊的二月需要单独考虑 ,其中有用到MAXDAY输出,当调整时间按下后,通过软件仿真可以知道该月对于该月的天数最大为多少。

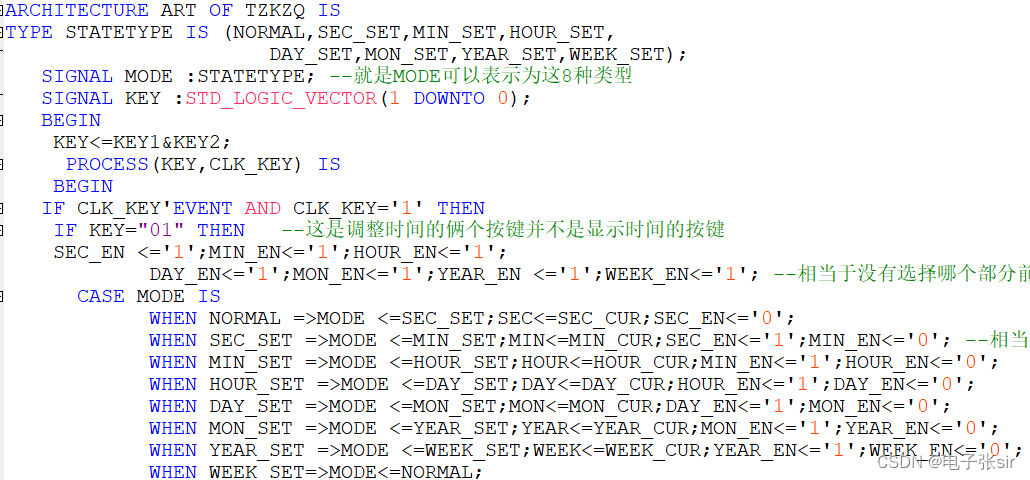

3.2 TZKZQ 调整控制端

调整控制端需要将计数器的结果全部作为输入,将输出控制信号和调整后的时间。

其中用到MODE选择的部分,首先控制信号都为1(控制信号低电平有效),所以计时器正常计时

当按下调整按键为01 的时候,选择调整时间的模块,由于是时钟产生的CASE语句会一一经过,当要选择分的时候,由于先经过了给了控制信号,所以当调整分的时候需要将调整秒的信号置1.以此类推即可。

例子:新生开学需要军训,有七个小绿人都没有带水壶,但是他们都想喝水,所以教官就拿出一瓶水给他们,命令他们:只有我给命令给你的时候,你才可以喝,所以当他命令小秒同学喝水的时候,其他人正常军训,当给小分同学命令喝水时,需要给小秒命令叫他停止喝水,并将水壶递给小分。这个思想是一致的。

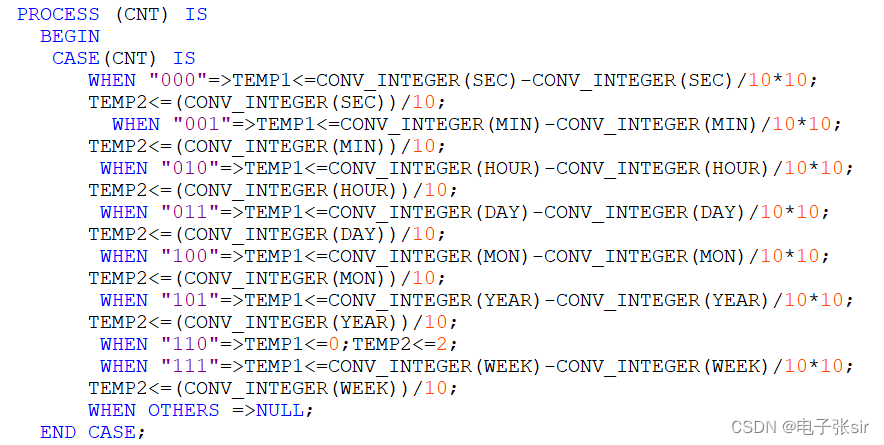

3.3 DISPLAY_CONTROL 扫描控制端

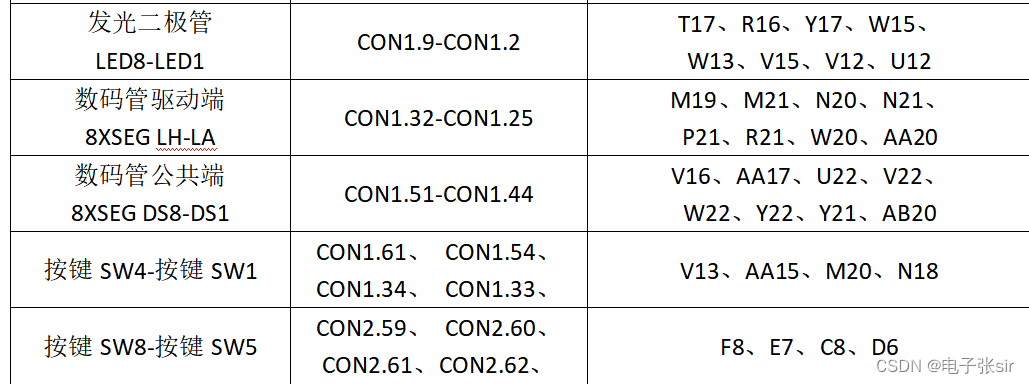

这里用到位数分离的方法,可以知道的时间位数都是俩位数的,所以只需要将时间的位数进行分离开并且分开进行显示即可,将分为LBCD和HBCD后输入到显示端进行控制数码管的显示。

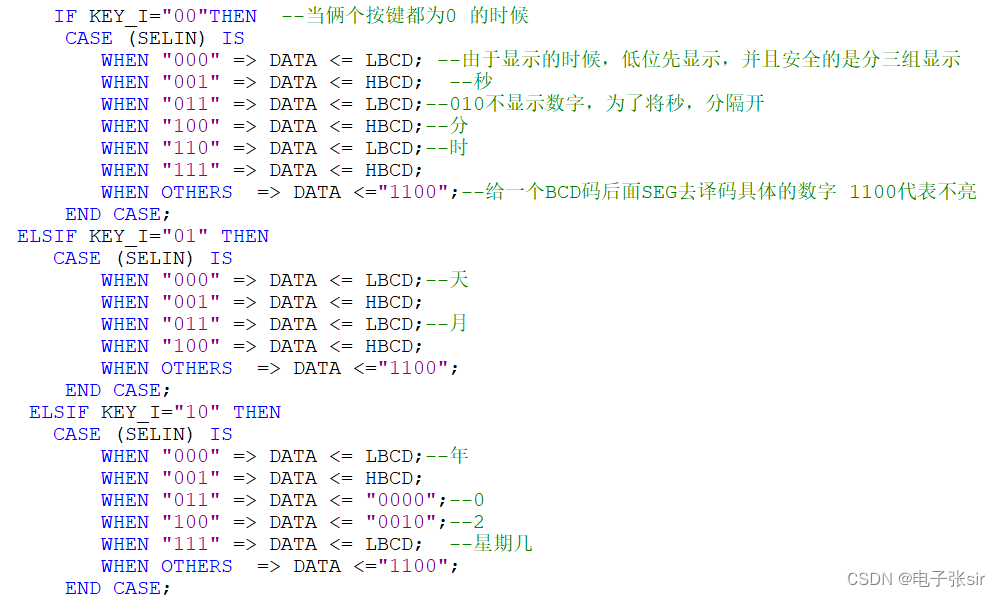

3.4 DISPLAY 显示控制

将显示控制的信号低位BCD码和低位BCD码输入到显示端, 用俩个按键来控制显示的情况,将秒、分、时一部分,天数、月份第二部分,年份和星期第三部分显示。

俩个按键为00的时候显示第一部分,01的时候显示第二部分,10显示第三部分。

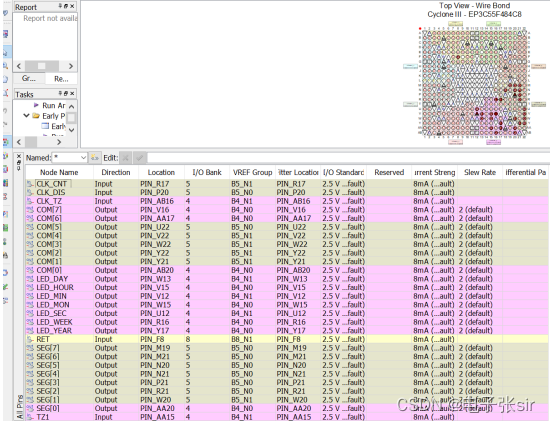

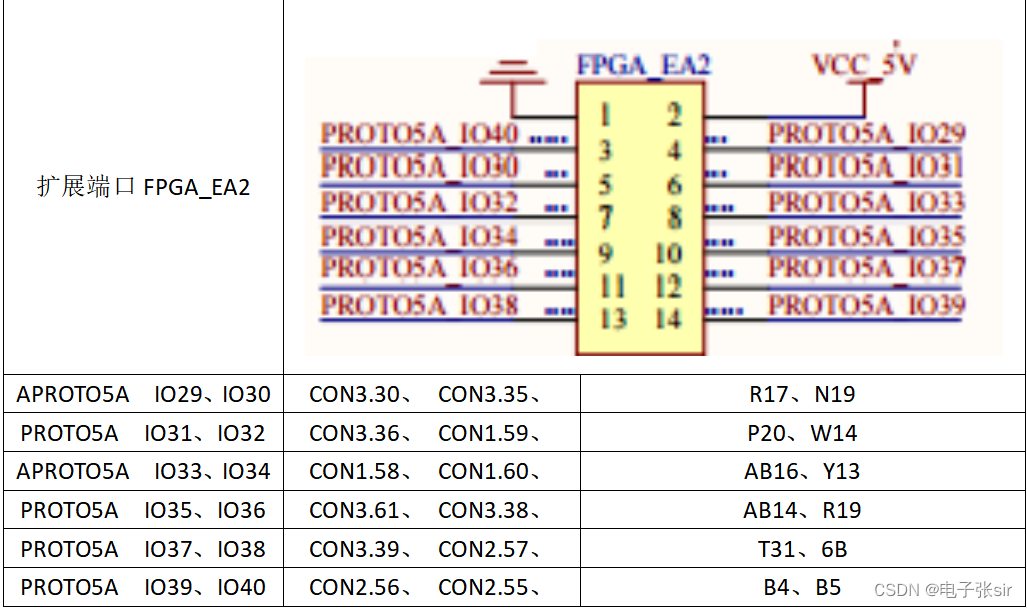

3.5 引脚锁定:

具体的引脚锁定可以按照常用锁定来配置即可,对照RTL图可知用到了三个时钟信号,5个按键开关,数码管的显示端,驱动端和七个LED灯。如下图:

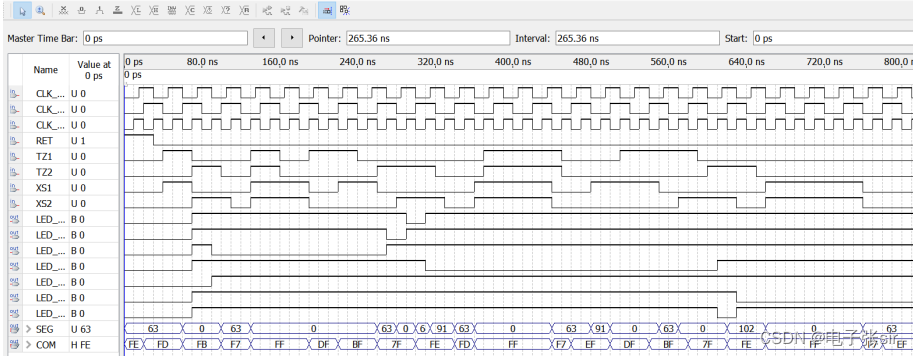

3.6 波形仿真图

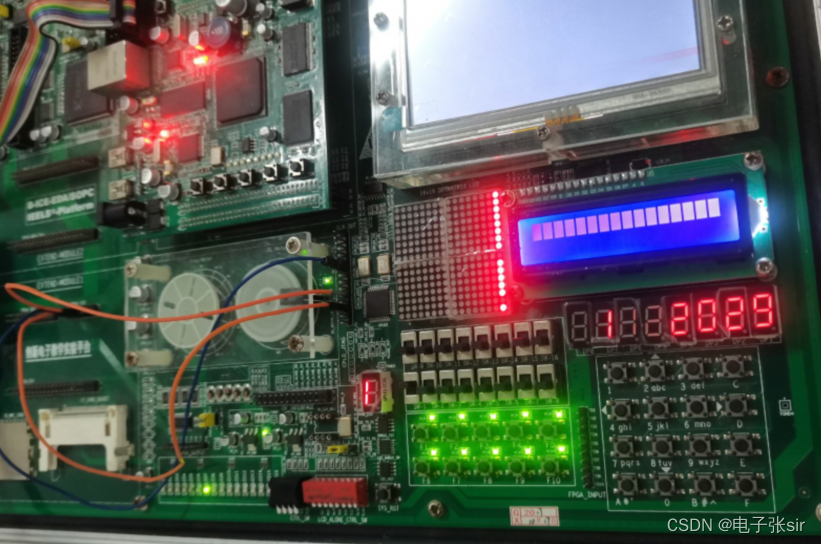

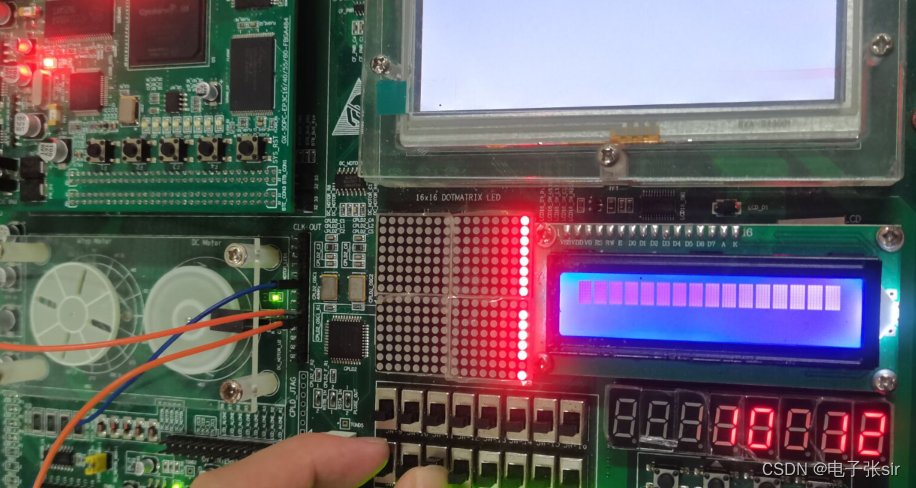

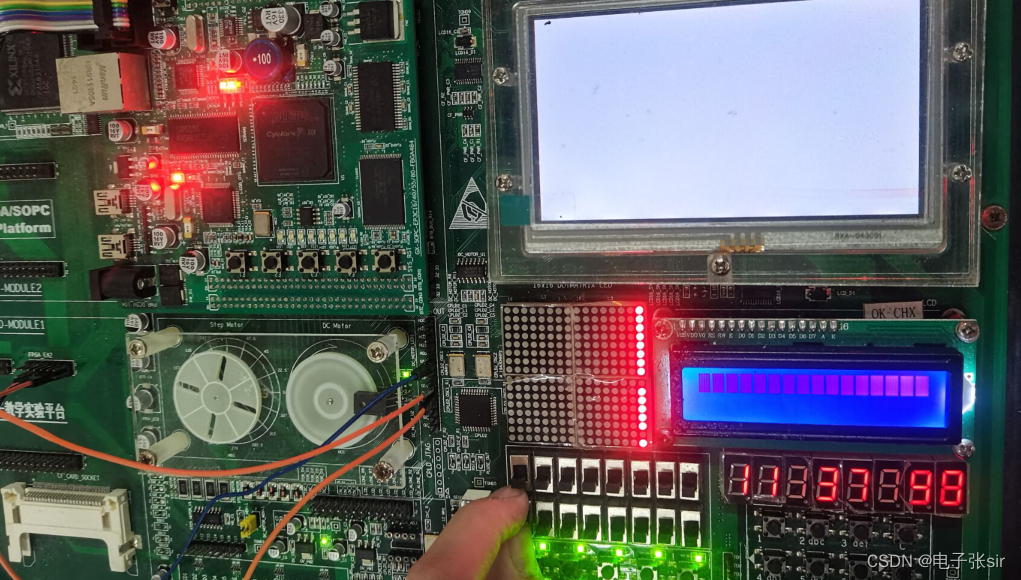

四、实验现象:

第三部分显示 星期和年份

第二部分显示天数,月份

第一部分显示秒 、分、时

五、部分程序源码:

5.1 DISPLAY_CONTROL (扫描控制端)

LIBRARY IEEE;

USE IEEE. STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY DISPLAY_CONTROL IS

PORT(CLK_SCAN:IN STD_LOGIC;

SEC,MIN:IN STD_LOGIC_VECTOR(5 DOWNTO 0);

HOUR:IN STD_LOGIC_VECTOR(4 DOWNTO 0);

DAY:IN STD_LOGIC_VECTOR(4 DOWNTO 0);

MON:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

YEAR:IN STD_LOGIC_VECTOR(6 DOWNTO 0);

WEEK:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

SELOUT:OUT STD_LOGIC_VECTOR(2 DOWNTO 0);

HBCD,LBCD:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END ENTITY DISPLAY_CONTROL;

ARCHITECTURE ART OF DISPLAY_CONTROL IS

SIGNAL TEMP1,TEMP2:INTEGER RANGE 0 TO 9;

SIGNAL CNT:STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

PROCESS(CLK_SCAN) IS

BEGIN

IF CLK_SCAN'EVENT AND CLK_SCAN='1' THEN

IF CNT="111" THEN

CNT<="000";

ELSE

CNT<=CNT+1;

END IF;

END IF;

END PROCESS;

SELOUT<=CNT;

PROCESS (CNT) IS

BEGIN

CASE(CNT) IS

WHEN "000"=>TEMP1<=CONV_INTEGER(SEC)-CONV_INTEGER(SEC)/10*10;

TEMP2<=(CONV_INTEGER(SEC))/10;

WHEN "001"=>TEMP1<=CONV_INTEGER(MIN)-CONV_INTEGER(MIN)/10*10;

TEMP2<=(CONV_INTEGER(MIN))/10;

WHEN "010"=>TEMP1<=CONV_INTEGER(HOUR)-CONV_INTEGER(HOUR)/10*10;

TEMP2<=(CONV_INTEGER(HOUR))/10;

WHEN "011"=>TEMP1<=CONV_INTEGER(DAY)-CONV_INTEGER(DAY)/10*10;

TEMP2<=(CONV_INTEGER(DAY))/10;

WHEN "100"=>TEMP1<=CONV_INTEGER(MON)-CONV_INTEGER(MON)/10*10;

TEMP2<=(CONV_INTEGER(MON))/10;

WHEN "101"=>TEMP1<=CONV_INTEGER(YEAR)-CONV_INTEGER(YEAR)/10*10;

TEMP2<=(CONV_INTEGER(YEAR))/10;

WHEN "110"=>TEMP1<=0;TEMP2<=2;

WHEN "111"=>TEMP1<=CONV_INTEGER(WEEK)-CONV_INTEGER(WEEK)/10*10;

TEMP2<=(CONV_INTEGER(WEEK))/10;

WHEN OTHERS =>NULL;

END CASE;

CASE(TEMP1) IS

WHEN 0 =>LBCD<="0000";

WHEN 1 =>LBCD<="0001";

WHEN 2 =>LBCD<="0010";

WHEN 3 =>LBCD<="0011";

WHEN 4 =>LBCD<="0100";

WHEN 5 =>LBCD<="0101";

WHEN 6 =>LBCD<="0110";

WHEN 7 =>LBCD<="0111";

WHEN 8 =>LBCD<="1000";

WHEN 9 =>LBCD<="1001";

WHEN OTHERS =>LBCD<="0000";

END CASE;

CASE TEMP2 IS

WHEN 0 =>HBCD<="0000";

WHEN 1 =>HBCD<="0001";

WHEN 2 =>HBCD<="0010";

WHEN 3 =>HBCD<="0011";

WHEN 4 =>HBCD<="0100";

WHEN 5 =>HBCD<="0101";

WHEN 6 =>HBCD<="0110";

WHEN 7 =>HBCD<="0111";

WHEN 8 =>HBCD<="1000";

WHEN 9 =>HBCD<="1001";

WHEN OTHERS =>HBCD<="0000";

END CASE;

END PROCESS;

END ARCHITECTURE ART;

5.2 DISPLAY (动态显示端)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY DISPLAY IS

PORT(KEY1: IN STD_LOGIC;

KEY2: IN STD_LOGIC;

SELIN :IN STD_LOGIC_VECTOR(2 DOWNTO 0);

LBCD: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

HBCD : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

SEG:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY DISPLAY;

ARCHITECTURE ART OF DISPLAY IS

SIGNAL DATA:STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL KEY_I :STD_LOGIC_VECTOR(1 DOWNTO 0);

BEGIN

KEY_I<=KEY1&KEY2;

P1:PROCESS(SELIN,KEY_I) IS

BEGIN

IF KEY_I="00" THEN

CASE (SELIN) IS

WHEN "000"=> COM <="11111110";

WHEN "001"=> COM <="11111101";

WHEN "010"=> COM <="11111011";

WHEN "011"=> COM <="11110111";

WHEN "100"=> COM <="11101111";

WHEN "101"=> COM <="11011111";

WHEN "110"=> COM <="10111111";

WHEN "111"=> COM <="01111111";

WHEN OTHERS=> COM <="11111111";

END CASE;

ELSIF KEY_I="01" THEN

CASE (SELIN) IS

WHEN "000"=> COM <="11111110";

WHEN "001"=> COM <="11111101";

WHEN "010"=> COM <="11111011";

WHEN "011"=> COM <="11110111";

WHEN "100"=> COM <="11101111";

WHEN "101"=> COM <="11011111";

WHEN "110"=> COM <="10111111";

WHEN "111"=> COM <="01111111";

WHEN OTHERS=> COM <="11111111";

END CASE;

ELSIF KEY_I="10" THEN

CASE (SELIN) IS

WHEN "000"=> COM <="11111110";

WHEN "001"=> COM <="11111101";

WHEN "010"=> COM <="11111011";

WHEN "011"=> COM <="11110111";

WHEN "100"=> COM <="11101111";

WHEN "101"=> COM <="11011111";

WHEN "110"=> COM <="10111111";

WHEN "111"=> COM <="01111111";

WHEN OTHERS=> COM <="11111111";

END CASE;

ELSE

COM<="11111111";

END IF;

END PROCESS P1;

P2:PROCESS(SELIN,KEY_I) IS

BEGIN

IF KEY_I="00"THEN

CASE (SELIN) IS

WHEN "000" => DATA <= LBCD;

WHEN "001" => DATA <= HBCD;

WHEN "011" => DATA <= LBCD;

WHEN "100" => DATA <= HBCD;

WHEN "110" => DATA <= LBCD;

WHEN "111" => DATA <= HBCD;

WHEN OTHERS => DATA <="1100";

END CASE;

ELSIF KEY_I="01" THEN

CASE (SELIN) IS

WHEN "000" => DATA <= LBCD;

WHEN "001" => DATA <= HBCD;

WHEN "011" => DATA <= LBCD;

WHEN "100" => DATA <= HBCD;

WHEN OTHERS => DATA <="1100";

END CASE;

ELSIF KEY_I="10" THEN

CASE (SELIN) IS

WHEN "000" => DATA <= LBCD;

WHEN "001" => DATA <= HBCD;

WHEN "011" => DATA <= "0000";

WHEN "100" => DATA <= "0010";

WHEN "111" => DATA <= LBCD;

WHEN OTHERS => DATA <="1100";

END CASE;

ELSE

DATA<="1100";

END IF;

CASE DATA IS

WHEN "0000" => SEG <="00111111";

WHEN "0001" => SEG <="00000110";

WHEN "0010" => SEG <="01011011";

WHEN "0011" => SEG <="01001111";

WHEN "0100" => SEG <="01100110";

WHEN "0101" => SEG <="01101101";

WHEN "0110" => SEG <="01111101";

WHEN "0111" => SEG <="00000111";

WHEN "1000" => SEG <="01111111";

WHEN "1001" => SEG <="01101111";

WHEN OTHERS => SEG <="00000000";

END CASE;

END PROCESS P2;

END ARCHITECTURE ART;

5.3 CNT30(月份对应天数)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT30 IS

PORT(LD: IN STD_LOGIC;

CLK:IN STD_LOGIC;

RET: IN STD_LOGIC;

DATAIN: IN STD_LOGIC_VECTOR(4 DOWNTO 0);

YEAR :IN STD_LOGIC_VECTOR(6 DOWNTO 0);

YUE: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

NUM: BUFFER STD_LOGIC_VECTOR( 4 DOWNTO 0);

MAXDAY: OUT STD_LOGIC_VECTOR(4 DOWNTO 0);

CQ : OUT STD_LOGIC);

END ENTITY CNT30;

ARCHITECTURE ART OF CNT30 IS

SIGNAL TOTAL_DAYS:STD_LOGIC_VECTOR(4 DOWNTO 0);

BEGIN

PROCESS(LD,CLK,RET) IS

VARIABLE RUNNIAN :STD_LOGIC;

BEGIN

CASE YEAR IS

WHEN"0000000"=>RUNNIAN:='1';

WHEN"0001000"=>RUNNIAN:='1';

WHEN"0001100"=>RUNNIAN:='1';

WHEN"0010000"=>RUNNIAN:='1';

WHEN"0010100"=>RUNNIAN:='1';

WHEN"0011000"=>RUNNIAN:='1';

WHEN"0011100"=>RUNNIAN:='1';

WHEN"0100000"=>RUNNIAN:='1';

WHEN"0100100"=>RUNNIAN:='1';

WHEN"0101000"=>RUNNIAN:='1';

WHEN"0101100"=>RUNNIAN:='1';

WHEN"0110000"=>RUNNIAN:='1';

WHEN"0110100"=>RUNNIAN:='1';

WHEN"0111000"=>RUNNIAN:='1';

WHEN"0111100"=>RUNNIAN:='1';

WHEN"1000000"=>RUNNIAN:='1';

WHEN"1000100"=>RUNNIAN:='1';

WHEN"1001000"=>RUNNIAN:='1';

WHEN"1001100"=>RUNNIAN:='1';

WHEN"1010000"=>RUNNIAN:='1';

WHEN"1010100"=>RUNNIAN:='1';

WHEN"1011000"=>RUNNIAN:='1';

WHEN"1011100"=>RUNNIAN:='1';

WHEN"1100000"=>RUNNIAN:='1';

WHEN OTHERS =>RUNNIAN:='0';

END CASE;

CASE YUE IS

WHEN "0001" =>TOTAL_DAYS<="11111";

WHEN "0011" =>TOTAL_DAYS<="11111";

WHEN "0101" =>TOTAL_DAYS<="11111";

WHEN "0111" =>TOTAL_DAYS<="11111";

WHEN "1000" =>TOTAL_DAYS<="11111";

WHEN "1010" =>TOTAL_DAYS<="11111";

WHEN "1100" =>TOTAL_DAYS<="11111";

WHEN "0100" =>TOTAL_DAYS<="11110";

WHEN "0110" =>TOTAL_DAYS<="11110";

WHEN "1001" =>TOTAL_DAYS<="11110";

WHEN "1011" =>TOTAL_DAYS<="11110";

WHEN "0010"=> --0010

IF (RUNNIAN='1') THEN

TOTAL_DAYS<="11101";

ELSE

TOTAL_DAYS<="11100";

END IF;

WHEN OTHERS=>NULL;

END CASE;

IF (RET='1') THEN

NUM<="00001";

ELSE

IF (LD='0') THEN

NUM<=DATAIN;

MAXDAY<= TOTAL_DAYS;

ELSIF CLK'EVENT AND CLK='1' THEN

IF NUM =TOTAL_DAYS THEN

NUM<="00001";CQ<='1';

ELSE

NUM <=NUM+1; CQ<='0';

END IF;

END IF;

END IF;

END PROCESS;

END ARCHITECTURE ART;

5.4 TZKZQ (调整控制端)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY TZKZQ IS

PORT( KEY1: IN STD_LOGIC;

KEY2: IN STD_LOGIC;

CLK_KEY:IN STD_LOGIC;

MAX_DAYS:IN STD_LOGIC_VECTOR(4 DOWNTO 0);

SEC_EN ,MIN_EN,HOUR_EN,DAY_EN,

MON_EN,YEAR_EN,WEEK_EN:OUT STD_LOGIC;

HOUR_CUR:IN STD_LOGIC_VECTOR(4 DOWNTO 0);

MIN_CUR,SEC_CUR:IN STD_LOGIC_VECTOR(5 DOWNTO 0);

YEAR_CUR:IN STD_LOGIC_VECTOR(6 DOWNTO 0);

MON_CUR:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

DAY_CUR:IN STD_LOGIC_VECTOR(4 DOWNTO 0);

WEEK_CUR:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

SEC,MIN:BUFFER STD_LOGIC_VECTOR(5 DOWNTO 0);

HOUR:BUFFER STD_LOGIC_VECTOR(4 DOWNTO 0);

DAY:BUFFER STD_LOGIC_VECTOR(4 DOWNTO 0);

MON:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);

YEAR:BUFFER STD_LOGIC_VECTOR(6 DOWNTO 0);

WEEK:BUFFER STD_LOGIC_VECTOR(2 DOWNTO 0));

END ENTITY TZKZQ;

ARCHITECTURE ART OF TZKZQ IS

TYPE STATETYPE IS (NORMAL,SEC_SET,MIN_SET,HOUR_SET,

DAY_SET,MON_SET,YEAR_SET,WEEK_SET);

SIGNAL MODE :STATETYPE;

SIGNAL KEY :STD_LOGIC_VECTOR(1 DOWNTO 0);

BEGIN

KEY<=KEY1&KEY2;

PROCESS(KEY,CLK_KEY) IS

BEGIN

IF CLK_KEY'EVENT AND CLK_KEY='1' THEN

IF KEY="01" THEN

SEC_EN <='1';MIN_EN<='1';HOUR_EN<='1';

DAY_EN<='1';MON_EN<='1';YEAR_EN <='1';WEEK_EN<='1';

CASE MODE IS

WHEN NORMAL =>MODE <=SEC_SET;SEC<=SEC_CUR;SEC_EN<='0';

WHEN SEC_SET =>MODE <=MIN_SET;MIN<=MIN_CUR;SEC_EN<='1';MIN_EN<='0';

WHEN MIN_SET =>MODE <=HOUR_SET;HOUR<=HOUR_CUR;MIN_EN<='1';HOUR_EN<='0';

WHEN HOUR_SET =>MODE <=DAY_SET;DAY<=DAY_CUR;HOUR_EN<='1';DAY_EN<='0';

WHEN DAY_SET =>MODE <=MON_SET;MON<=MON_CUR;DAY_EN<='1';MON_EN<='0';

WHEN MON_SET =>MODE <=YEAR_SET;YEAR<=YEAR_CUR;MON_EN<='1';YEAR_EN<='0';

WHEN YEAR_SET =>MODE <=WEEK_SET;WEEK<=WEEK_CUR;YEAR_EN<='1';WEEK_EN<='0';

WHEN WEEK_SET=>MODE<=NORMAL;

END CASE;

ELSIF KEY="10" THEN

CASE MODE IS

WHEN SEC_SET=>SEC_EN<='0';

IF SEC="111011" THEN

SEC<="000000";

ELSE

SEC<=SEC+1;

END IF;

WHEN MIN_SET=>MIN_EN<='0';

IF MIN="111011" THEN

MIN<="000000";

ELSE

MIN<=MIN+1;

END IF;

WHEN HOUR_SET=>HOUR_EN<='0';

IF HOUR="11000" THEN

HOUR<="00000";

ELSE

HOUR<=HOUR+1;

END IF;

WHEN DAY_SET=>DAY_EN<='0';

IF DAY=MAX_DAYS THEN

DAY<="00001";

ELSE

DAY<=DAY+1;

END IF;

WHEN MON_SET=>MON_EN<='0';

IF MON="1100" THEN

MON<="0001";

ELSE

MON<=MON+1;

END IF;

WHEN YEAR_SET=>YEAR_EN<='0';

IF YEAR="1100011" THEN

YEAR<="0000001";

ELSE

YEAR<=YEAR+1;

END IF;

WHEN WEEK_SET=>WEEK_EN<='0';

IF WEEK="111" THEN

WEEK<="001";

ELSE

WEEK<=WEEK+1;

END IF;

WHEN OTHERS =>NULL;

END CASE;

END IF;

END IF;

END PROCESS;

END ARCHITECTURE ART;5.5 SHJSQSYSTEM(综合计数器系统顶层文件)

LIBRARY IEEE;

USE IEEE. STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ZHJSQSYSTEM IS

PORT ( CLK_CNT:IN STD_LOGIC;--计数器时钟

CLK_TZ:IN STD_LOGIC;--调整控制端始终

CLK_DIS:IN STD_LOGIC; --动态显示控制时钟

RET:IN STD_LOGIC;

TZ1:IN STD_LOGIC;--调整时间按键,分01和10

TZ2:IN STD_LOGIC;

XS1,XS2:IN STD_LOGIC; --调整显示按键,分三组01,10,00

LED_SEC,LED_MIN,LED_HOUR,LED_WEEK,

LED_DAY,LED_MON,LED_YEAR:OUT STD_LOGIC;

COM:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

SEG:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ENTITY ZHJSQSYSTEM;

ARCHITECTURE ART OF ZHJSQSYSTEM IS

COMPONENT CLKGEN IS

PORT(CLK: IN STD_LOGIC;

NEWCLK: OUT STD_LOGIC);

END COMPONENT CLKGEN;

COMPONENT CNT60 IS

PORT(CLK:IN STD_LOGIC;

LD: IN STD_LOGIC;

DATAIN: IN STD_LOGIC_VECTOR(5 DOWNTO 0);

NUM: BUFFER STD_LOGIC_VECTOR(5 DOWNTO 0);

CQ : OUT STD_LOGIC);

END COMPONENT CNT60;

COMPONENT CNT24 IS

PORT( LD: IN STD_LOGIC;

CLK:IN STD_LOGIC;

DATAIN: IN STD_LOGIC_VECTOR(4 DOWNTO 0);

NUM: BUFFER STD_LOGIC_VECTOR(4 DOWNTO 0);

CQ:OUT STD_LOGIC);

END COMPONENT CNT24;

COMPONENT CNT7 IS

PORT(CLK: IN STD_LOGIC;

RET: IN STD_LOGIC;

LD : IN STD_LOGIC;

DATAIN: IN STD_LOGIC_VECTOR(2 DOWNTO 0);

NUM : BUFFER STD_LOGIC_VECTOR(2 DOWNTO 0));

END COMPONENT CNT7;

COMPONENT CNT30 IS

PORT( LD: IN STD_LOGIC;

CLK:IN STD_LOGIC;

RET: IN STD_LOGIC;

DATAIN: IN STD_LOGIC_VECTOR(4 DOWNTO 0);

YEAR :IN STD_LOGIC_VECTOR(6 DOWNTO 0);

YUE: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

NUM: BUFFER STD_LOGIC_VECTOR( 4 DOWNTO 0);

MAXDAY: OUT STD_LOGIC_VECTOR(4 DOWNTO 0);

CQ : OUT STD_LOGIC);

END COMPONENT CNT30;

COMPONENT CNT12 IS

PORT( CLK: IN STD_LOGIC;

LD: IN STD_LOGIC;

RET: IN STD_LOGIC;

DATAIN:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

NUM: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);

CQ: OUT STD_LOGIC);

END COMPONENT CNT12;

COMPONENT CNT100 IS

PORT( CLK:IN STD_LOGIC;

LD:IN STD_LOGIC;

DATAIN: IN STD_LOGIC_VECTOR(6 DOWNTO 0);

NUM :BUFFER STD_LOGIC_VECTOR(6 DOWNTO 0));

END COMPONENT CNT100;

COMPONENT TZKZQ IS

PORT( KEY1: IN STD_LOGIC; --相当于分三种情况显示

KEY2: IN STD_LOGIC;

CLK_KEY:IN STD_LOGIC;

MAX_DAYS:IN STD_LOGIC_VECTOR(4 DOWNTO 0);

SEC_EN ,MIN_EN,HOUR_EN,DAY_EN,

MON_EN,YEAR_EN,WEEK_EN:OUT STD_LOGIC;--灯1对应秒,以此类推

SEC_CUR:IN STD_LOGIC_VECTOR(5 DOWNTO 0);

MIN_CUR:IN STD_LOGIC_VECTOR(5 DOWNTO 0);

HOUR_CUR:IN STD_LOGIC_VECTOR(4 DOWNTO 0);

DAY_CUR:IN STD_LOGIC_VECTOR(4 DOWNTO 0);

WEEK_CUR:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

MON_CUR:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

YEAR_CUR:IN STD_LOGIC_VECTOR(6 DOWNTO 0);

SEC:BUFFER STD_LOGIC_VECTOR(5 DOWNTO 0);

MIN:BUFFER STD_LOGIC_VECTOR(5 DOWNTO 0);

HOUR:BUFFER STD_LOGIC_VECTOR(4 DOWNTO 0);

DAY:BUFFER STD_LOGIC_VECTOR(4 DOWNTO 0);

MON:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);

YEAR:BUFFER STD_LOGIC_VECTOR(6 DOWNTO 0);

WEEK:BUFFER STD_LOGIC_VECTOR(2 DOWNTO 0));

END COMPONENT TZKZQ;

COMPONENT DISPLAY_CONTROL IS

PORT(CLK_SCAN:IN STD_LOGIC;

SEC,MIN:IN STD_LOGIC_VECTOR(5 DOWNTO 0);

HOUR:IN STD_LOGIC_VECTOR(4 DOWNTO 0);

DAY:IN STD_LOGIC_VECTOR(4 DOWNTO 0);

MON:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

YEAR:IN STD_LOGIC_VECTOR(6 DOWNTO 0);

WEEK:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

SELOUT:OUT STD_LOGIC_VECTOR(2 DOWNTO 0);

HBCD,LBCD:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END COMPONENT DISPLAY_CONTROL;

COMPONENT DISPLAY IS

PORT(KEY1: IN STD_LOGIC;

KEY2: IN STD_LOGIC;

SELIN :IN STD_LOGIC_VECTOR(2 DOWNTO 0);

LBCD: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

HBCD : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

SEG:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END COMPONENT DISPLAY;

COMPONENT LED IS

PORT(SEC_EN,MIN_EN,HOUR_EN,WEEK_EN,

DAY_EN,MON_EN,YEAR_EN:IN STD_LOGIC;

LED_SEC,LED_MIN,LED_HOUR,LED_WEEK,LED_DAY,LED_MON,LED_YEAR:OUT STD_LOGIC);

END COMPONENT LED;

SIGNAL EN1,EN2,EN3,EN4,EN5,EN6,EN7:STD_LOGIC; --LD 控制计数器和LED点亮

SIGNAL S1,S2,S3,S4,S5:STD_LOGIC; --进位信号连接线

SIGNAL NEWCLK: STD_LOGIC;

SIGNAL DATA1: STD_LOGIC_VECTOR(5 DOWNTO 0); -- DATA 是计数器的预置数连接线

SIGNAL DATA2: STD_LOGIC_VECTOR(5 DOWNTO 0);--秒和分的

SIGNAL DATA3: STD_LOGIC_VECTOR(4 DOWNTO 0);--小时

SIGNAL DATA4: STD_LOGIC_VECTOR(2 DOWNTO 0);--星期几

SIGNAL DATA5: STD_LOGIC_VECTOR(4 DOWNTO 0);--一个月几天

SIGNAL DATA6: STD_LOGIC_VECTOR(3 DOWNTO 0);--月

SIGNAL DATA7: STD_LOGIC_VECTOR(6 DOWNTO 0);--年

SIGNAL NUM1: STD_LOGIC_VECTOR(5 DOWNTO 0);--为计数结果连接线

SIGNAL NUM2: STD_LOGIC_VECTOR(5 DOWNTO 0);--上个为秒,这为分

SIGNAL NUM3: STD_LOGIC_VECTOR(4 DOWNTO 0);--时

SIGNAL NUM4: STD_LOGIC_VECTOR(2 DOWNTO 0);--星期几

SIGNAL NUM5: STD_LOGIC_VECTOR(4 DOWNTO 0);--月天数

SIGNAL NUM6: STD_LOGIC_VECTOR(3 DOWNTO 0);--月

SIGNAL NUM7: STD_LOGIC_VECTOR(6 DOWNTO 0);--年

SIGNAL SEL: STD_LOGIC_VECTOR(2 DOWNTO 0); --将数码管点亮从控制端连接到显示端

SIGNAL HBCD1,LBCD1:STD_LOGIC_VECTOR(3 DOWNTO 0); --将显示控制的高低BCD连接在显示端

SIGNAL MAX:STD_LOGIC_VECTOR(4 DOWNTO 0); --由于每月的数极为特殊。只当调整时间的时候才会显示

END ARCHITECTURE ART;

整个系统设计的源程序可以到我的资源库中自行下载!(内部含重要代码详细解析)

最后

以上就是幸福向日葵最近收集整理的关于[EDA] 综合计时系统设计 【VHDL】一、实验要求:二、实验步骤分析:三、核心程序代码、仿真分析四、实验现象:五、部分程序源码:的全部内容,更多相关[EDA]内容请搜索靠谱客的其他文章。

![[EDA] 综合计时系统设计 【VHDL】一、实验要求:二、实验步骤分析:三、核心程序代码、仿真分析四、实验现象:五、部分程序源码:](https://www.shuijiaxian.com/files_image/reation/bcimg16.png)

发表评论 取消回复