Verilog数字系统设计(夏宇闻)- 绪论笔记

- C与HDL

- C配合Verilog HDL设计算法的硬件电路时考虑到三个问题:

- 为什么选择C语言与Verilog HDL配合使用?

- C语言与Verilog HDL的使用有何限制?

- 如何利用C语言来加速硬件的设计和故障检测?

- Verilog和VHDL:

- Verilog HDL与VHDL的建模能力比较:

- 行为描述/结构描述

- CPLD/FPGA

- 在数字信号处理的领域内有相当大的一部分工作是事后处理的,即利用通用的计算机系统来处理此类问题。还有一类数字信号处理必须在规定时间内完成。

- 有的数字信号处理对时间的要求非常苛刻。以至于用高速的通用微处理器芯片也无法在规定时间内完成必要的计算。因此,必须为这样的运算设计一个专用的高速硬件逻辑电路,在高速FPGA器件上实现或者制成高速专用集成电路。

- 数字信号处理系统由高速专用数字逻辑系统或者专用数字信号处理器构成,通常包括高速数据通道接口和高速算法电路。

- 现代专用集成电路的设计是借助电子电路设计自动化(Electronic Design Automation,EDA)工具完成。因为现代复杂数字逻辑系统的设计都是借助于EDA工具完成的,无论电路系统的仿真和综合都需要掌握硬件描述语言。

- 为了准确地表示特定问题的信息并顺利地解决有关的计算问题,需要采用一些特殊方法并建立相应的模型。所谓算法就是解决特定问题的有序步骤;所谓数据结构就是解决特定问题的相应模型。

C与HDL

- 用HDL的程序设计硬件的好处是易于理解、易于维护、调试电路速度快,有很多易于掌握的仿真、综合和布局布线工具,还可以用C语言配合HDL来做逻辑设计的布线前和布线后仿真,验证功能是否正确。

- 在算法硬件电路的研制过程中,计算电路的结构和芯片的工艺对运行速度有很大的影响,所以在电路结构完全确定之前,必须经过多次仿真,即:

- C语言的功能仿真;

- C语言的并行结构仿真;

- Verilog HDL的行为仿真;

- Verilog HDL RTL级仿真;

- 综合后门级结构仿真;

- 布局布线后仿真;

- 电路实现仿真。

C配合Verilog HDL设计算法的硬件电路时考虑到三个问题:

为什么选择C语言与Verilog HDL配合使用?

首先,C语言很灵活,差错功能强,还可以通过PLI(编程语言接口)编写自己的系统任务,并直接与硬件仿真器结合使用。C语言是目前世界上应用最为广泛的一种编程语言。因而C语言的设计环境比Verilog更完善。C语言有可靠的编译环境,语法完备,缺陷较少,可应用于许多英语。比较起来,Verilog只针对硬件描述,在别处使用(如用于算法表达等)并不方便。

既要利用C语言的完整性,又要结合Verilog对硬件描述的准确性,来更快更好地设计出符合性能要求的硬件电路系统。利用C完备的查错和编译环境,设计者可以先设计出一个功能正确的设计单元,以此作为设计比较的标准。然后,把C程序一段一段地改写成用并行结构(类似于Verilog)描述的C程序,此时还是在C的环境里,使用的依然是C语言。如果运行结果正确,就将C语言关键字用Verilog相应的关键字替换,进入Verilog的环境。将测试输入同时加到C与Verilog两个单元,比较输出,发现问题,进行更正,进行测试,直至测试通过。

C语言与Verilog HDL的使用有何限制?

可用于综合的Verilog语法有限,找不到对应的关键字替换C中关键字。Verilog可用的输入输出函数很少,C的花样很多。C的函数调用与Verilog中模块的调用有区别。

C是一行接一行依次执行的,属于顺序结构;而Verilog描述的硬件是可以在同一时间同时执行的,属于并行结构。

如何利用C语言来加速硬件的设计和故障检测?

- C可以与Verilog配合使用,辅助设计硬件。

- C语言与Verilog类似,只要稍加限制,C语言的程序很容易转成Verilog的行为程序。

Verilog和VHDL:

VHDL——VHSIC Hardware Description Language,VHSIC——Very High Speed Integrated Circuit,甚高速集成电路的硬件描述语言。

能够形式化地抽象表示电路的行为和结构;支持逻辑设计中层次与范围的描述;可借用高级语言的精巧结构来简化电路的行为和结构;具有电路仿真与验证机制以保证设计准确性;支持电路描述由高层到低层的综合转换;硬件描述与 实现工艺无关(工艺参数可通过语言提供的属性包括进去);便于文档管理;易于理解和设计重用;

Verilog HDL与VHDL的建模能力比较:

一般认为Verilog HDL在系统级抽象方面比VHDL略差一些,而在门级开关电路描述方面比VHDL强得多。

VHDL不具有晶体管开关级模拟设计的描述能力,但对特大型的系统级逻辑电路设计,VHDL较为合适。在底层的VHDL设计环境是由Verilog HDL描述的器件库支持的。

- 系统级(system level):用语言提供的高级结构能够实现系统(待设计模块的外部性能)的模型。

- 算法级(algorithm level):用语言提供的高级结构能够实现算法运行的模型。

- RTL级(register transfer level,寄存器传输级):描述数据在寄存器之间的流动和如何处理、控制这些数据流动的模型。

以上三种属于行为描述,只有RTL级才有与逻辑电路有明确对用关系。

门级(gate level):描述逻辑门与逻辑门之间连接的模型,与逻辑电路有确切的连接关系。

开关级(switch level):描述器件中三极管和存储节点以及它们之间连接的模型。

行为描述/结构描述

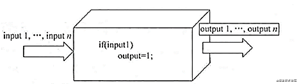

- 行为描述由输入/输出的相应关系来描述,只有电路的功能描述,没有结构描述,也没有具体的硬件示意图。

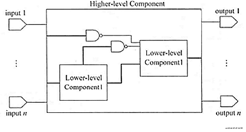

- 结构描述由低等级的元件或基本单元的连接关系来描述,主要关注电路的功能和结构。它设计具体的硬件,便于后续综合。

CPLD/FPGA

- PLD——Programmable Logic Device,可编程逻辑器件

- CPLD——Complex Programmable Logic Device,复杂可编程逻辑器件

- FPGA——Field Programmable Gate Array,现场可编程逻辑门阵列

- PLD最早基于只读存储器(PROM),由固定的与阵列和可编程的或阵列组成,之后也有基于电可擦除只读存储器EEPROM。

- CPLD至少包含三种结构:可编程逻辑宏单元、可编程I/O单元、可编程内部连线。是一种用户根据各自需求而自行构造逻辑功能的数字集成电路。

- FPGA 基于查找表LUT,其本质就是将所有逻辑可能性存入RAM 中;CPLD 基于“与-或”乘积项。

- FPGA采用CMOS-SRAM工艺制成,与门阵列PLD不同,其内部由许多独立的可编程逻辑模块(CLB)组成,逻辑块之间可以灵活地相互连接,CLB功能强大,不仅能够实现逻辑函数,还可以配置成RAM等复杂的形式。配置数据存放在芯片内的SRAM中,可现场修改器件的逻辑功能,即所谓的现场可编程。提供丰富的可编程逻辑资源、易用的存储/运算功能模块和良好的性能,既解决了定制电路的不足,又克服了原有可编程器件门电路数量有限的缺点。

- FPGA 内部构造触发器比例和数量多,更适合时序逻辑设计;CPLD 具有与或门逻辑资源丰富、程序掉电不易失等特点,适合用于设计译码等组合逻辑电路。

- FPGA 的集成度比CPLD 高,具有更复杂的布线结构和逻辑实现。

- CPLD 速度快,具有较大的时间可预测性(连续式布线结构)(CPLD结构提供了非常好的组合逻辑实现能力和片内信号延时可预测性),FPGA 分段式布线。CPLD 保密性好,FPGA 保密性差。在编程上FPGA 具有更大的灵活性。CPLD 通过修改具有固定内连电路的逻辑功能来编程,FPGA 通过改变内部连线的布线来编程。CPLD 功耗大,集成度越高越明显。

最后

以上就是腼腆手链最近收集整理的关于Verilog数字系统设计(夏宇闻)- 绪论笔记C与HDL的全部内容,更多相关Verilog数字系统设计(夏宇闻)-内容请搜索靠谱客的其他文章。

![[EDA] 综合计时系统设计 【VHDL】一、实验要求:二、实验步骤分析:三、核心程序代码、仿真分析四、实验现象:五、部分程序源码:](https://www.shuijiaxian.com/files_image/reation/bcimg16.png)

发表评论 取消回复