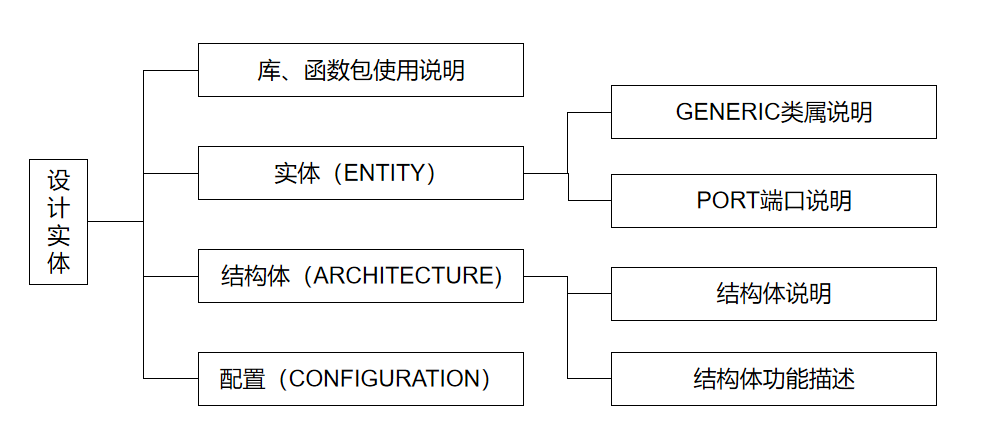

一个相对完整的VHDL程序至少包括实体说明和实体对应的结构体两个基本组成部分。实际上,一个完整的VHDL程序应具有如下所示的比较固定的结构体,包括四个部分。

库、函数包使用说明:用于打开(调用)本设计实体将要用到的库和程序包。

实体说明:描述该设计实体与外界接口信号,是可视部分。

结构体说明:用于描述该设计实体内部工作的逻辑关系,是不可视部分。

配置说明语句:主要用于以层次化方式中对特定的设计实体进行元件例化,或是为实体选定某个特定的结构体。

一、实体

实体(entity)是一个设计实体的表层设计单元,功能是对这个设计实体与外部电路进行接口描述。

1.实体语句结构

entity 实体名 is

[generic(类属表);]

[port(端口表);]

end entity 实体名;实体说明单元必须以语句“entity 实体名 is”开始,以语句“end entity 实体名;”,实体名有设计者命名,用来表示设计电路芯片的名称,也可以作为其他设计调用该设计实体时的名称。

注意:实体名和源程序文件的名字必须一致。

2.类属说明语句

类属(generic)参量是一种端口界面常数,常以一种说明的形式放在实体或块结构体前的说明部分。类属为设计实体和其外部环境通信的静态信息提供通道,特别是用来规定端口的大小、实体中子元件的数目、实体的定时特性等。类属的值可以有设计外部提供。因此,设计者可以从外部通过类属参量的重新设定而容易的改变一个设计实体或一个元件的内部电路结构和规模。

generic (常数名:数据类型[:=设定值];

...

常数名:数据类型[:=设定值]);

例如:

generic(wide:integer:=32);--说明宽度为32位

generic(tph_h1,tph_1h:time:=5ns);--典型延时3.端口说明语句

由端口(port)引导的端口说明语句是对一个设计实体界面的说明。端口为设计实体和外部环境的动态通信提供通道。

port(端口名:端口模式 数据类型;

...

端口号:端口模式 数据类型);(1)端口名

端口名是设计者为实体的每一个对外通道所取的名字。

(2)端口模式

①输入(IN):只读模式,将变量或者信号通过该端口读入。

②输出(OUT):单向幅值模式,将信号通过该端口输出。

③双向(INOUT):信号是双向的,既可以进入实体也可以离开实体。双向模式还可以用于内部反馈。

④缓冲(BUFFER):具有读功能的输出模式,即信号输出到实体外部,但同时也在内部反馈使用。缓冲模式不允许做双向端口使用。

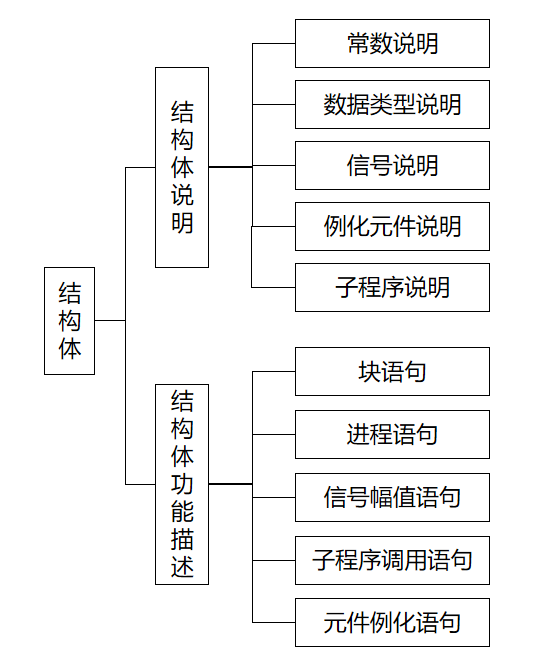

二、结构体

结构体用来描述设计实体的结构和行为,即描述实体的功能,把设计实体的输入和输出之间的联系建立起来。

每个实体可以有多个结构体,每个结构体对应着实体不同结构和算法实现方案。

1.结构体一般语句结构

achitecture 结构体 of 实体名 is

[说明语句]

begin

[功能描述语句]

end achitecture 结构体;2.结构体说明语句

结构体中的说明语句是对结构体的功能描述语句中将要用到的信号(signal)、数据类型(type)、常数(constant)、元件(component)、函数(function)和过程(process)等加以说明的语句。

3.功能描述语句

功能描述语句包括块语句、进程语句、信号幅值语句、子程序语句和元件例化语句。

最后

以上就是背后硬币最近收集整理的关于VHDL语言基本单元及其构成——EDA学习笔记(一)的全部内容,更多相关VHDL语言基本单元及其构成——EDA学习笔记(一)内容请搜索靠谱客的其他文章。

发表评论 取消回复