遵循 Xilinx 建议的复位准则:

a) 尽量少使用复位;

b) 必须复位时采用同步复位;

c) 确保使用高电平有效的复位;

d) 避免异步复位(RAMB 和 DSP48 模块中不支持异步复位)。

1、尽量共用复位、使能等控制信号,以便在综合实现时,寄存器能放在同一个Slice中,充分利用资源。

2、少用复位信号,可使设计在实现时更加灵活,不会被限定在一种实现方法,充分利用资源。

3、FPGA器件寄存器默认值为0,若复位仅用于初始化寄存器,可不使用复位。关于复位更详细的设计可参考

《wp272-Get Smart About Reset_ Think Local, Not Global》。

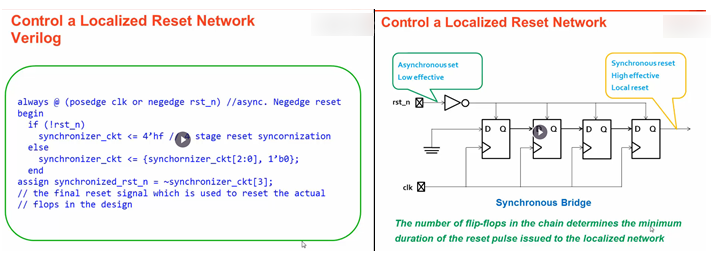

4、当外部给出的复位信号为异步复位时,可通过以下设计转换为同步复位:

(图片来自高亚军老师xinlinx教学视频)

该博客早期写在AET blog上,为方便查看,统一转一份到CSDN。

FPGA设计中的复位-Bryan-电子技术应用-AET-中国科技核心期刊-最丰富的电子设计资源平台

最后

以上就是雪白小天鹅最近收集整理的关于FPGA设计中的复位的全部内容,更多相关FPGA设计中内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复