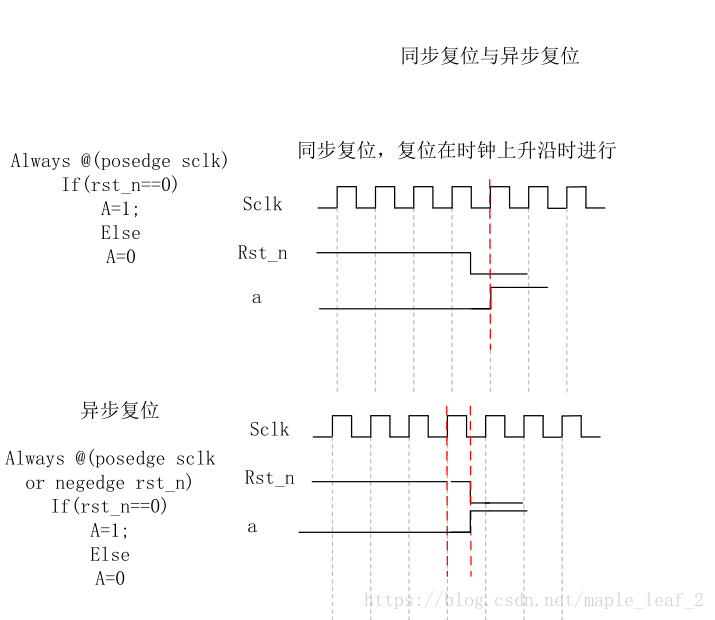

一、同步复位

同步复位 : 复位在时钟上升沿进行(同步可粗略的理解为同步于时钟)

二、异步复位

异步复位 : 复位可以是时钟也可以是复位触发(即使时钟并不在上升沿,但复位信号有效也许复位)

如下图所示为同步复位和异步复位的区别,图一中A的跳变由时钟的上升沿来触发,图二中A的值可由时钟的上升沿和复位的下降沿来触发。

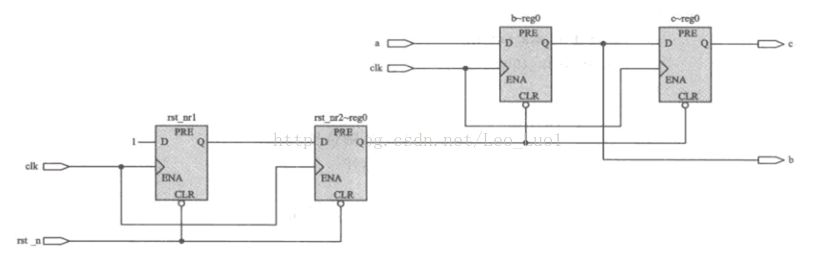

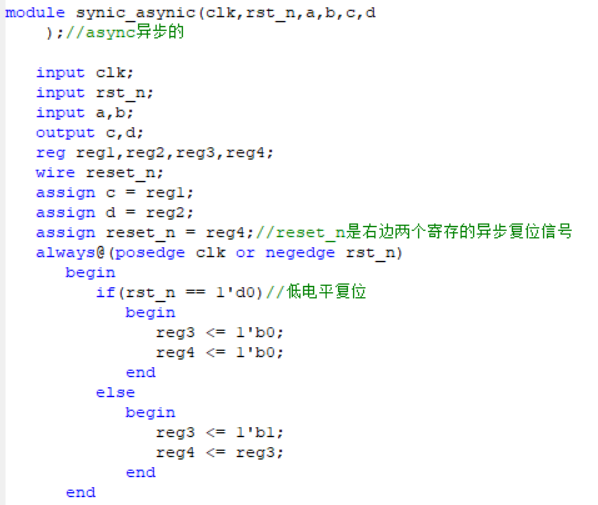

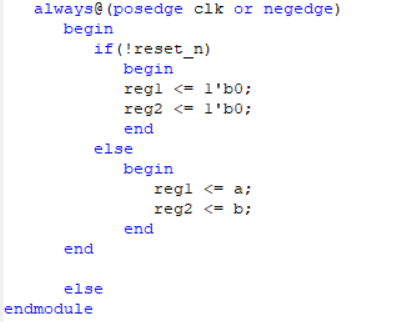

三、异步复位同步释放

异步复位:复位信号不受时钟信号影响——只要是复位有效就能复位(假如约定低电平复位)。也就是说,复位信号不需要和时钟同步。

同步释放:复位信号撤销(释放)的时候,必须跟时钟信号同步,也就是说正好跟时钟同沿。

左边两个寄存器共同作用,可使reg4的输出Q作为右边两个寄存器的异步复位信号。

注:寄存器从左到右依次命名为reg3,reg4,reg1,reg2。a和b分别为reg1、reg2的输入。

reset_n接到两个异步复位寄存器的清零端(CLRN端接低电平的时候寄存器输出端会清零)。当reset_n为0 时,寄存器reg3和寄存器reg4输出为0;由于寄存器reg1和寄存器reg2的CLRN端接到了寄存器reg4的输出端,所以寄存器输出端out_a和out_b会被清零,从而实现复位清零的功能。

第二个always模块的分析:在reset_n由低变高时,第一个时钟周期将VCC输入到左边第一个寄存器(reg3),第二个寄存器(reg2)保持为0,在第二个时钟周期后两个寄存器都变为1,输出端寄存器的清零端为1,跳出复位。

http://www.eda365.com/thread-203680-1-1.html

https://blog.csdn.net/maple_leaf_2/article/details/81353579

https://blog.csdn.net/Leo_Luo1/article/details/72848843

最后

以上就是忧伤狗最近收集整理的关于【verilog】同步复位&异步复位&异步复位同步释放的全部内容,更多相关【verilog】同步复位&异步复位&异步复位同步释放内容请搜索靠谱客的其他文章。

发表评论 取消回复