????????欢迎大家来学习数字电路——JK触发器。

????????在这里我们会讲解JK触发器和集成JK触发器74LS112,希望通过我们的学习会让你更明白数字电路中的奥秘。

目录

????一、JK触发器

????1.JK触发器的组成和逻辑功能

(1)电路结构和图形符号

(2)逻辑功能

????2.集成边沿JK触发器

(1)边沿触发方式

(2)集成JK触发器

一、JK触发器

1.JK触发器的组成和逻辑功能

(1)电路结构和图形符号

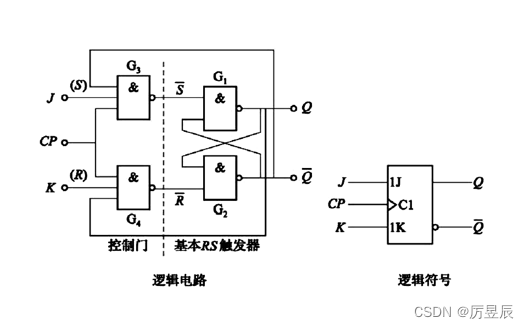

JK触发器是在同步RS触发器的基础上引入两条反馈线构成的。

如图所示:

这样当CP=1、R=S=1时,使=Q、

=

(即

、

不可能同时为0),可以从根本上解决当R=S=1时,触发器输出不确定的问题。将S、R输入端改写成J、K输入端,即为JK触发器。

图形符号中,C1、1J、1K是关联标记,表示1J、1K受C1的控制。

(2)逻辑功能

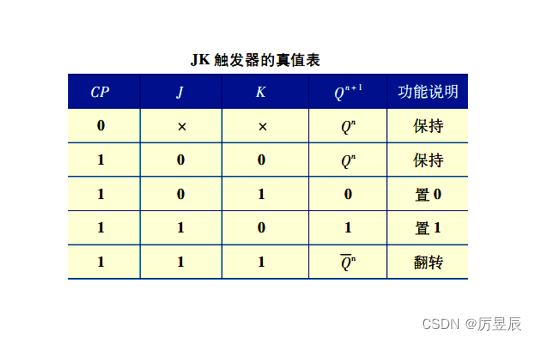

JK触发器不仅可以避免不确定状态,而且增加了触发器的逻辑功能,见表:

由上可知:

在CP=0期间:与非门G3、G4被CP端的低电平关闭,使输入信号不起作用, =

=1,基本RS触发器保持原来状态不变。

在CP=1期间:

①保持功能

当J=K=0时,与非门G3、G4的输出 =1,

=1,触发器保持原来状态不变,即

=

②置0功能

当J=0、K=1时,与非门G3的输出 =1、G4的输出

=

。若触发器原状态为0,则

=1,触发器输出保持原来状态,即输出为0;若触发器原状态为1,则

=0,触发器输出置0。

③置1功能

当J=1、K=0时,与非门G3的输出 =Q、G4的输出

=1。若触发器原状态为0,则

=0,触发器输出置1;若触发器原状态为1,则

=1,触发器输出保持原来状态,输出为1。

④翻转功能(又称为计数功能)

当J=1、K=1时,与非门G3的输出 =Q、G4的输出

=

。若触发器原状态为0,则

=0,

=1,触发器输出置1;若触发器原状态为1,则

=1,

=0,触发器输出置0。也就是触发器的输出总与原状态相反,即

=

。

2.集成边沿JK触发器

(1)边沿触发方式

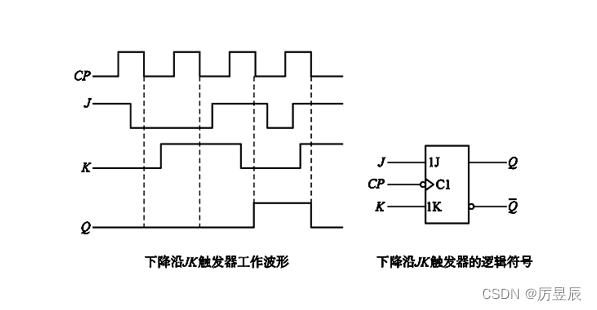

边沿触发是利用与非门之间的传输延迟时间来实现边沿控制,使触发器在CP脉冲上升沿(或下降沿)的瞬间,根据输入信号的状态产生触发器新的输出状态;而在CP=1(或CP=0)的期间,输入信号对触发器的状态均无影响。边沿触发器方式保证了触发器在一个时钟脉冲作用期间只动作一次,有效地克服了触发器“空翻”现象。

CP脉冲上升触发称为正边沿触发,CP脉冲下降沿触发称为负边沿触发。

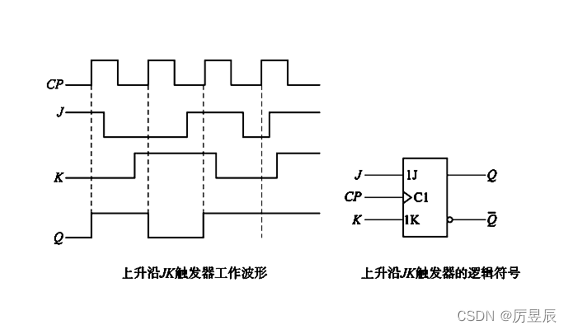

边沿JK触发器的工作波形和图形符号如图所示:

图形符号中下降沿触发器除了用“>”符号外,还在CP引脚上标注小圆圈。

(2)集成JK触发器

①引脚排列和图形符号

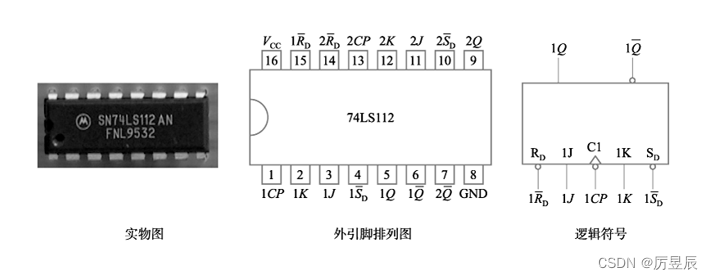

74LS112芯片的实物、引脚排列和图形符号如图所示:

它内含两个下降沿触发的JK触发器, 、

的作用不受CP同步脉冲控制,

称为直接置0端(又称直接复位端)、

称为直接置1端(又称直接置位端),

、

端的小圆圈表示低电平有效。

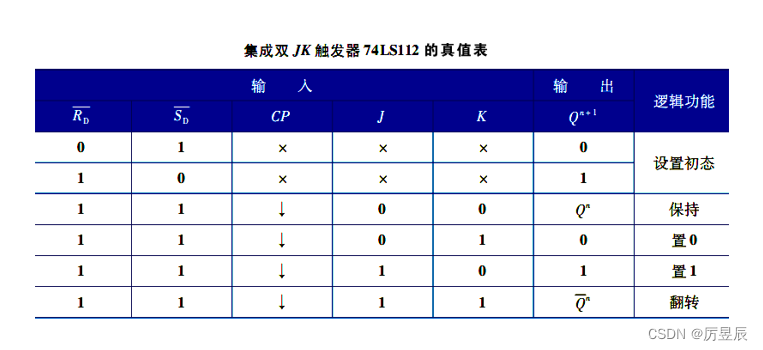

②逻辑功能

下面表格是集成双JK触发器74LS112的逻辑功能表,表中的“↓”表示下降沿触发。

下篇文章我们继续学习D触发器!????????

最后

以上就是大力御姐最近收集整理的关于触发器基础知识(中)的全部内容,更多相关触发器基础知识(中)内容请搜索靠谱客的其他文章。

发表评论 取消回复