一、Purpose

1.利用数字电路的知识,用74LS73或74LS74(即D触发器或JK触发器)和各种逻辑门实现七进制同步加法计数器。

2.锻炼实验操作技能,使之更熟练。

二、Devices

Equipmental Box

ANY LOGICAL GATE

74LS73 (双JK负边沿触发器)

74LS74 (正边沿触发双D型触发器)

三、Requirements

统计输入脉冲的个数,也就是正向计数,从0数到6后输出1,返回0,进入下一个循环。

四、Steps

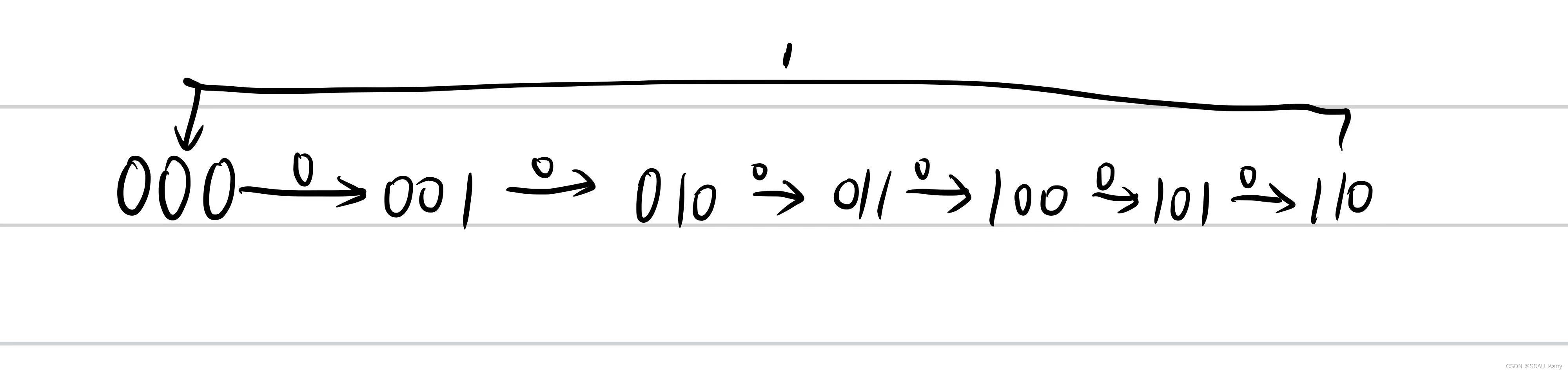

1. 根据需求,画出状态图

2.状态化简——不需化简

3.状态编码——已完成

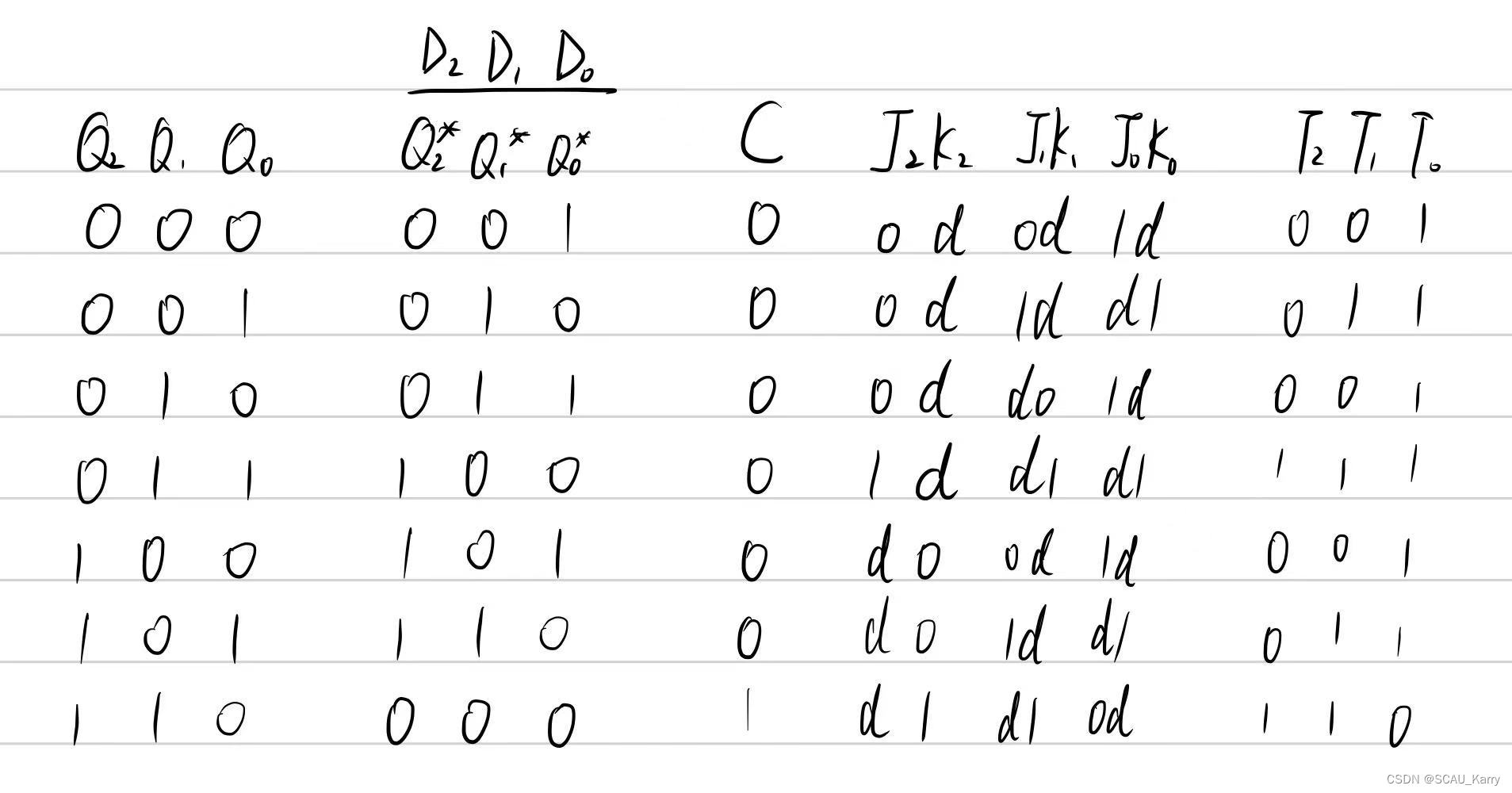

4.输出转换表

5.激励输出表

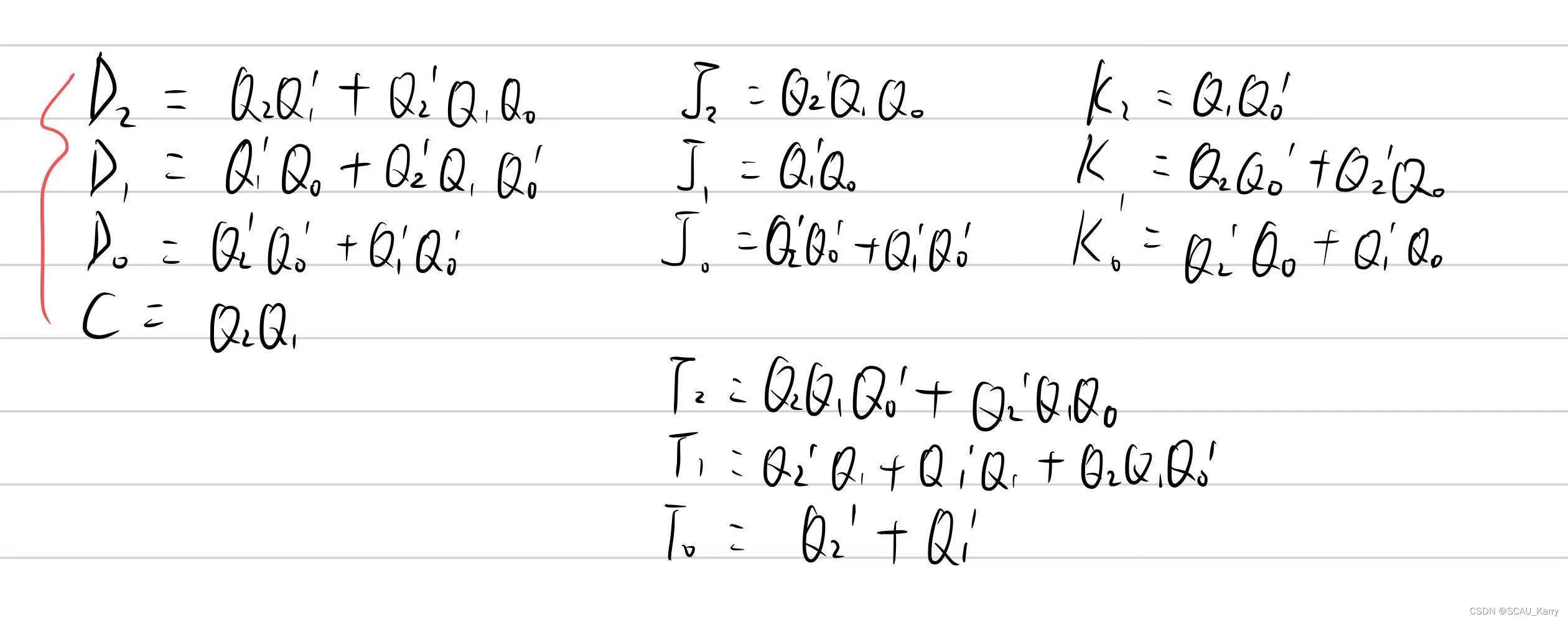

6.激励方程和输出方程

7.检查未使用的状态:发现Q2Q1Q0输出为111的时候,会跳入001状态,输出0,一轮以后能正常进入下一个循环,所以不需要管理。

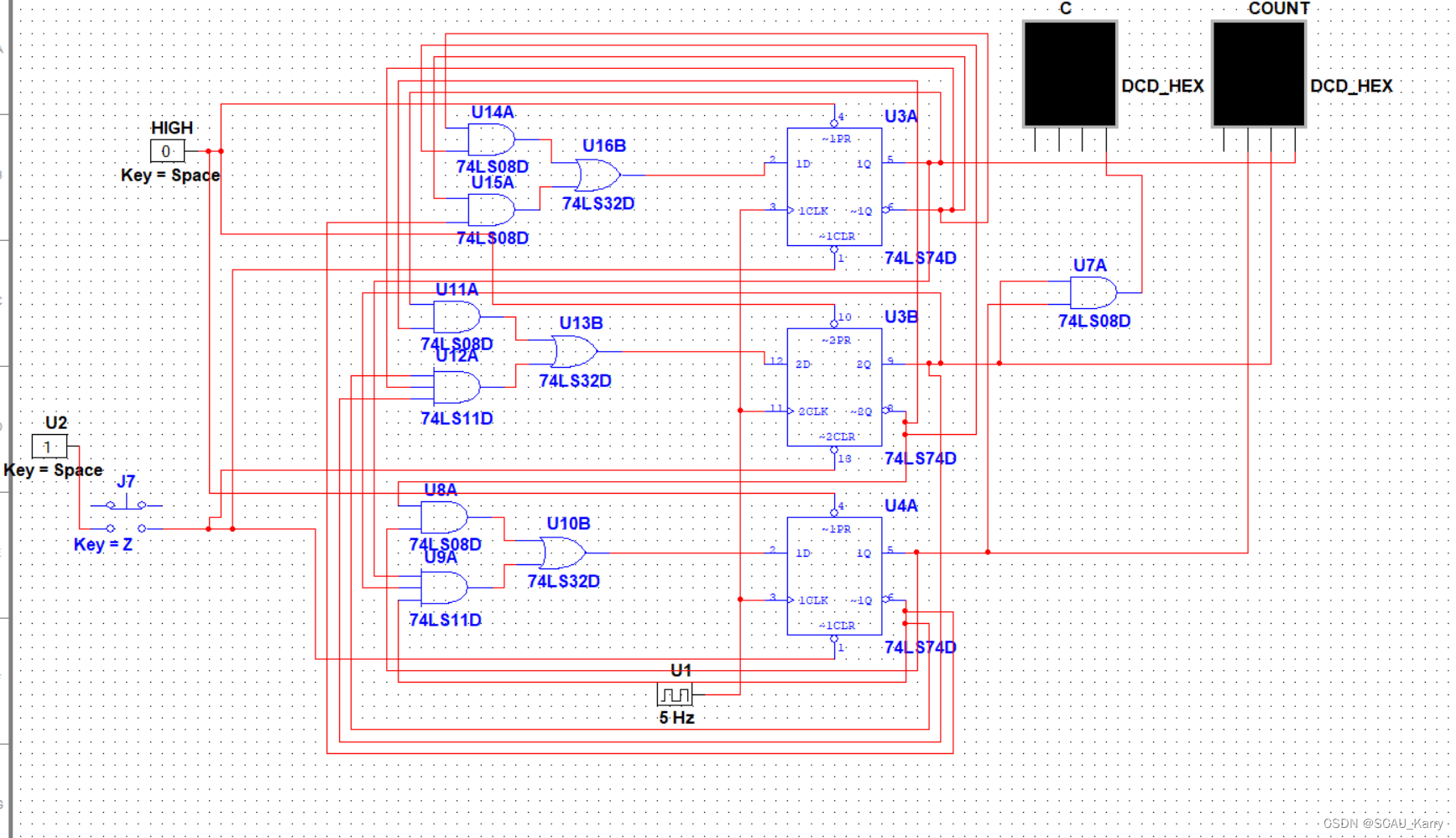

8.电路图-看下图Multisim软件设计图片:

五、Conclusion

1. 通过学习,从得到题目,到分析电路,写出真值表,写出逻辑表达式,化简。很好地回顾了之前学习的内容;

2. 通过做实验,把学习到的理论知识做了实现。既锻炼了动手能力,让课堂生动有趣,增强对理论知识的记忆,同时也增加了对数字电路的兴趣。

3. 反省:实验时应该记住三输入与门的型号。

最后

以上就是美好大碗最近收集整理的关于SCAU华南农业大学-数电实验-七进制同步加法计数器-实验报告的全部内容,更多相关SCAU华南农业大学-数电实验-七进制同步加法计数器-实验报告内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复