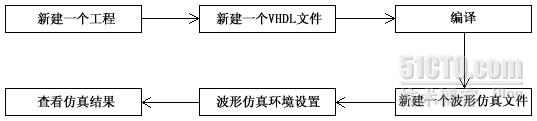

1. 流程

这里我们使用Quartus8.0来做演示

2. 步骤

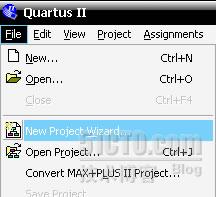

1) 新建一个工程

Ø 新建工程

在D:下新建一个目录,目录名为project

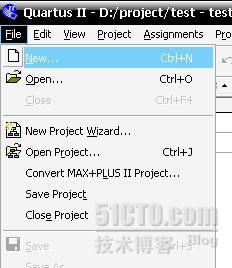

启动Quartus8.0集成开发环境,选择【

File】->【New project Wizard…】

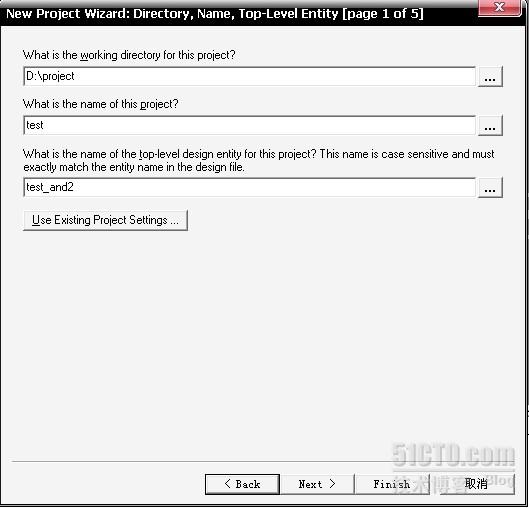

Ø 输入工程信息

输入工程保存目录,工程名为

test。顶层实体名为test_add2

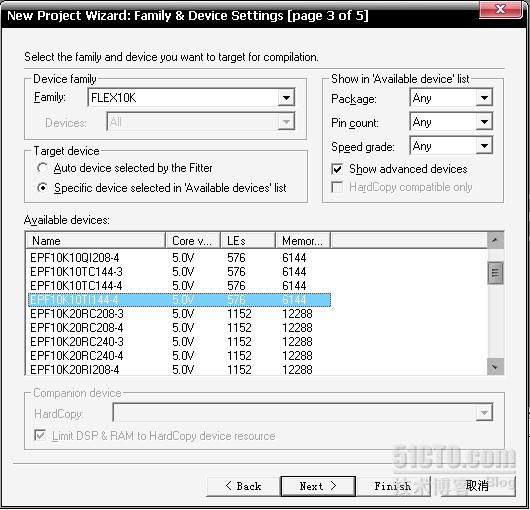

Ø 选择设备类型

根据所使用的不同的试验箱选择不同的器材系列以及型号,这里使用的是FLEX10K系列中的EPF10K10TI144-4的试验箱

Ø 完成

单击“Finish”完成工程文件的建立,可以看到工程框图中已经有所建立的工程了

2) 新建一个VHDL文件

Ø 建立文件

单击【

File】->【New】

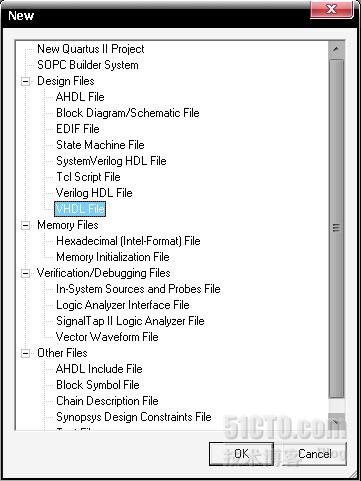

Ø 选择所建文件类型

选择

VHDL文件

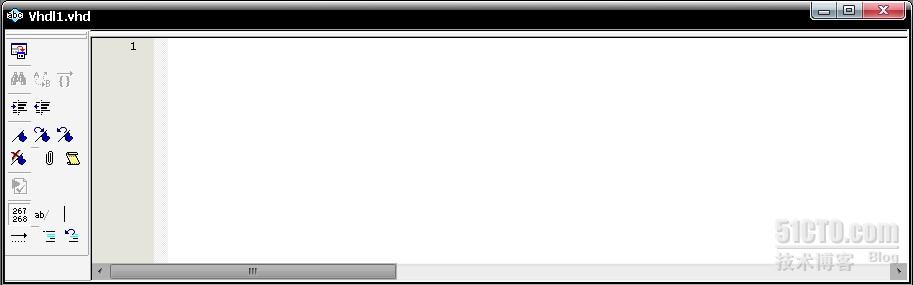

Ø 编写代码

建立好后可以看到所建VHDL文件的编辑框

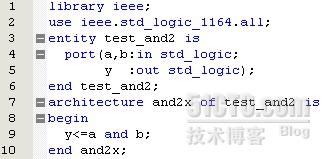

在空白处,输入VHDL语言程序段

第一行:库说明语句

第二行:程序包说明语句

第三到第六行:定义三个实体,a、b为输入,y为输出

第七到第十行:一个结构体,它的功能是与运算,当a、b都为1时,y值为1

Ø 单击“

”保存VHDL文件。

”保存VHDL文件。

”保存VHDL文件。

”保存VHDL文件。

3) 编译

单击“

”编译源程序

”编译源程序

”编译源程序

”编译源程序

编译通过后出现提示框,表示编译成功

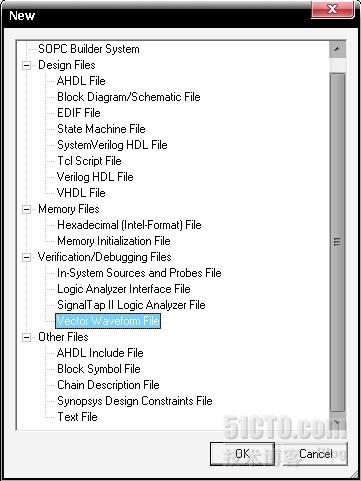

4) 建立一个波形仿真文件

Ø 新建波形仿真文件

单击【

File】->【New】

新建波形仿真文件

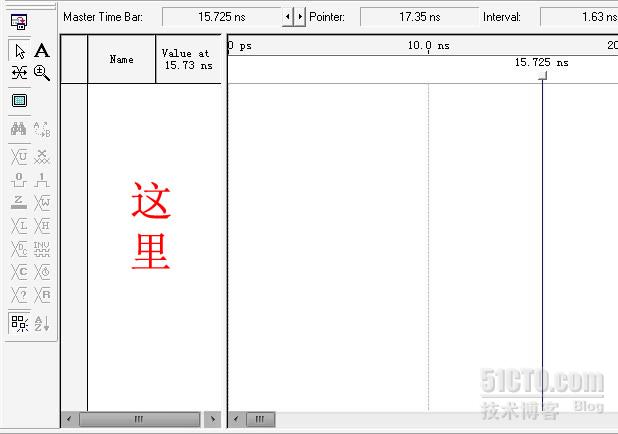

Ø 新建波形图

在图红字处双击鼠标左键

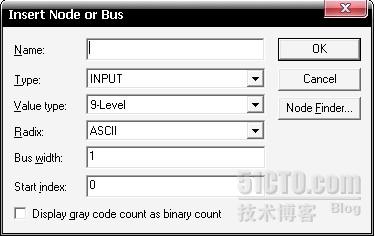

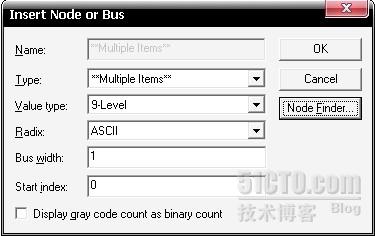

弹出插入节点或总线对话框

Ø 添加端口仿真文件。

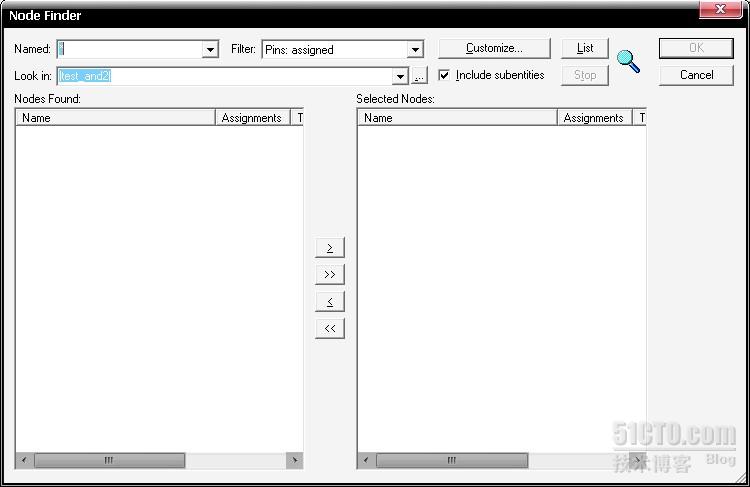

l 单击“Node Finder”按钮

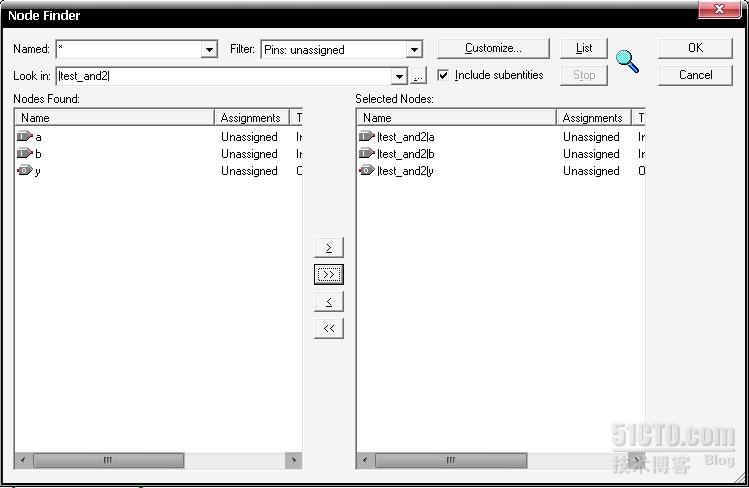

l 查询所有未配置端口

将Filter设置为Pins:unassigned,然后单击List,单击“

”选择所有端口(也可单击“

”选择所有端口(也可单击“

”分别选择),单击OK。

”分别选择),单击OK。

”选择所有端口(也可单击“

”选择所有端口(也可单击“

”分别选择),单击OK。

”分别选择),单击OK。

l 确定选择

单击OK即可

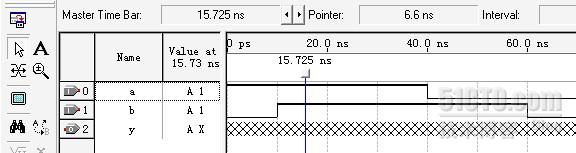

Ø 编辑波形仿真文件

如图编辑波形仿真文件,并保存

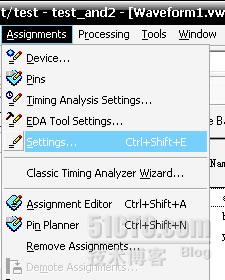

5) 波形仿真环境设置

Ø 打开设置:

选择【

Assignments】->【Setting】或在工程文件上单击右键,选择Setting。

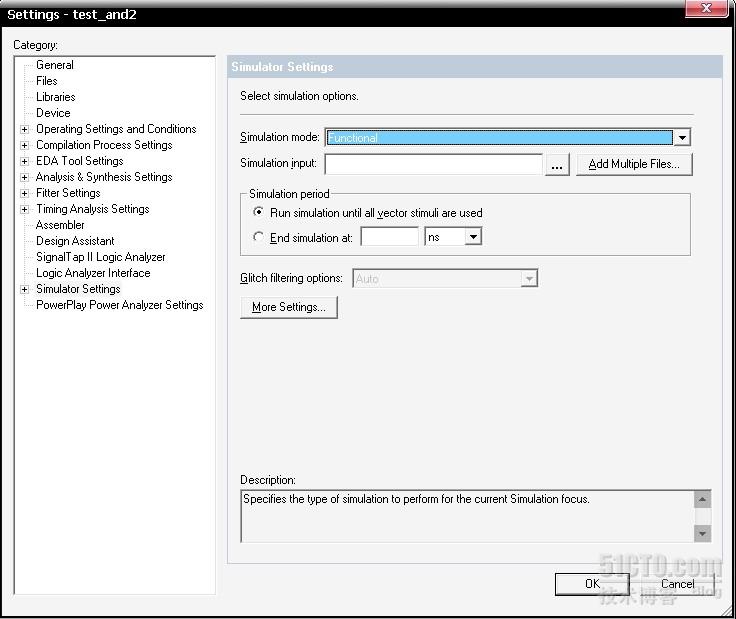

Ø 仿真设置

选择“

simulator setting”,将“simulation mode”改为“Functional”

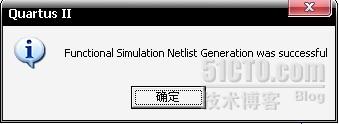

Ø 产生仿真所需的网格

单击【

Processing】->【Generate Functional Simulation Netlist】

Ø 网格产生成功

Ø 单击“

”启动波形仿真。

”启动波形仿真。

”启动波形仿真。

”启动波形仿真。

6) 查看波形仿真结果

查看波形仿真结果,根据所写的程序,当a,b都为1时y值为1,由仿真图可以看出结果是正确的

转载于:https://blog.51cto.com/huobumingbai/351530

最后

以上就是包容电话最近收集整理的关于VHDL之Quartus简介的全部内容,更多相关VHDL之Quartus简介内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复