硬件中断线中断

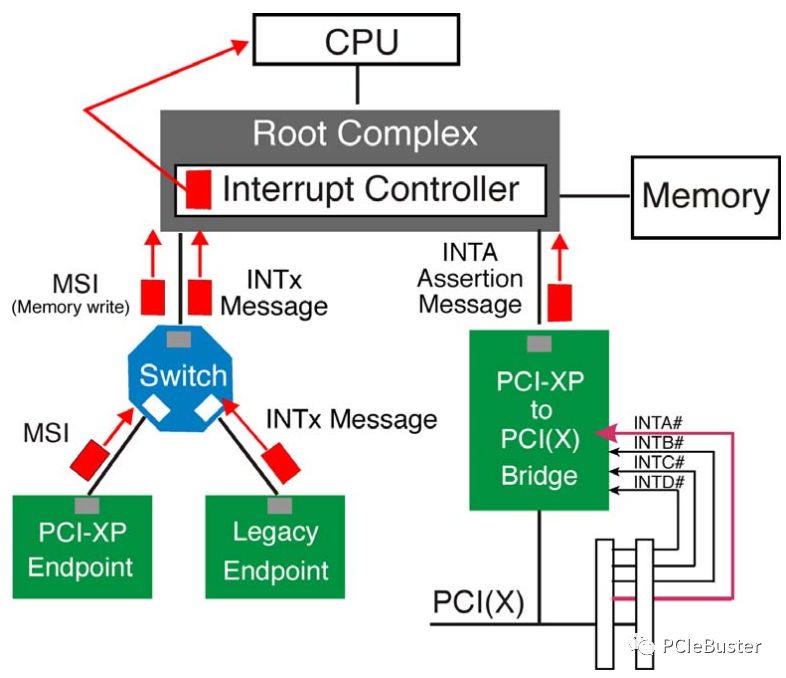

早期PCI时代,PCI设备的中断使用的是传统中断,也就是基于硬件中断线(INTx,每个设备有四条INTAINTBINTCINTD)来向中断控制器(IO APIC)报告中断的产生。这个中断是多个设备(功能)共享的。中断产生后,系统中断服务程序再来轮询具体是哪个设备产生了中断。这显然很低效。

MSI(Message SignaledInterrupt)中断

PCI协议2.2引入了一个新的中断处理方式,即MSI(Message SignaledInterrupt)。有中断产生时在系统特定内存地址写入中断数据已通知CPU一个中断。该种方式脱离了中断引脚(PIN)带来的数目限制,并且延迟小、效率高。

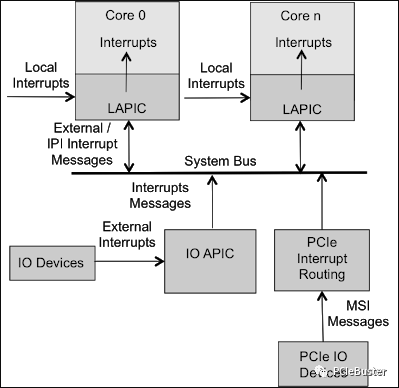

当设备准备引发中断时,它将向LAPIC(Local Advanced Programmable Interrupt Controller)发送一条MSI消息,(注意:这个消息不要和PCIe协议里面的读写事务的消息混淆了,MSI的消息发送本质是memory write事务)该消息包含有关目标LAPIC和中断向量编号的信息。一旦LAPIC收到消息,它就会将其发送到响应的CPU Core进行中断处理。

设备怎么知道发送什么消息内容到哪个地址去呢?

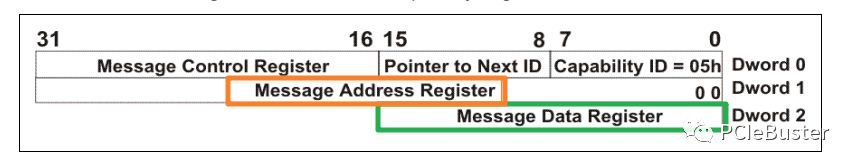

MSI消息内容(Message Data)最初由系统OS配置,写入到PCI/PCIe设备的消息数据寄存器Message Data Register中。消息将要发送的地址(Message Address),也由OS配置,写入到对应PCI/PCIe设备的消息地址寄存器Message Address Register中。

消息的地址和内容具体是什么?

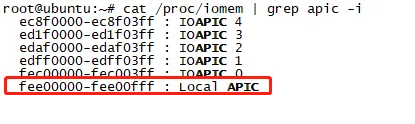

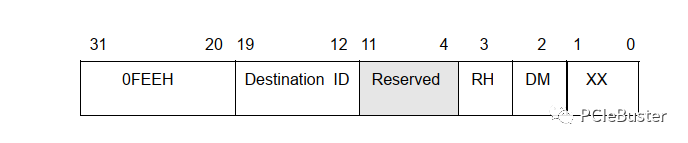

在X86系统下,message address对应的LAPIC的地址。

发往0FEEXXXX都会触发CPU的中断消息。

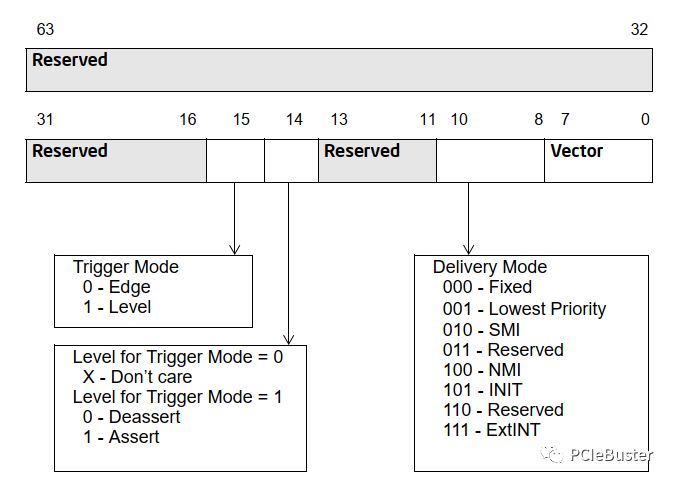

发送的具体数据格式如下,bit7-0即为中断向量编号:

注意,上面都是以X86为例,具体的可以参考《Intel® 64 and IA-32 Architectures Software Developer’s Manual》卷三关于APIC和MSI的部分。

MSI-X跟MSI类似,只是每个设备可以发送更多的中断。而且,MSI-X的Message Address和 Message Data并不存放在PCI/PCIe设备的寄存器中。而是存放在PCIe设备的BAR空间中。

最后

以上就是机灵可乐最近收集整理的关于PCIE的中断硬件中断线中断和MSI中断(一) 硬件中断线中断MSI(Message SignaledInterrupt)中断的全部内容,更多相关PCIE的中断硬件中断线中断和MSI中断(一) 硬件中断线中断MSI(Message内容请搜索靠谱客的其他文章。

发表评论 取消回复