初次使用FPGA硬件编程编程语言Verilog编写HDL程序01

初次使用FPGA硬件编程编程语言Verilog编写HDL程序02

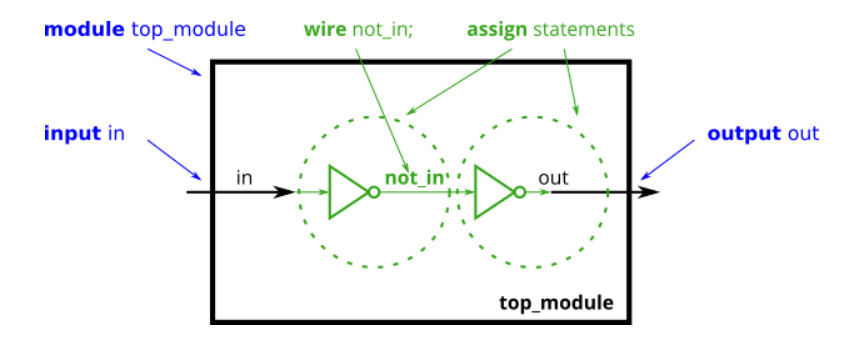

1、案例:声明电线

随着电路变得越来越复杂,您将需要电线将内部组件连接在一起。当你需要使用连线时,你应该在模块的主体中声明它,在它第一次使用之前的某个地方。

module top_module (

input in, // 声明输入线 in

output out // 声明输出线 out

);

wire not_in; // 声明线 not_in

assign out = ~not_in; // 定义变量out接收not_in非值

assign not_in = ~in; // 定义变量not_in接收in的非值

endmodule

关键字: wire

`default_nettype none

`default_nettype none

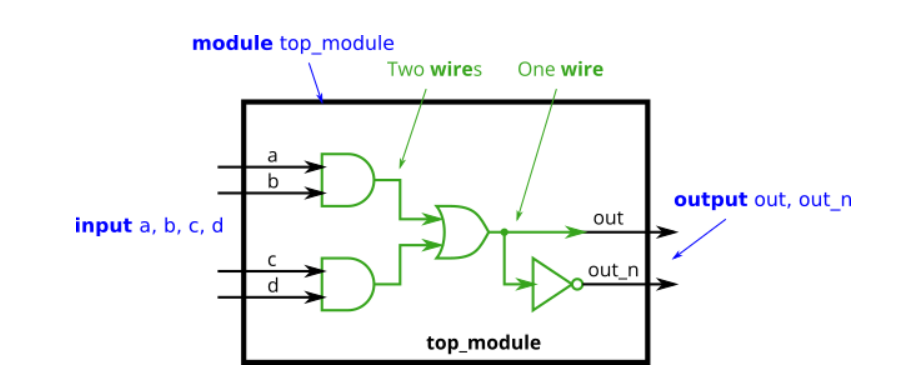

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n );

wire and_in_ab = a && b; // 与门

wire and_in_cd = c && d; // 与门

wire nor_abcd = !(and_in_ab || and_in_cd); // 或非门

assign out = !nor_abcd;

assign out_n = nor_abcd; // 非门

endmodule

讲解 :verilog HDL中wire和reg的区别

wire表示直通,即输入有变化,输出马上无条件地反映(如与、非门的简单连接)。

reg表示一定要有触发,输出才会反映输入的状态。

reg相当于存储单元,wire相当于物理连线。

reg表示一定要有触发,没有输入的时候可以保持原来的值,但不直接实际的硬件电路对应。

两者的区别是:寄存器型数据保持最后一次的赋值,而线型数据需要持续的驱动。wire使用在连续赋值语句中,而reg使用在过程赋值语句(initial ,always)中。wire若无驱动器连接,其值为z,reg默认初始值为不定值 x 。

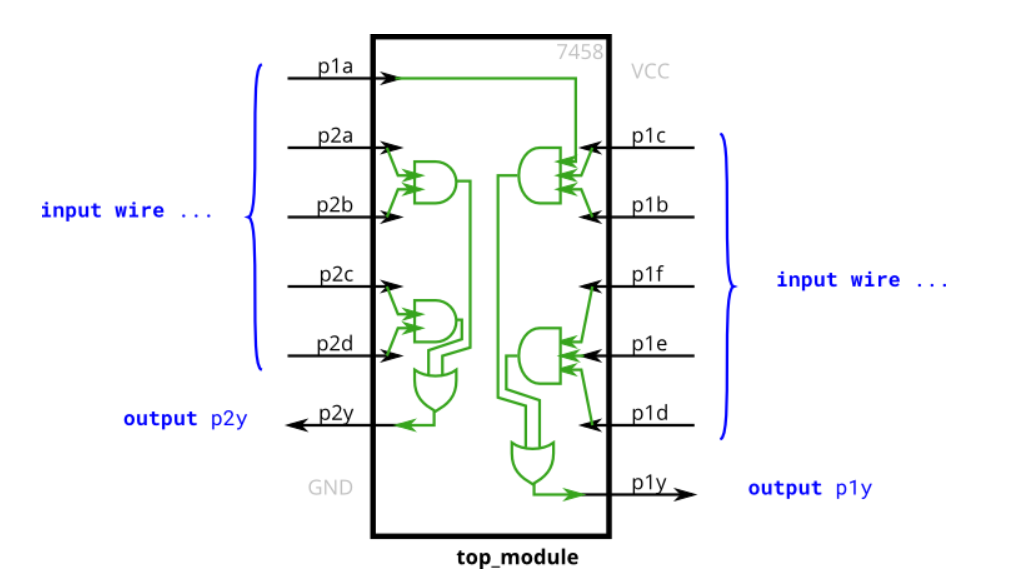

2、7458芯片

创建一个与 7458 芯片功能相同的模块。它有 10 个输入和 2 个输出。您可以选择使用assign语句来驱动每条输出线,或者您可以选择声明(四)条线用作中间信号,其中每条内部线由一个与门的输出驱动。(需要用一个值驱动两个信号 p1y和p2y。)

module top_module (

input p1a, p1b, p1c, p1d, p1e, p1f,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

wire in_ab,in_cd,in_acb,in_def;

assign in_ab = p2a && p2b;

assign in_cd = p2c && p2d;

assign in_acb = p1a && p1c && p1b;

assign in_def = p1f && p1d && p1e;

assign p2y = in_ab || in_cd;

assign p1y = in_acb || in_def;

endmodule

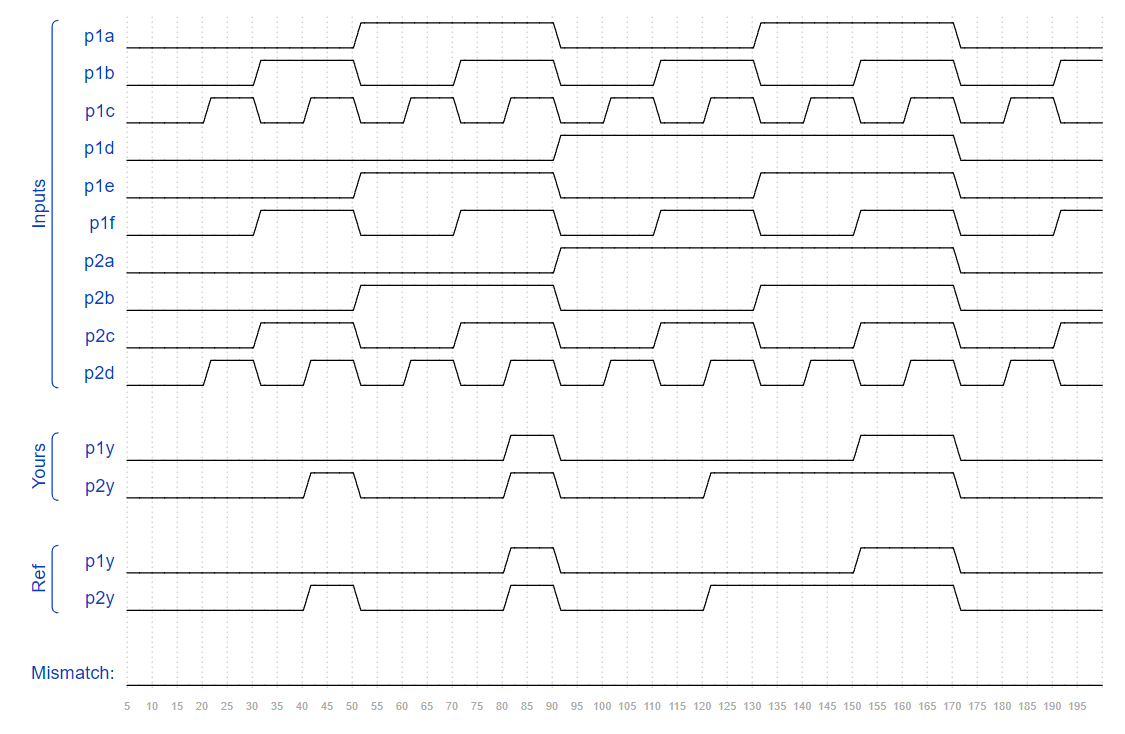

时序图:

最后

以上就是发嗲彩虹最近收集整理的关于【FPGA学习笔记】初次使用FPGA硬件编程编程语言Verilog编写HDL程序03的全部内容,更多相关【FPGA学习笔记】初次使用FPGA硬件编程编程语言Verilog编写HDL程序03内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复