一、概述

先介绍四个最基本的类型:reg、wire、integer、parameter;除了这四个之外,还有其他诸多类型可参考夏宇闻的Verilog数字系统设计第二版,这些数据类型除了time外都和基本逻辑单元库有关,该库是由半导体厂家和EDA工具厂家共同提供的。

二、常量

-

数字类型:

整数: 二、八、十、十六进制

x和z: x表不定态,z表高阻态还可以用?来表达,在case语句中建议用?写法来提高程序可读性

负数: 比如-8’d5

下划线: 比如:8’b000_0001以此提高可读性 -

参数(parameter)类型:

用来定义常量的,通过一个标识符来代表一个常量,例如: parameter A = 3’b001; 那么在这个module中A的值就代表二进制001; -

变量

wire/tri: wire通常使用assign语句实现(组合逻辑的描述),定义的方式:例如wire [3:0] state; 即wire型变量state的为位宽是4位。

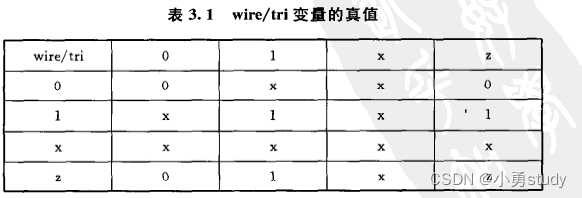

关于wire/tri真值表如下:

reg: 寄存器数据类型变量的关键字,reg型数据通常在always块中使用,定义方式和wire的一致。注:reg型数据默认初始值是不定值。如果reg值是一个无符号数,即该数的本身,若是有符号的话则认为是其补码+1,例如一个reg型数据被赋值为4,那么就是4,如果被赋值为-1,那么在运算时被认为是+15。

memory: 类似于C语言中的数组,可用来对存储器建模,如:RAM、ROM等。定义方式如:reg [7:0] mema [255:0],定义了一个mema存储器,存入的数据位宽是8bit,存储器的深度是256。索引的方式如:mema[3]=0,即对存储器mema的第三个单元进行操作。

最后

以上就是昏睡冷风最近收集整理的关于Verilog基础语法--数据类型【常用的几种】的全部内容,更多相关Verilog基础语法--数据类型【常用内容请搜索靠谱客的其他文章。

如何使用integer型別? (IC Design) (Verilog)](https://www.shuijiaxian.com/files_image/reation/bcimg1.png)

发表评论 取消回复