Verilog小知识点

1. integer可以截位

整数类型用关键字integer来声明,声明时不用指明位宽,位宽和编译器有关,一般为32bit。reg型变量为无符号数,而integer型变量为有符号数,也就是说integer可以声明为负数,就像integer=-10。所以本质上integer是可以截位的,以下代码证明了这一点。

`timescale 1ns / 1ps

module test_integer;

reg [3:0] a;

integer i = 8'b11010100;

initial

begin

a = i[5:2];

end

endmodule

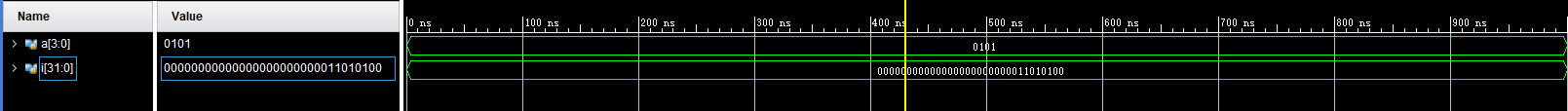

上面的文件直接保存为仿真文件,可以在vivado中直接仿真,其仿真波形图如下所示。

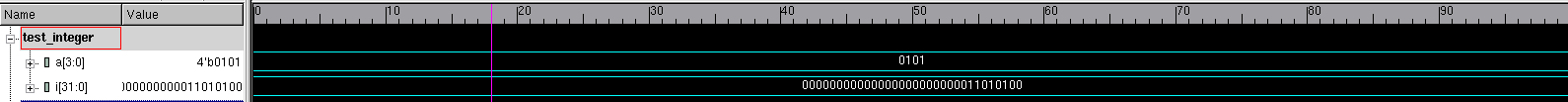

由上图可知,该程序成功对整数类型i进行了截取。

同理,以上程序也可以放在vcs平台进行仿真,其仿真程序如下所示。

`timescale 1ns / 1ns

module test_integer;

reg [3:0] a;

integer i = 8'b11010100;

initial

begin

a = i[5:2];

end

initial begin

#100 $finish;

end

endmodule

编译指令为:

vcs test_integer.v -debug_all

打开图形界面指令为:

./simv -gui

仿真波形如下图所示:

最后

以上就是飘逸汽车最近收集整理的关于Verilog小知识点Verilog小知识点的全部内容,更多相关Verilog小知识点Verilog小知识点内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

如何使用integer型別? (IC Design) (Verilog)](https://www.shuijiaxian.com/files_image/reation/bcimg1.png)

发表评论 取消回复