一、什么是PN码?PN码有什么用处?

1、 什么是PN码

PN码的英文名字叫Pseudo-Noise Code,(pseudo:adj.伪; 假的),直译过来就是伪噪声码,这里噪声主要是想表达随机的意思。其中最重要的一种PN序列叫m序列(全称叫最长线性反馈移位寄存器序列),说它重要主要是研究得早,理论成熟,用得多。

其本质上就是一串周期性的随机数,周期是由移位寄存器的位数决定的,序列是由生成多项式(有的地方叫本原多项式、反馈系数)决定的。这意味着,对于掌握了长度和生成多项式的人来说,这段序列就是确知的,对于不知道长度和生成多项式的人来说,就是随机的,不可捉摸的(或者说解密代价极大的)。

2、PN码有什么用处

PN码一般用在扩频通信里面,另外有扰码、测量延时和距离、测量误码率、数据加密等用途。

二、如何生成m序列?m序列有什么性质?生成多项式怎么设置?

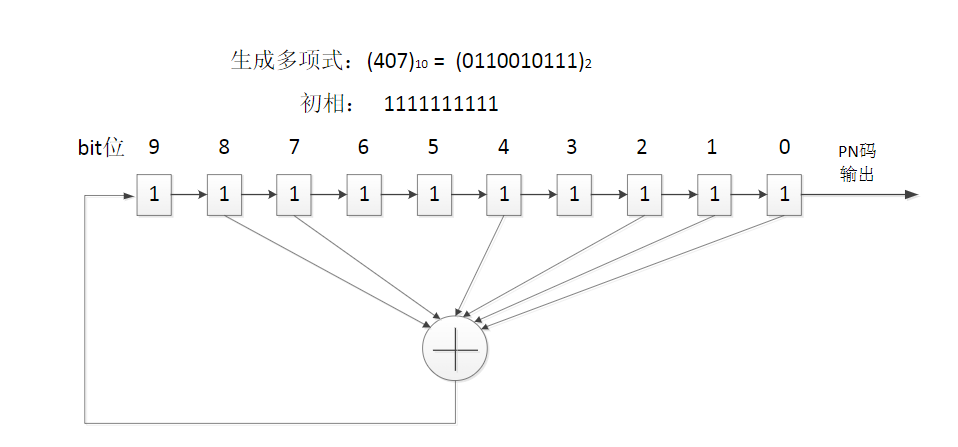

1、如何生成PN码

2、m序列的性质:

- 均衡性:0、1各占一半,1比0多一个;

- 游程特性:就是说连0段或连1段的,长度为1的约占1/2,长度为2的约占1/4,长度为3的约占1/8,按照三位m序列想一下就能想明白;

- 移位相加性:自己+下一个时钟的自己,等于另外一个移位序列;

- 相关函数: R ( τ ) = { 1 , if τ = 0 − 1 / L , if τ = 1 R(tau) =begin{cases} 1, & text{if } tau = 0 \-1/L, & text{if }tau = 1end{cases} R(τ)={1,−1/L,if τ=0if τ=1。

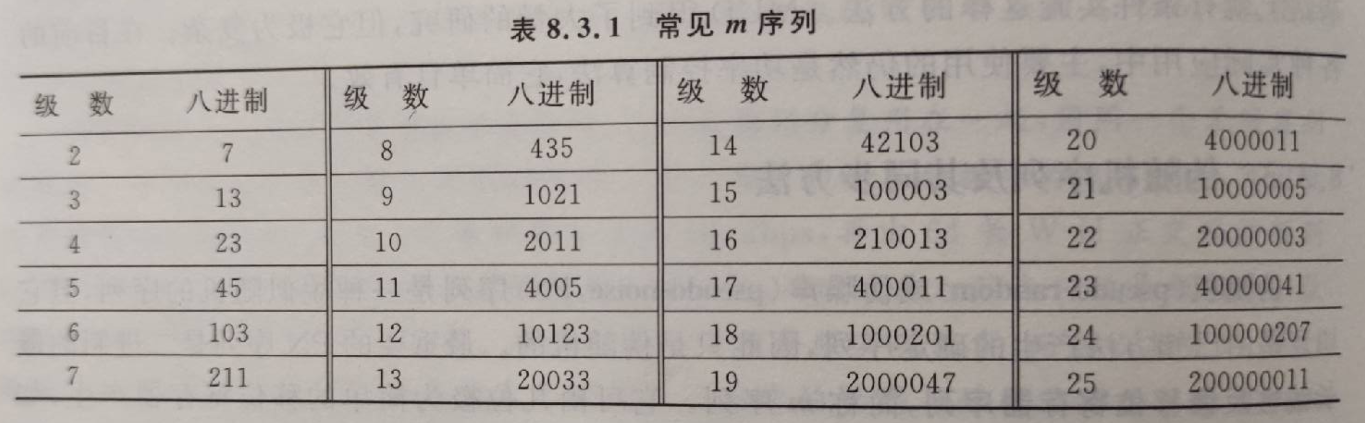

3、生成多项式怎么设置?

这项工作交给搞理论研究的数学家就行了,不按这个来的话m序列的性质就会出问题,如果想深究这种东西话,可以看下这篇博客:m序列产生原理的是什么?m序列的产生与本原多项式

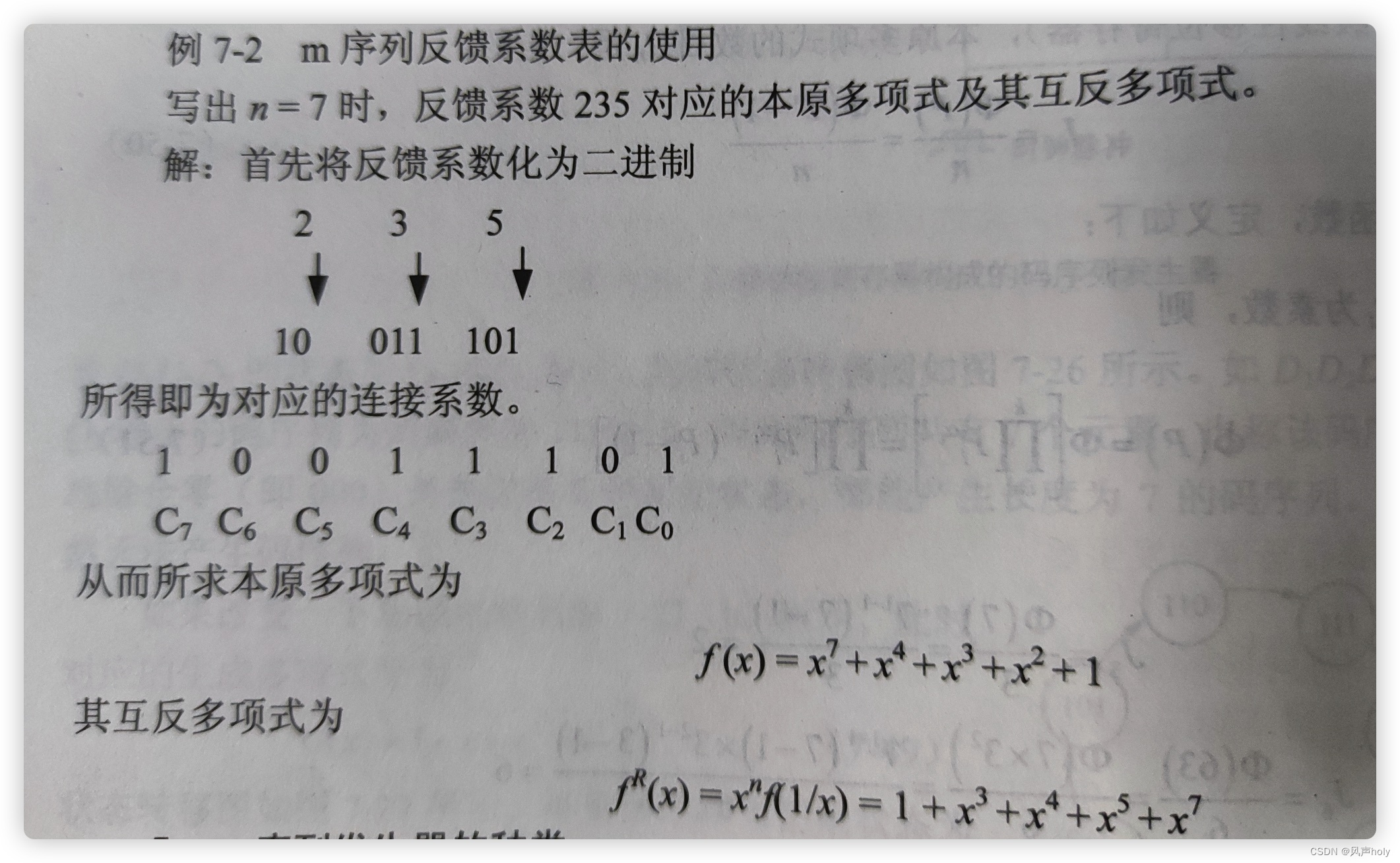

4、常见m序列表格的使用方法

需要注意的就是LSB(最低有效位)对应的是C0(模二加后的反馈输入)

四、如何用FPGA来实现?

话不多说,直接上代码:

module PN_1023_gen_1 (sysclk,reset,pnclk,

pnxs1_allone,pnxs1_code,

pnclkpos);

input sysclk,reset,pnclk;//系统钟,高电平复位,码钟

output pnxs1_allone,pnxs1_code; //allone是周期重复指示(因为这里初相是1023嘛),后面一个是输出的m码序列,

reg pnxs1_allone,pnxs1_code;

output pnclkpos;//相当于一个使能信号,也可用来做stp的触发信号

wire pnclkpos;

reg [9:0] gxs1regshift;

wire polyvalgxs1;

reg [9:0] gxs1_counter;

reg [1:0] tempa,tempb;

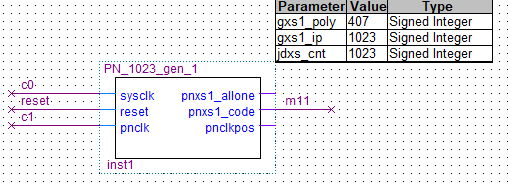

parameter gxs1_poly = 407;

parameter gxs1_ip = 1023;

parameter jdxs_cnt = 1023;

/*-------------------------------------code clk gen---------------------------*/

always @(posedge sysclk)

begin

if(reset)

begin

tempb<=2'd0;

end

else

begin

tempb<={ tempb[0],pnclk };

end

end

assign pnclkpos=( tempb[0] & ~tempb[1] );//边缘检测方法

/*-----------------------------------------short(1023) code gen------------------*/

assign polyvalgxs1=^(gxs1_poly & gxs1regshift);

always @(posedge sysclk)

begin

if(reset)

begin

gxs1regshift<=gxs1_ip;

gxs1_counter<=0;

end

else

begin

if(pnclkpos)

begin

if(gxs1_counter < jdxs_cnt-1)

begin

gxs1regshift<={polyvalgxs1,gxs1regshift[9:1]};

gxs1_counter<=gxs1_counter+18'd1;

end

else

begin

gxs1regshift<=gxs1_ip;

gxs1_counter<=0;

end

end

else

begin

gxs1regshift<=gxs1regshift;

gxs1_counter<=gxs1_counter;

end

end

end

always @(posedge sysclk)

begin

if(reset)

begin

pnxs1_code<=0;

pnxs1_allone<=1;

end

else

begin

pnxs1_code<=gxs1regshift[0];//每经过一个码钟,gxs1regshift序列才移位一次,所以要传重复的值十次

pnxs1_allone<=(gxs1regshift==gxs1_ip);

end

end

endmodule

产生好的模块长这样:

五、m序列的存在的问题及改进方法

- 存在的问题:

- 周期相同的m序列可用的生成多项式少,比如L=1023的生成多项式只有60个,这就意味着解密所付出的代价还不够大

- 互相关系数大,这会导致m序列直接用作扩频码时会产生严重的多址干扰(MAI)

- 解决方法:gold序列

gold序列就是将两个能组成优选对的m序列的输出结果进行模二加。gold序列能同时解决上述两个问题。

六、产生gold序列的工程文件

这附一个产生gold序列的工程文件,两块钱就能直接下载,也可以在评论里留下联系方式,我看见了就私发给你。

注意一下,这个工程文件用到的quartus是13.1版,FPGA是EP4CE115F29C7,如果版本不对的话,下载的工程文件可能没法用。但里面涉及到的pll模块、按键复位模块、gold码生成模块都是可以直接用的

下载链接:

https://download.csdn.net/download/weixin_45827703/58007033

最后

以上就是虚心背包最近收集整理的关于m序列生成方法及其fpga实现的全部内容,更多相关m序列生成方法及其fpga实现内容请搜索靠谱客的其他文章。

发表评论 取消回复