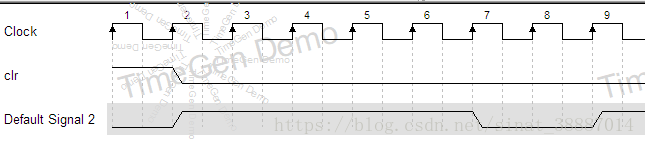

今天突发奇想,比如我要得到上图所示的,高电平占7个CLK,低电平占2个CLK的输出方波。

设置个计数的寄存器,当计数值小于高电平持续时间时,输出高电平,当高于高电平持续时间小于总周期时,输出低电平。

程序如下:

module fenpinqi_buduicheng (clk, clr, q);

input clk;

input clr;

output reg q;

parameter high = 5, low = 2;

reg [3:0] count;

always @ (posedge clk)

begin

if (clr == 1)

begin

q <= 0;

count <= 1'b0;

end

if (clr == 0)

begin

if (count < high)

begin

count <= count+1'b1;

q <= 1;

end

if (count >= high)

begin

count <= count+1'b1;

q <= 0;

end

if (count == high+low-1)

begin

q <= 0;

count <= 1'b0;

end

end

end

endmodule

注意,count因为要计数到high+low-1,所以要注意reg的大小,我刚开始没有设置,默认为一位reg,导致计数值在0-1之间变化,所以输出一直是高电平。

最后

以上就是缥缈砖头最近收集整理的关于verilog实现一种任意占空比方波产生的全部内容,更多相关verilog实现一种任意占空比方波产生内容请搜索靠谱客的其他文章。

发表评论 取消回复