50m 分频器设计——50MHZ(含verilog程序)

分频器设计

一、实验目的

1、熟悉分频器的原理;

2、掌握采用Verilog HDL语言设计分频器的方法;

3、进一步学习利用VerilogHDL语言进行层次设计的方法。(wWW.niubb.NeT)

二、实验内容

1、采用Verilog语言设计一个十分频器,记录Verilog程序;

2、对十分频器进行功能仿真,观察仿真波形;

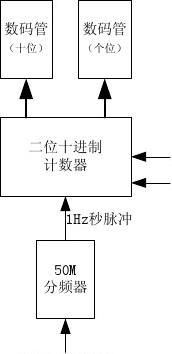

3、仿真没有问题后,将分频比改为50000000,实现一个50M分频器。利用此分频器和开发板上的50MHz时钟信号,得到1Hz的秒脉冲信号,完成如图1-2.28所示的秒计数器。

50m 分频器设计——50MHZ(含verilog程序)

(拨码开关)

程序设计如下:

module fenp(clk_out,clk_in,reset);

output clk_out;

input clk_in;

input reset;

reg cnt;

reg clk_out;

50m 分频器设计——50MHZ(含verilog程序)

always@(posedge clk_in or posedge reset) begin

if(reset)

begin

cnt<=0;

clk_out<=0;

end

else

begin

if(cnt==24999999)

begin

clk_out<=!clk_out;

cnt<=0;

end

else

cnt<=cnt+1;

end

end

endmodule

本程序经验证,完全可以实现实验要求 。(WwW.niubb.Net)文章来自某大学EDA实验课

50m 分频器设计——50MHZ(含verilog程序)[wWW.NIUBB.NEt]

50m 分频器设计——50MHZ(含verilog程序)

免责申明:本栏目所发资料信息部分来自网络,仅供大家学习、交流。我们尊重原创作者和单位,支持正版。若本文侵犯了您的权益,请直接点击提交联系我们,立刻删除!

最后

以上就是尊敬高山最近收集整理的关于verilog将100mhz分频为1hz_50m 分频器设计——50MHZ(含verilog程序)的全部内容,更多相关verilog将100mhz分频为1hz_50m内容请搜索靠谱客的其他文章。

发表评论 取消回复