最近使用FPGA的串口与串口WIFI通信,本文用于记录分析过程及关键点。

1、原理分析

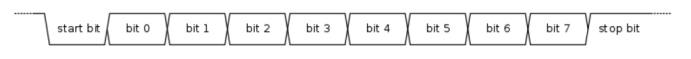

上图为一个字节的UART传输,注意以下几个关键点:

1)起始信号

当检测到下降沿的时候,开始传输

2)传输的位数

一个字节需要8位还没有加上检验位

3)停止信号

一个字节的传输完成,需要拉高,该信号的目的是告诉接收端,我已经发送完成一个字节。您可以接收了。

2、 代码分析

1)由于是串口发送8位数据,所以需要一个always函数将数据发出去。

always @( posedge sys_clk or negedge sys_rst_n ) begin

if (! sys_rst_n)

uart_txd <= 1'b1;

else if ( tx_flag)

case (tx_cnt)

4'd0: uart_txd <= 1'b0; //起始位为低电平

4'd1: uart_txd <= tx_data[0];

4'd2: uart_txd <= tx_data[1];

4'd3: uart_txd <= tx_data[2];

4'd4: uart_txd <= tx_data[3];

4'd5: uart_txd <= tx_data[4];

4'd6: uart_txd <= tx_data[5];

4'd7: uart_txd <= tx_data[6];

4'd8: uart_txd <= tx_data[7];

4'd9: uart_txd <= 1'b1; //停止位为高电平

end

上面的代码其中有两个标志位:

tx_flag 用于记录状态,

当 tx_flag == 1; 处于发送状态

当 tx_flag == 0; 处于停止发送状态

tx_cnt 用于记录发送的位数,

tx_cnt 在0~9之间不断循环,如果想改变发送的字节,那么在tx_cnt == 9的时候,就更改tx_data的值

2)tx_cnt 的设计

always @(posedge sys_clk or negedge sys_rst_n ) begin

if (! sys_rst_n) begin

clk_cnt <= 16'd0;

tx_cnt <= 4'd0; end

else if (tx_flag) begin

if (clk_cnt < BPS_CNT - 1) begin // BPS_CNT 为一个波特率周期,需要计数的值

clk_cnt <= clk_cnt + 1'b1;

tx_cnt <= tx_cnt; end

else begin

clk_cnt <= 16'd0;

tx_cnt <= tx_cnt + 1'b1;end

else begin

clk_cnt <= 16'd0;

tx_cnt <= 4'd0;end

end

end

上面的程序是经典的外部循环和内部循环,clk_cnt 计数一周期,tx_cnt 才递加1。

上面的程序依然很依赖tx_flag这个标记。它控制着整个always块。

3)tx_flag 的设计

当tx_flag == 1 时,开始传输,

当tx_flag == 0 时,停止传输,

在一个字节的传输过程中,tx_flag 需要变化两次。

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n) begin

tx_flag <= 1'b0;

tx_data <= 8'd0;end

else if (en_flag) begin

tx_flag <= 1'b1;

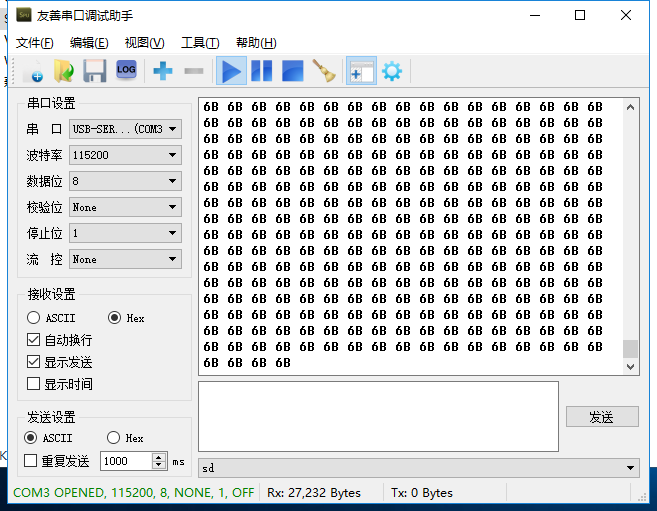

tx_data <= 8'h6F; end //此处给发送的数据赋值

else begin

tx_flag <= 1'b0;

tx_data <= 8'd0;end

end

上面的设计引入了一个新的标记为en_flag.

4)en_falg 的设计

always @(posedge sys_clk or negedge sys_rst_n ) begin

if (!sys_rst_n) begin

count <= 16'd0;

en_flag <= 1'b0;end

else if (count < 16'd10000) begin

count = count + 1'b1;

en_flag = 1'b1;end

else begin

count <= 16'b0;

en_flag = 1'b0;end

end

5)波特率的配置

parameter CLK_FREQ = 50 000 000;

parameter UART_BPS = 115200;

localpara BPS_CNT = CLK_FREQ/UART_BPS;

3、总结

上文实现了串口不断的发送6F的实验,但是发送数据不能停止,不能更改。后面将进行修改,完善。

转载于:https://www.cnblogs.com/cjyc/p/11181265.html

最后

以上就是积极星星最近收集整理的关于FPGA的串口UART通信原理及代码的全部内容,更多相关FPGA内容请搜索靠谱客的其他文章。

发表评论 取消回复