文章目录

- 一、UART串口通信

- 一、基本概念

- 二、串口数据

- 三、了解波特率

- 二、串口UART思路设计

- 三 、代码部分

- 一、串口接收模块

- 二、串口发送模块

- 四、串口回环实验

- 五、仿真验证

- 六、上板验证

- 七、总结

一、UART串口通信

一、基本概念

串口是串行接口(serial port)的简称,也称为串行通信接口或COM接口。

串口通信是指采用串行通信协议(serial communication)在一条信号线上将数据一个比特一个比特地逐位进行传输的通信模式。

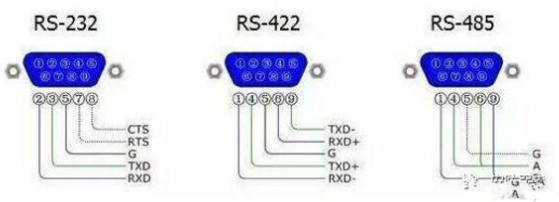

串口按电气标准及协议来划分,包括RS-232-C、RS-422、RS485等。

RS-232-C、RS-422、RS485的区别

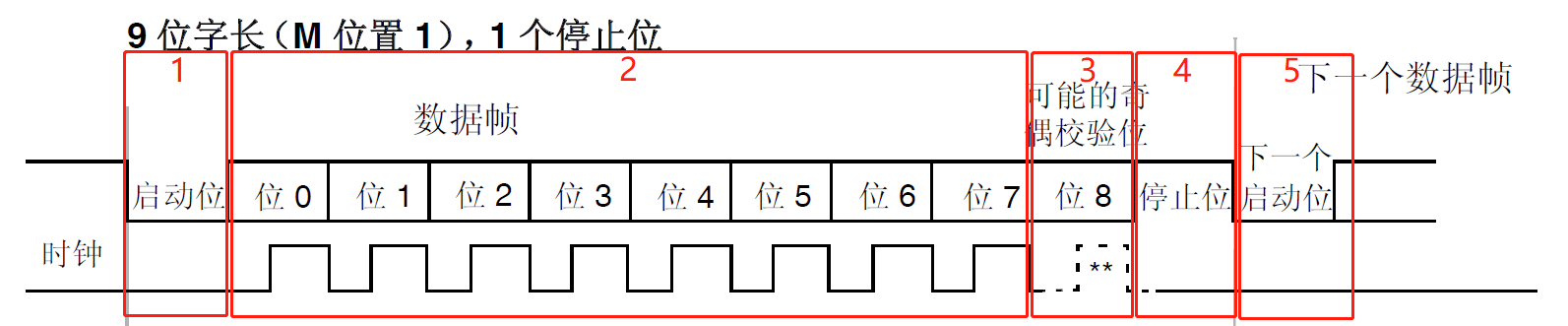

二、串口数据

- 起始位:0

- 数据位:可以是6/7/8位数据

- 奇偶校验位(可有可无):奇偶校验就是相对于数据里的1来说,如果是奇校验,有奇数个1就是在奇偶校验位是0,否则奇偶校验位是1,如果是偶校验,有奇数个1就是在奇偶校验位是1,否则奇偶校验位是0,总的来说,奇校验就是看数据位里的加上奇偶校验位(一共9位)是否是奇数,偶校验反之。

- 结束位:1

三、了解波特率

波特率表示每秒钟传送的码元符号的个数,是衡量数据传送速率的指标。

我们常常使用的是RS-232-C,RS-232-C标准规定的数据传输速率为50、75、100、150、300、600、1200、2400、4800、9600、19200、38400波特。

二、串口UART思路设计

其实串口算是一个较简单的协议了,不需要有状态机,只需要有2个计数器就可以搞定,1个是波特率计数器,用来何时收发数据,1个是bit计数,顾名思义记串口的数据bit的,串口分为2个模块,1个是接收模块,1个是发送模块

- 接收模块

在波特率中间稳定的时候去采集数据,第一位为起始位,是0,所以检测到下降沿,给一个标志就可以采集数据位了,最后串并转换。 - 发送模块

从上位机发来的数据,然后最后串并转换的时候在头部加上起始位,在尾部加上结束位即可。

三 、代码部分

这部分我自己写的,如果有问题,请及时通知我。

代码注解比较详细吧。

一、串口接收模块

// 串口接收模块

module uart_rx(

input clk,

input rst_n,

input baud_sel,// 波特率的选择

input din,// 串口接收模块接收到主机来的1bit的数据

output [7:0] dout,// 串口接收模块串并转换的数据发送

output dout_vld

);

parameter SCLK = 50_000_000;// 50MHZ系统时钟

localparam BAUD_9600 = SCLK/9600,// 9600HZ波特率周期

BAUD_115200 = SCLK/115200;// 115200HZ波特率周期

// 波特率计数器

reg [12:0] cnt_baud;

wire add_cnt_baud;

wire end_cnt_baud;

reg [12:0] baud;

// bit计数器

reg [3:0] cnt_bit;

wire add_cnt_bit;

wire end_cnt_bit;

// 对输入的1bit数据打拍

// 因为开始位是0,,停止位是1

reg din_r0;

reg din_r1;

// 检测到下降沿开始输入接收

wire din_nedge;

// 检测到下降沿的标志

reg din_nedge_flag;

// 寄存串并转换的接收到的数据9位开始位+停止位+数据8位

reg [9:0] rx_data;

reg rx_data_vld;

// 波特率计数器

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_baud <= 0;

end

else if(add_cnt_baud)begin

if(end_cnt_baud)begin

cnt_baud <= 0;

end

else begin

cnt_baud <= cnt_baud + 1;

end

end

else begin

cnt_baud <= cnt_baud;

end

end

assign add_cnt_baud = din_nedge_flag;

assign end_cnt_baud = add_cnt_baud && cnt_baud == baud - 1;

// bit计数器

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_bit <= 0;

end

else if(add_cnt_bit)begin

if(end_cnt_bit)begin

cnt_bit <= 0;

end

else begin

cnt_bit <= cnt_bit + 1;

end

end

else begin

cnt_bit <= cnt_bit;

end

end

assign add_cnt_bit = end_cnt_baud;

assign end_cnt_bit = add_cnt_bit && cnt_bit == 10 - 1;

// 波特率的选择9600 115200

always @(*)begin

case(baud_sel)

0 : baud = BAUD_9600;

1 : baud = BAUD_115200;

default : baud = BAUD_9600;

endcase

end

// 同步打拍

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

din_r0 <= 0;

din_r1 <= 0;

end

else begin

din_r0 <= din;

din_r1 <= din_r0;

end

end

// 下降沿检测

assign din_nedge = ~din_r0 & din_r1;

// 下降沿检测标志

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

din_nedge_flag <= 0;

end

else if(din_nedge)begin

din_nedge_flag <= 1'b1;

end

else if(end_cnt_bit)begin

din_nedge_flag <= 1'b0;

end

end

// 在波特率中间取稳定的值

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

rx_data <= 0;

end

else if(add_cnt_baud && cnt_baud == (baud >> 1) - 1)begin

rx_data[cnt_bit] <= din;

end

end

assign dout = rx_data[8:1];

// 数据有效

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

rx_data_vld <= 0;

end

else if(end_cnt_bit)begin

rx_data_vld <= 1;

end

else begin

rx_data_vld <= 1'b0;

end

end

assign dout_vld = rx_data_vld;

endmodule

二、串口发送模块

module uart_tx(

input clk,

input rst_n,

input baud_sel,// 波特率的选择

input [7:0] din,// 串并转换的数据

input din_vld,// 串并转换的数据有效

output dout,// 发送模块发送的1bit数据

output busy // 发送模块忙标志

);

parameter SCLK = 50_000_000;// 50MHZ系统时钟

localparam BAUD_9600 = SCLK/9600,// 9600HZ波特率周期

BAUD_115200 = SCLK/115200;// 115200HZ波特率周期

// 波特率计数器

reg [12:0] cnt_baud;

wire add_cnt_baud;

wire end_cnt_baud;

reg [12:0] baud;

// bit计数器

reg [3:0] cnt_bit;

wire add_cnt_bit;

wire end_cnt_bit;

// 寄存发送模块接收的数据有效

reg rx_data_vld_flag;

// 寄存要发送的数据

reg [9:0] tx_data;

// 波特率计数器

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_baud <= 0;

end

else if(add_cnt_baud)begin

if(end_cnt_baud)begin

cnt_baud <= 0;

end

else begin

cnt_baud <= cnt_baud + 1;

end

end

else begin

cnt_baud <= cnt_baud;

end

end

assign add_cnt_baud = rx_data_vld_flag;

assign end_cnt_baud = add_cnt_baud && cnt_baud == baud - 1;

// bit计数器

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_bit <= 0;

end

else if(add_cnt_bit)begin

if(end_cnt_bit)begin

cnt_bit <= 0;

end

else begin

cnt_bit <= cnt_bit + 1;

end

end

else begin

cnt_bit <= cnt_bit;

end

end

assign add_cnt_bit = end_cnt_baud;

assign end_cnt_bit = add_cnt_bit && cnt_bit == 10 - 1;

// 波特率的选择9600 115200

always @(*)begin

case(baud_sel)

0 : baud = BAUD_9600;

1 : baud = BAUD_115200;

default : baud = BAUD_9600;

endcase

end

// 数据有效的标志

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

rx_data_vld_flag <= 0;

end

else if(din_vld)begin

rx_data_vld_flag <= 1'b1;

end

else if(end_cnt_bit)begin

rx_data_vld_flag <= 1'b0;

end

end

// 数据有效添加开始位和停止位

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

tx_data <= 0;

end

else if(din_vld)begin

tx_data <= {1'b1,din,1'b0};

end

end

// 数据有效标志1bit数据发送,之后都发高位,不能发低位

assign dout = rx_data_vld_flag?tx_data[cnt_bit]:1'b1;

// 这个busy有待商榷

assign busy = rx_data_vld_flag;

endmodule

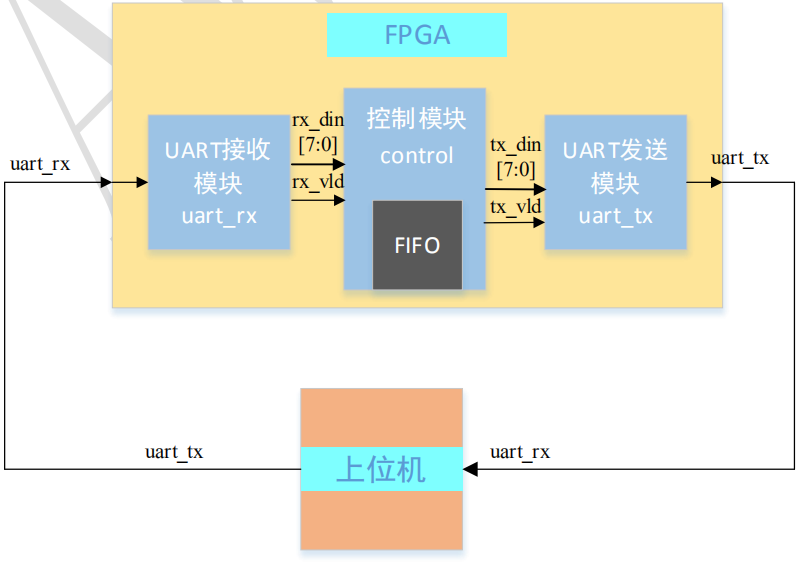

四、串口回环实验

任务要求

◼ FPGA 与上位机通过串口通信,完成数据环回;

◼ 波特率可调,即可以选择 115200、57600、38400 等;

◼ 使用 FIFO 作为数据缓存单元

系统框图

难的不是串口接收发送模块,难的是串口控制的fifo,对于fifo的使用我还不太熟悉,fifo的读写请求和数据要一致,还有fifo的前显模式和正常模式。

串口控制模块

// 串口控制模块

module uart_ctrl(

input clk,

input rst_n,

input [7:0] din,// 接收模块8位数据

input din_vld,// 接收模块8位数据的

input busy,

output [7:0] dout,

output dout_vld

);

wire rdreq;

wire wrreq;

wire empty;

wire full ;

wire [7:0] q_out;

wire [4:0] usedw;

// 用fifo缓存数据,来控制读写

fifo fifo_inst (

.aclr ( ~rst_n ),

.clock ( clk ),

.data ( din ),

.rdreq ( rdreq ),

.wrreq ( wrreq ),

.empty ( empty ),

.full ( full ),

.q ( q_out ),

.usedw ( usedw )

);

// 写使能,写进fifo

assign wrreq = ~full && din_vld;

// 读使能,从fifo读出来

assign rdreq = ~empty && ~busy && (usedw == 2);

assign dout = q_out;

assign dout_vld = rdreq;

endmodule

顶层

module top(

input clk,

input rst_n,

input uart_rx,

output uart_tx

);

wire [7:0] rx_data;

wire rx_data_vld;

wire busy;

wire [7:0] tx_data;

wire tx_data_vld;

// 串口接收模块

uart_rx u_uart_rx(

/* input */.clk (clk ),

/* input */.rst_n (rst_n ),

/* input */.baud_sel (0),// 波特率的选择

/* input */.din (uart_rx ),// 串口接收模块接收到主机来的1bit的数据

/* output [7:0] */.dout (rx_data ),// 串口接收模块串并转换的数据发送

/* output */.dout_vld (rx_data_vld)

);

// 串口控制模块

uart_ctrl u_uart_ctrl(

/* input */.clk (clk ),

/* input */.rst_n (rst_n ),

/* input [7:0] */.din (rx_data ),// 接收模块8位数据

/* input */.din_vld (rx_data_vld ),// 接收模块8位数据的

/* input */.busy (busy ),

/* output [7:0] */.dout (tx_data ),

/* output */.dout_vld (tx_data_vld)

);

// 串口发送模块

uart_tx u_uart_tx(

/* input */.clk (clk ),

/* input */.rst_n (rst_n ),

/* input */.baud_sel (0),// 波特率的选择

/* input [7:0] */.din (tx_data ),// 串并转换的数据

/* input */.din_vld (tx_data_vld ),// 串并转换的数据有效

/* output */.dout (uart_tx ),// 发送模块发送的1bit数据

/* output */.busy (busy ) // 发送模块忙标志

);

endmodule

串口接收发送模块同上

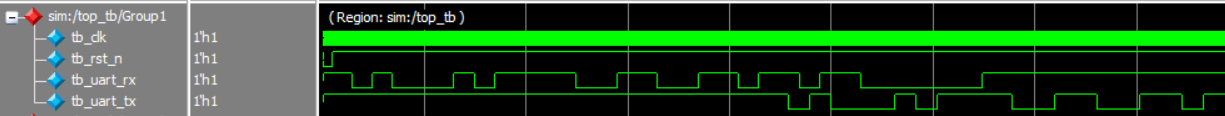

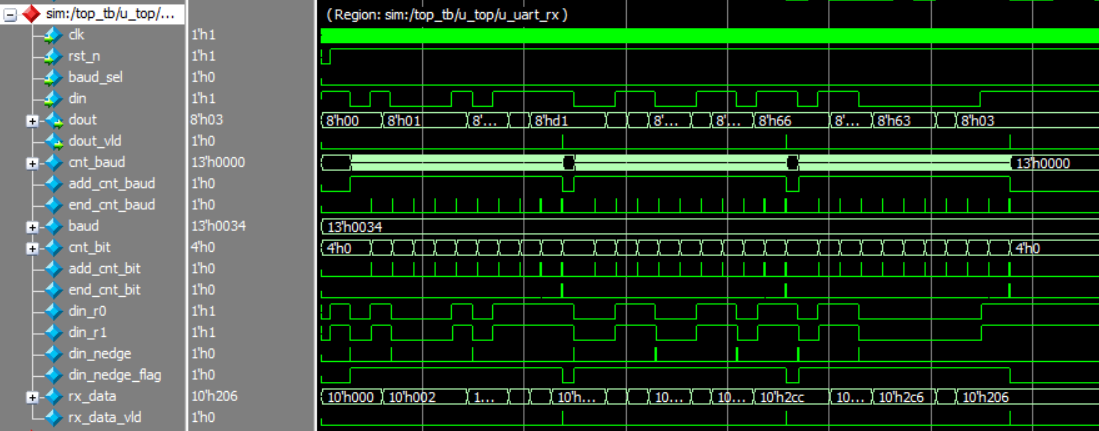

五、仿真验证

fifo就是队列,先进先出,我这里设了数据量深度为2个数据出现数据

顶层仿真

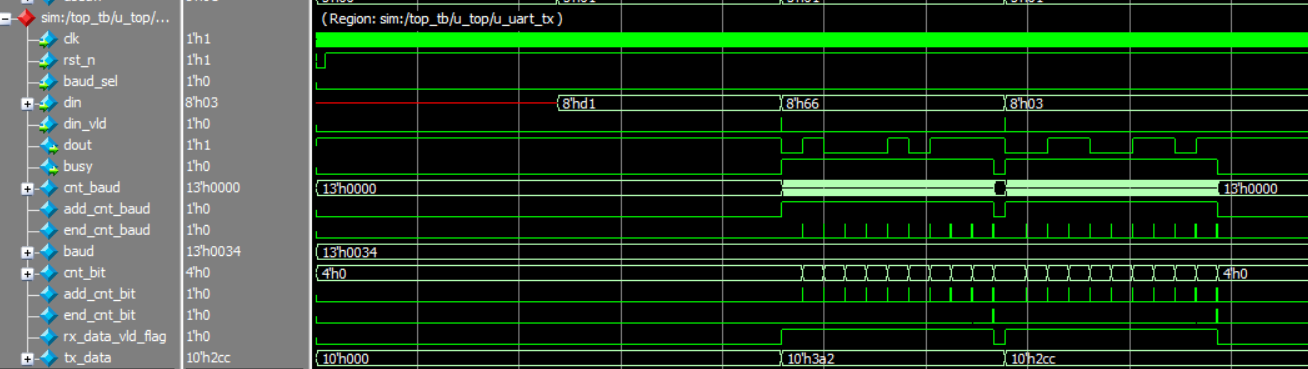

串口发送模块仿真

串口发送模块仿真

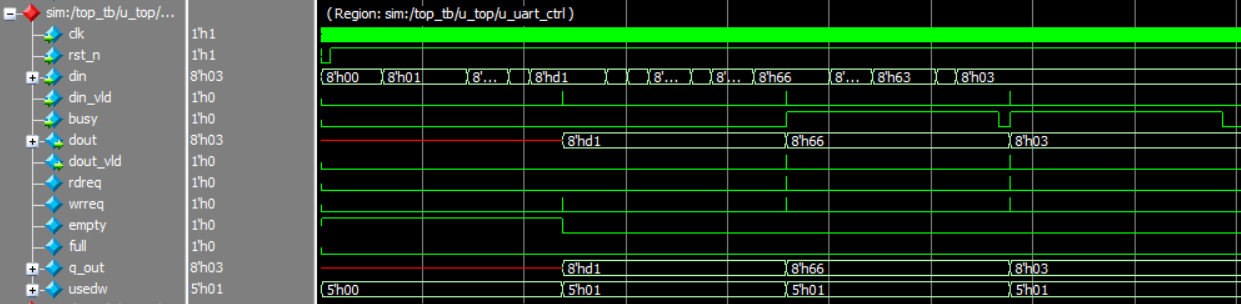

串口控制模块仿真

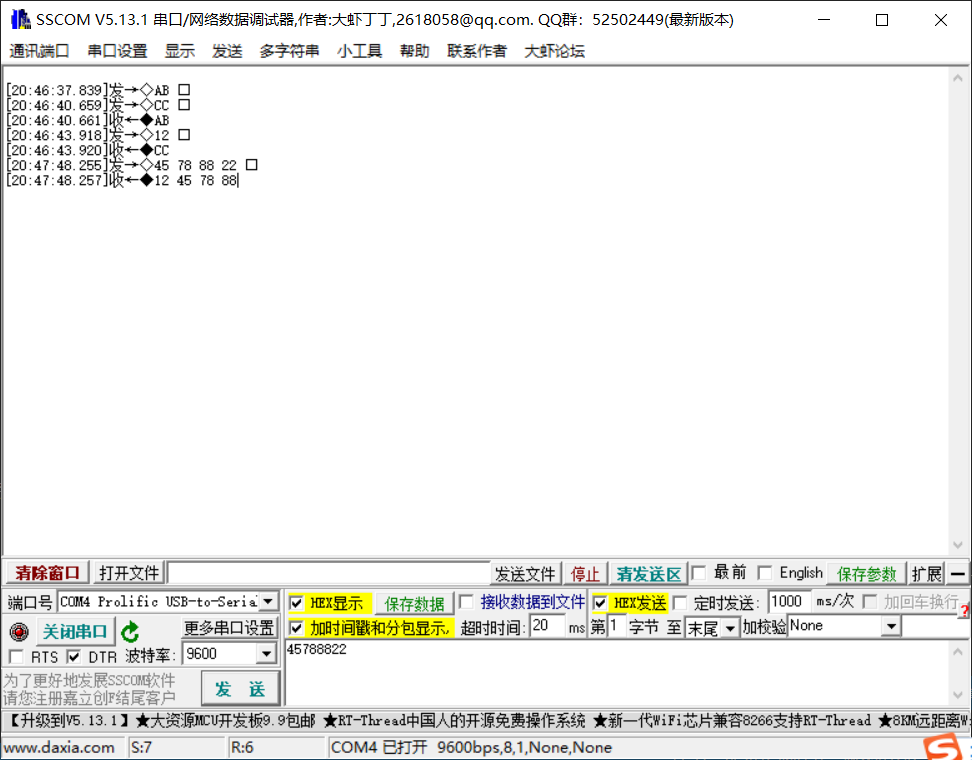

六、上板验证

七、总结

串口通信算是最最最基础的通信协议了,虽然我也当时写不出来,但是后来仔细研究,串口不难,难的是fifo。

以后再写一篇关于fifo的使用。

最后

以上就是单身小蘑菇最近收集整理的关于【FPGA】串口通信UART一、UART串口通信二、串口UART思路设计三 、代码部分四、串口回环实验五、仿真验证六、上板验证七、总结的全部内容,更多相关【FPGA】串口通信UART一、UART串口通信二、串口UART思路设计三内容请搜索靠谱客的其他文章。

发表评论 取消回复