module ram_test

#(

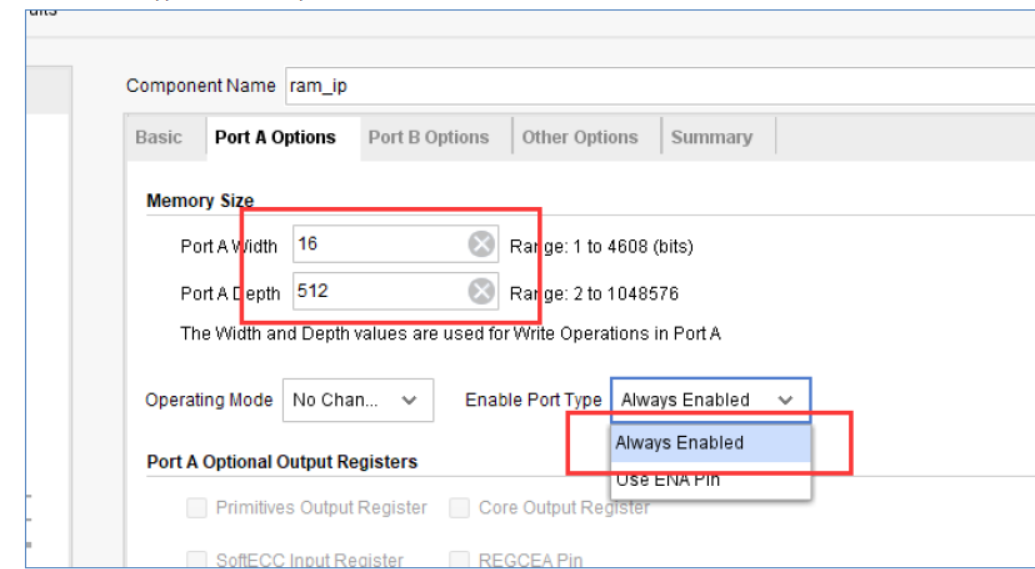

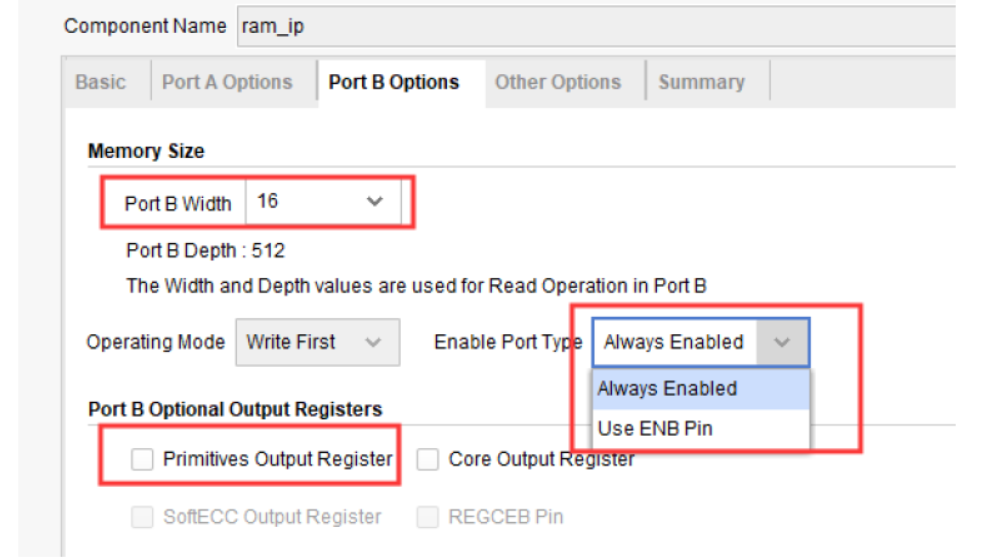

parameter addr_legth=9,

parameter data_legth=16

)

(

input clk_sys,

input rst_n

);

reg [addr_legth-1:0] w_addr;

reg [data_legth-1:0] w_data;

reg wea;

reg [addr_legth-1:0] r_addr;

wire [data_legth-1:0] r_data; //注意作为输出连线,要用wire,用reg会报错。

//产生RAM PORTB的读地址

always@(posedge clk_sys or negedge rst_n)

begin

if(rst_n)

r_addr<=9'd0;

else if(|w_addr) //所有位位或,地址一般不等于0,位或得0表示地址为0

r_addr<=r_addr+1'b1;

else

r_addr<=9'd0;

end

//产生RAM PORTA的写使能信号

always@(posedge clk_sys or negedge rst_n)

begin

if(rst_n)

wea<=1'b0;

else

begin

if(&w_addr) //所有位位与,全为1,表示已经写完。准备结束

wea<=1'b0;

else

wea<=1'b1;

end

end

//产生RAM PORTA写入的地址及数据

always@ (posedge clk_sys or negedge rst_n)

begin

if(rst_n)

begin

w_addr<=9'd0;

w_data<=16'd0;

end

else

begin

if(wea)

begin

if(&w_addr)

begin

w_addr<=w_addr;

w_data<=w_data;

end

else

begin

w_addr<=w_addr+1'b1;

w_data<=w_data+3'd5;

end

end

end

end

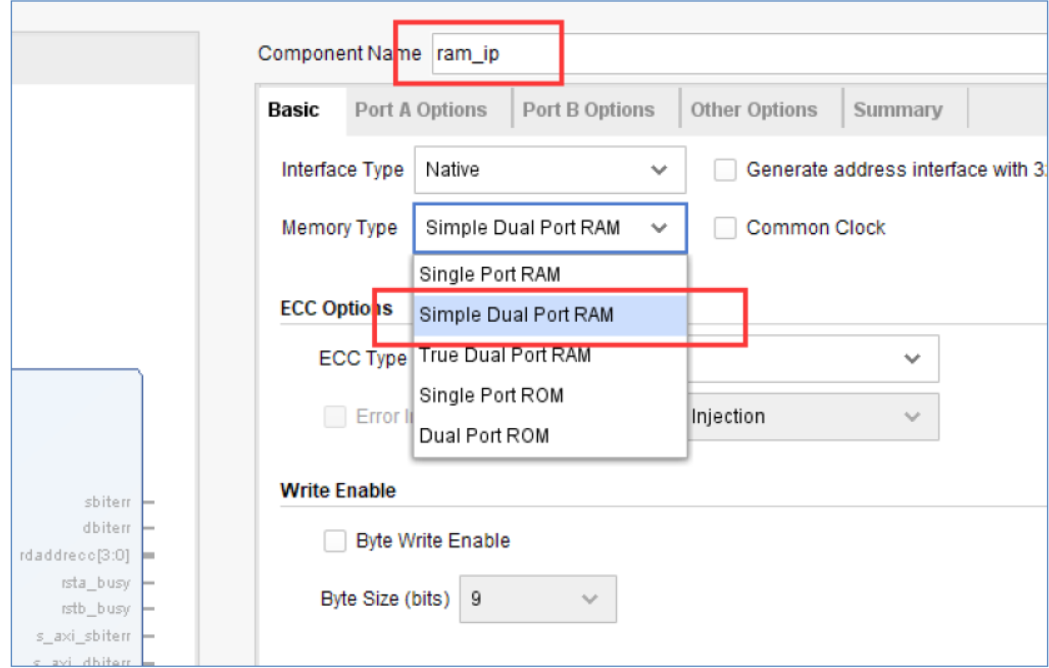

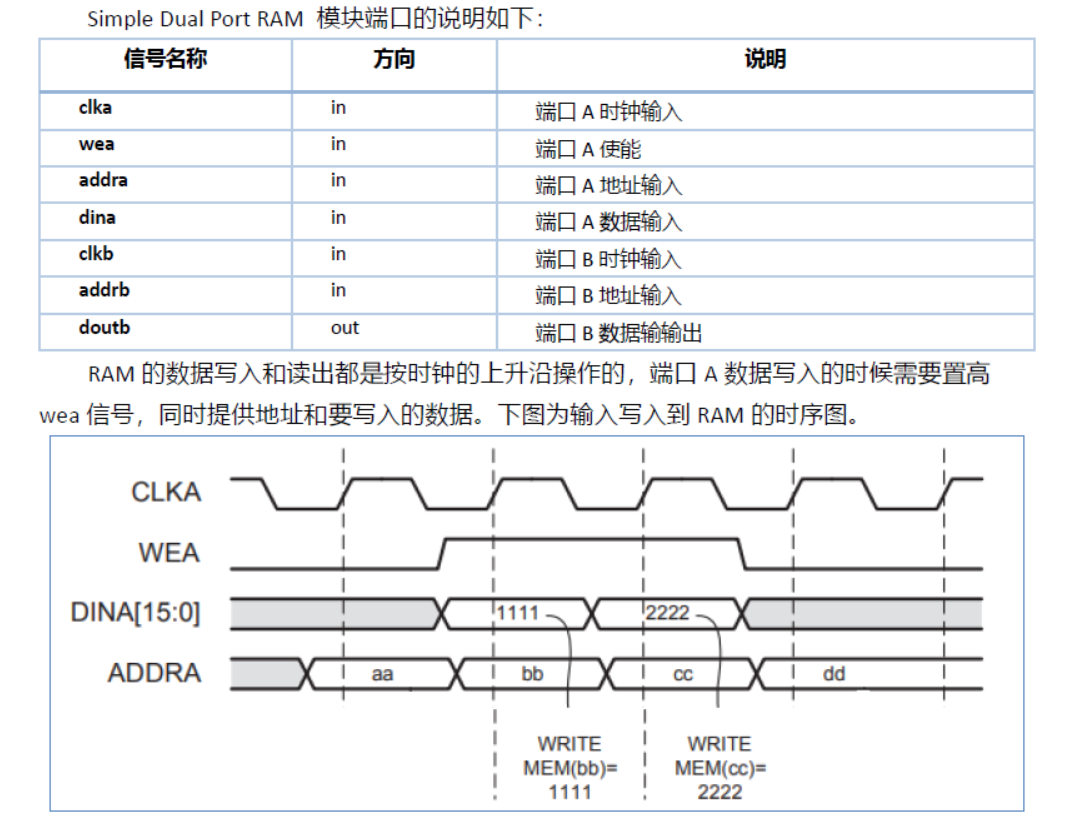

//RAM实例化

ram_ip ram_ip_init (

.clka(clk_sys), // input wire clka

.wea(wea), // input wire [0 : 0] wea

.addra(w_addr), // input wire [8 : 0] addra

.dina(w_data), // input wire [15 : 0] dina

.clkb(clk_sys), // input wire clkb

.addrb(r_addr), // input wire [8 : 0] addrb

.doutb(r_data) // output wire [15 : 0] doutb

);

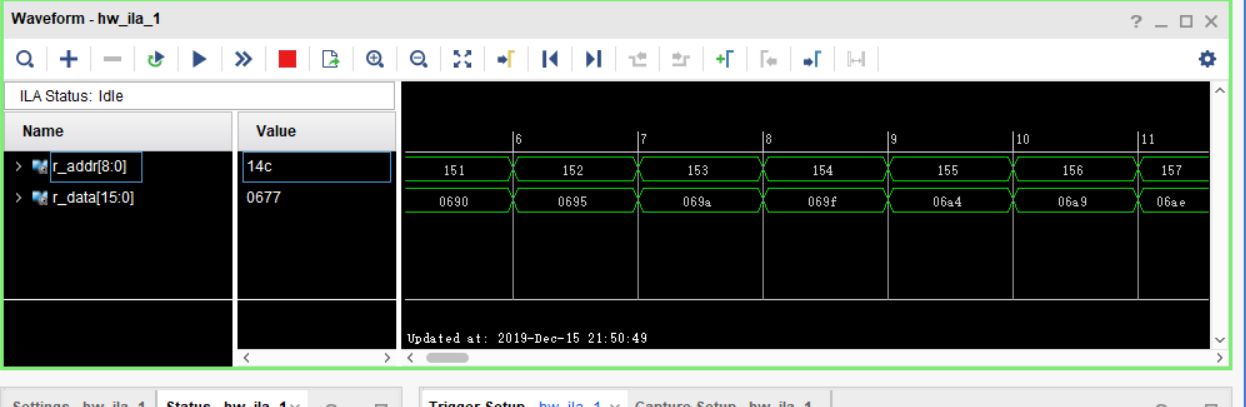

//逻辑分析仪实例化

ila_0 ila_init (

.clk(clk_sys), // input wire clk

.probe0(r_addr), // input wire [8:0] probe0

.probe1(r_data) // input wire [15:0] probe1

);

endmodule测试结果:

最后

以上就是微笑柠檬最近收集整理的关于ZYQN学习之RAM使用的全部内容,更多相关ZYQN学习之RAM使用内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复