目录

- 原语简介

- 原语的分类

- 时钟相关的原语

- IBUFG

- IBUFGDS

- BUFG

- BUFGP

- BUFGCE

- BUFGMUX

- BUFGDLL

- DCM

- 接口相关的原语

- IDDR

- ODDR

原语简介

原语,即primitive,原语类似最底层的描述方法,是不同厂商针对自己FPGA芯片提供的底逻辑资源的描述。 因此不同的厂商,原语不同,同一家的FPGA,由于不同系列的芯片内部资源一般不同,原语也是不通用的。 使用原语的好处,可以直接例化使用,不用定制IP。 我们在进行FPGA开发时的HDL代码在进行综合后的输出就是由原语组成的逻辑网表,因此原语是不会参于综合过程的。

我们在集成开发工具中能够例化的原语模板实质不是真正的原语,为了设计人员设计方便其已经经过一层封装,不过通常还是将其称为原语。 正如前面所说,原语是对底层资源的直接描述,因此其抽象层次低,是需要考虑实现细节更多的一种实现,采用原语的设计方式对于FPGA底层资源理解要高。 一般在实际HDL代码编写中,不需要去进行原语的调用,我们进行HDL代码这种抽象层次更高的设计,将具体细节交给了集成开发环境完成。

原语的分类

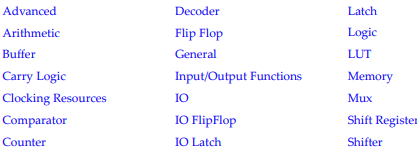

Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G比特收发器组件。

时钟相关的原语

目前电路设计一般推荐使用同步时序电路。 同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。 为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。 FPGA 全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select RAM)的时延和抖动都为最小。 但是如果时钟信号不是由FPGA芯片的专用时钟pin(或pad)引入FPGA的,那么它通常就需要在FPGA内部被显式的连接到时钟树资源上,否则,直接使用这种不经过时钟树的时钟信号,会给FPGA设计的时序带来非常麻烦的问题,进而导致逻辑行为失败。可是HDL代码仅仅描述功能,无法向编译器表达“希望将某一时钟信号连接到时钟树资源”这样的一层意思,那么此时,就需要使用类似BUFG这样的原语提供的底层模块来进行指示。需要说明的是,直接从全局时钟pin(或pad)引入的时钟信号,对于xilinx的FPGA芯片来说,实际上是通过IBUFG+BUFG这样的组合直接连接到全局时钟树上的,只不过此时我们不需要显式例化这两个原语。

与全局时钟资源相关的Xilinx器件原语包括:IBUFG、IBUFGDS、BUFG、BUFGP、BUFGCE、BUFGMUX、BUFGDLL和DCM等。

IBUFG

IBUFG即输入全局缓冲,是与专用全局时钟输入管脚相连接的首级全局缓冲。所有从全局时钟管脚输入的信号必须经过IBUF元,否则在布局布线时会报错。 IBUFG支持AGP、CTT、GTL、GTLP、HSTL、LVCMOS、LVDCI、LVDS、LVPECL、LVTTL、PCI、PCIX和 SSTL等多种格式的IO标准。

IBUFGDS

IBUFGDS是IBUFG的差分形式,当信号从一对差分全局时钟管脚输入时,必须使用IBUFGDS作为全局时钟输入缓冲。IBUFG支持BLVDS、LDT、LVDSEXT、LVDS、LVPECL和ULVDS等多种格式的IO标准。

BUFG

全局缓冲,它的输入是IBUFG的输出,BUFG的输出到达FPGA内部的IOB、CLB、选择性块RAM的时钟延迟和抖动最小。BUFG是具有高扇出的全局时钟缓冲器,一般由综合器自动推断并使用,其和同类原语的RTL结构如图所示。全局时钟是具有高扇出驱动能力的缓冲器,可以将信号连到时钟抖动可以忽略不计的全局时钟网络,BUFG组件还可应用于典型的高扇出信号和网络,如复位信号和时钟使能信号。如果要对全局时钟实现PLL或DCM等时钟管理,则需要手动例化该缓冲器。

BUFGP

相当于IBUG加上BUFG

BUFGCE

是带有时钟使能端的全局缓冲。它有一个输入I、一个使能端CE和一个输出端O。只有当BUFGCE的使能端CE有效(高电平)时,BUFGCE才有输出。

BUFGMUX

是全局时钟选择缓冲,它有I0和I1两个输入,一个控制端S,一个输出端O。当S为低电平时输出时钟为I0,反之为I1。需要指出的是BUFGMUX的应用十分灵活,I0和I1两个输入时钟甚至可以为异步关系。

BUFGDLL

是全局缓冲延迟锁相环,相当于BUFG与DLL的结合。BUFGDLL在早期设计中经常使用,用以完成全局时钟的同步和驱动等功能。随着数字时钟管理单元(DCM)的日益完善,目前BUFGDLL的应用已经逐渐被DCM所取代。

DCM

数字时钟管理单元,主要完成时钟的同步、移相、分频、倍频和去抖动等。DCM与全局时钟有着密不可分的联系,为了达到最小的延迟和抖动,几乎所有的DCM应用都要使用全局缓冲资源。

接口相关的原语

当需要使用接口资源中的寄存器来实现高速数据采集时,如果直接调用相关的原语,编译器便会利用接口资源中的寄存器进行数据的传输,达到较高性能的同时,能够避免复杂的时序。相关的原语如:ODDR、IDDR、IDDR2CLK、ISERDES、OSERDES等。

IDDR

旨在将外部双数据速率(DDR)信号接收到Xilinx FPGA中。IDDR可用的模式可以在捕获数据的时间和时钟沿或在相同的时钟沿向FPGA架构显示数据。此功能使您可以避免其他时序复杂性和资源使用情况。

ODDR

通过ODDR把两路单端的数据合并到一路上输出,上下沿同时输出数据,上沿输出a路下沿输出b路;如果两路输入信号一路恒定为1,一路恒定为0,那么输出的信号实际上就是输入的时钟信号。

最后

以上就是朴素金毛最近收集整理的关于FPGA原语简介原语简介原语的分类时钟相关的原语接口相关的原语的全部内容,更多相关FPGA原语简介原语简介原语内容请搜索靠谱客的其他文章。

发表评论 取消回复