32位乘法器和除法器

- 32位乘法器和除法器的设计与实现

- 乘法器原理

- 除法器原理

- 乘法器代码

- 除法器代码

- 乘除法器顶层模块代码(包含拨码输入以及数码管输出)

- 约束文件修改

32位乘法器和除法器的设计与实现

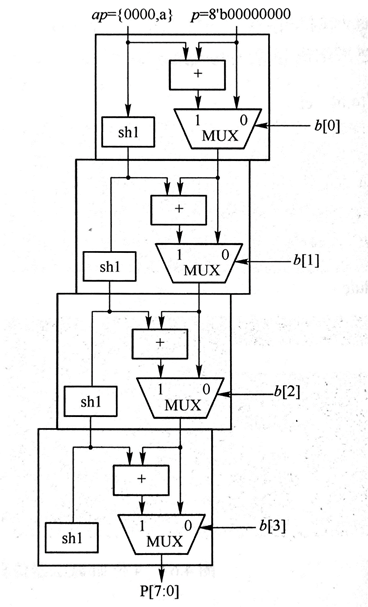

乘法器原理

类比10进制乘法,利用移位运算。每次对两因数中的一个的第一位进行判断,一共判断32位共循环32次,若该位为1,则将积加上另一因数,若为0,则不用加。每次循环结束将用于判断的因数右移一位,用于和积相加的因数左移一位,循环完成后,积即为两因数的积。

除法器原理

类比十进制除法,利用移位运算。将被除数前32位拼接上32位的0,一共判断32位共循环32次,每次比较被除数前32位与除数相比,若大于除数,则将被除数前32位减去除数,并将整个64位的被除数加上1,若小于除数,则什么也不做,每次循环完成后将被除数左移一位。循环完成后,被除数前32位为余数,后32位为商。

乘法器代码

module mult32(

input wire [31:0] a,

input wire [31:0] b,

output reg [63:0]p

);

reg [63:0] pv;

reg [63:0] ap;

integer i;

always@(*)

begin

pv=64'b0000_0000_0000_0000_0000_0000_0000_0000_0000_0000_0000_0000_0000_0000_0000_0000;

ap={32'b0000_0000_0000_0000_0000_0000_0000_0000,a};

for(i=0;i<=31;i=i+1)

begin

if(b[i]==1)

pv=pv+ap;

ap={ap[62:0],1'b0};

end

p=pv;

end

endmodule

除法器代码

module div32(

input[31:0] a,

input[31:0] b,

output reg [31:0] yshang,

output reg [31:0] yyushu

);

reg[31:0] tempa;

reg[31:0] tempb;

reg[63:0] temp_a;

reg[63:0] temp_b;

integer i;

always @(a or b)

begin

tempa <= a;

tempb <= b;

end

always @(tempa or tempb)

begin

temp_a = {32'h00000000,tempa};

temp_b = {tempb,32'h00000000};

for(i = 0;i < 32;i = i + 1)

begin

temp_a = {temp_a[62:0],1'b0};

if(temp_a[63:32] >= tempb)

temp_a = temp_a - temp_b + 1'b1;

else

temp_a = temp_a;

end

yshang <= temp_a[31:0];

yyushu <= temp_a[63:32];

end

endmodule

乘除法器顶层模块代码(包含拨码输入以及数码管输出)

module mult_div_top(

input clk,

input [15:0] sw,

output reg [6:0] a_to_g,

output reg [3:0] an,

output reg [3:0] led,

output wire dp

);

reg [31:0] a;

reg [31:0] b;

wire [63:0] mult;

wire [63:0] div;

reg [15:0] disp;

always@(sw[15:8])

begin

if(sw[15]==0)

case(sw[14:13])

2'b00:a[31:24]=sw[7:0];

2'b01:a[23:16]=sw[7:0];

2'b11:a[15:8]=sw[7:0];

2'b10:a[7:0]=sw[7:0];

default:;

endcase

else if(sw[15]==1)

case(sw[14:13])

2'b00:b[31:24]=sw[7:0];

2'b01:b[23:16]=sw[7:0];

2'b11:b[15:8]=sw[7:0];

2'b10:b[7:0]=sw[7:0];

default:;

endcase

end

always@(*)

begin

if(sw[8]==0)

case(sw[10:9])

2'b00:

begin

disp=mult[63:48];

led=4'b1000;

end

2'b01:

begin

disp=mult[47:32];

led=4'b0100;

end

2'b11:

begin

disp=mult[31:16];

led=4'b0010;

end

2'b10:

begin

disp=mult[15:0];

led=4'b0001;

end

default:

begin

disp=16'b0000_0000_0000_0000;

led=4'b0000;

end

endcase

else if(sw[8]==1)

case(sw[10:9])

2'b00:

begin

disp=div[63:48];

led=4'b1000;

end

2'b01:

begin

disp=div[47:32];

led=4'b0100;

end

2'b11:

begin

disp=div[31:16];

led=4'b0010;

end

2'b10:

begin

disp=div[15:0];

led=4'b0001;

end

default:

begin

disp=16'b0000_0000_0000_0000;

led=4'b0000;

end

endcase

end

mult32 multiply(

.a(a),

.b(b),

.p(mult)

);

div32 divide(

.a(a),

.b(b),

.yshang(div[63:32]),

.yyushu(div[31:0])

);

wire [15:0]x;

assign x=disp;

wire [1:0] s;

reg [3:0] digit;

reg [19:0] clkdiv;

assign dp=1;

assign s=clkdiv[19:18];

assign ane=4'b1111;

always@(*)

case(s)

0:digit=x[3:0];

1:digit=x[7:4];

2:digit=x[11:8];

3:digit=x[15:12];

default:digit=x[3:0];

endcase

always@(*)

case(digit)

0:a_to_g=7'b0000001;

1:a_to_g=7'b1001111;

2:a_to_g=7'b0010010;

3:a_to_g=7'b0000110;

4:a_to_g=7'b1001100;

5:a_to_g=7'b0100100;

6:a_to_g=7'b0100000;

7:a_to_g=7'b0001111;

8:a_to_g=7'b0000000;

9:a_to_g=7'b0000100;

'hA:a_to_g=7'b0001000;

'hB:a_to_g=7'b1100000;

'hC:a_to_g=7'b0110001;

'hD:a_to_g=7'b1000010;

'hE:a_to_g=7'b0110000;

'hF:a_to_g=7'b0111000;

default: a_to_g=7'b0000001;

endcase

always@(*)

begin

an=4'b1111;

an[s]=0;

end

always@(posedge clk)

begin

clkdiv<=clkdiv+1;

end

endmodule

约束文件修改

直接IO Planning之后Run Implementation会出现’IO Clock Placer failed’

需要在约束文件中加上

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets sw]

了解更多

了解更多

以下是我的约束文件(板子型号BASYS3)

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property PACKAGE_PIN W5 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports dp]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[15]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[14]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[13]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[12]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[11]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[10]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {an[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {an[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {an[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {an[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {a_to_g[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {a_to_g[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {a_to_g[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {a_to_g[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {a_to_g[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {a_to_g[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {a_to_g[0]}]

set_property PACKAGE_PIN W7 [get_ports {a_to_g[6]}]

set_property PACKAGE_PIN W6 [get_ports {a_to_g[5]}]

set_property PACKAGE_PIN U8 [get_ports {a_to_g[4]}]

set_property PACKAGE_PIN V8 [get_ports {a_to_g[3]}]

set_property PACKAGE_PIN U5 [get_ports {a_to_g[2]}]

set_property PACKAGE_PIN V5 [get_ports {a_to_g[1]}]

set_property PACKAGE_PIN U7 [get_ports {a_to_g[0]}]

set_property PACKAGE_PIN W4 [get_ports {an[3]}]

set_property PACKAGE_PIN V4 [get_ports {an[2]}]

set_property PACKAGE_PIN U4 [get_ports {an[1]}]

set_property PACKAGE_PIN U2 [get_ports {an[0]}]

set_property PACKAGE_PIN L1 [get_ports {led[3]}]

set_property PACKAGE_PIN P1 [get_ports {led[2]}]

set_property PACKAGE_PIN N3 [get_ports {led[1]}]

set_property PACKAGE_PIN P3 [get_ports {led[0]}]

set_property PACKAGE_PIN R2 [get_ports {sw[15]}]

set_property PACKAGE_PIN T1 [get_ports {sw[14]}]

set_property PACKAGE_PIN U1 [get_ports {sw[13]}]

set_property PACKAGE_PIN W2 [get_ports {sw[12]}]

set_property PACKAGE_PIN R3 [get_ports {sw[11]}]

set_property PACKAGE_PIN T2 [get_ports {sw[10]}]

set_property PACKAGE_PIN T3 [get_ports {sw[9]}]

set_property PACKAGE_PIN V2 [get_ports {sw[8]}]

set_property PACKAGE_PIN W13 [get_ports {sw[7]}]

set_property PACKAGE_PIN W14 [get_ports {sw[6]}]

set_property PACKAGE_PIN V15 [get_ports {sw[5]}]

set_property PACKAGE_PIN W15 [get_ports {sw[4]}]

set_property PACKAGE_PIN W17 [get_ports {sw[3]}]

set_property PACKAGE_PIN W16 [get_ports {sw[2]}]

set_property PACKAGE_PIN V16 [get_ports {sw[1]}]

set_property PACKAGE_PIN V17 [get_ports {sw[0]}]

set_property PACKAGE_PIN U16 [get_ports dp]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clk]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets {sw[8]}]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets {sw[9]}]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets {sw[10]}]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets {sw[13]}]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets {sw[14]}]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets {sw[15]}]

最后

以上就是朴实猫咪最近收集整理的关于32位乘法器和除法器32位乘法器和除法器的设计与实现的全部内容,更多相关32位乘法器和除法器32位乘法器和除法器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复