转载与:https://blog.csdn.net/hua371242480/article/details/88629023

sensor接口之DVP

- 什么是DVP

- DVP时序

-

- PCLK、HSYNC、VSYNC对应关系

- sensor并行输出说明

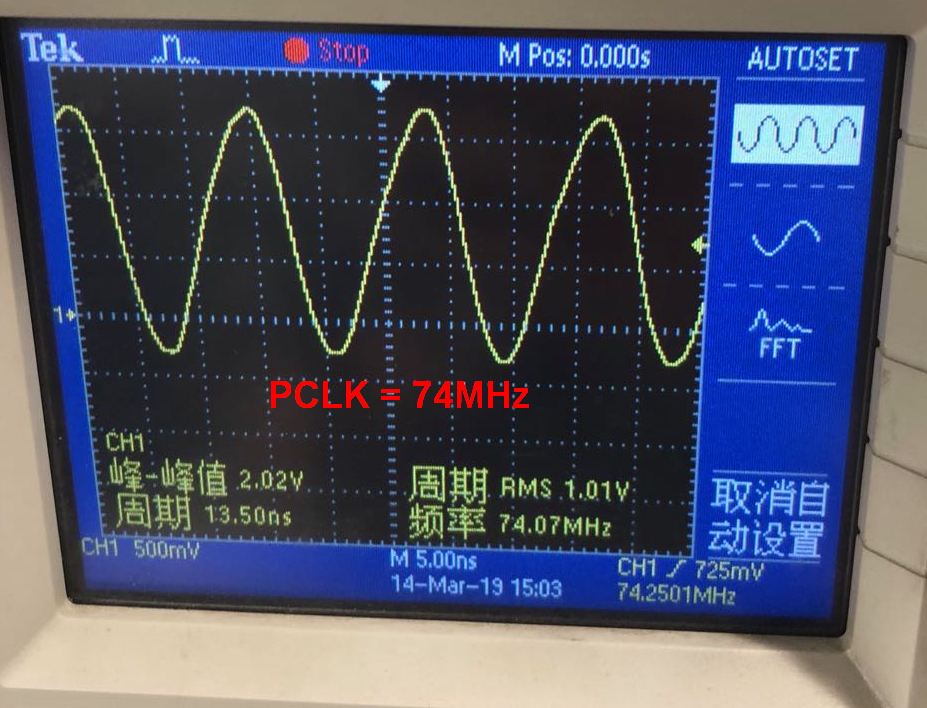

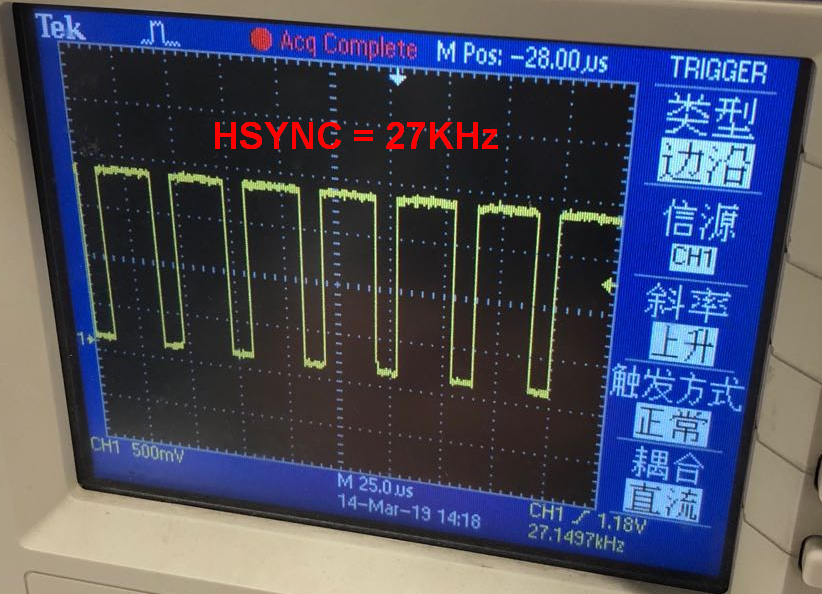

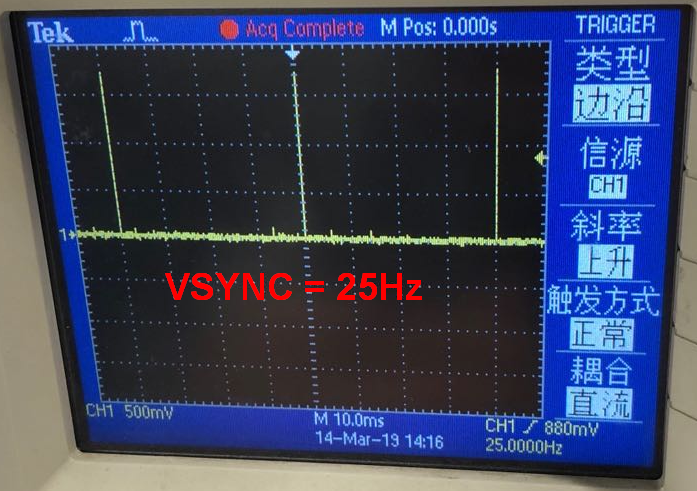

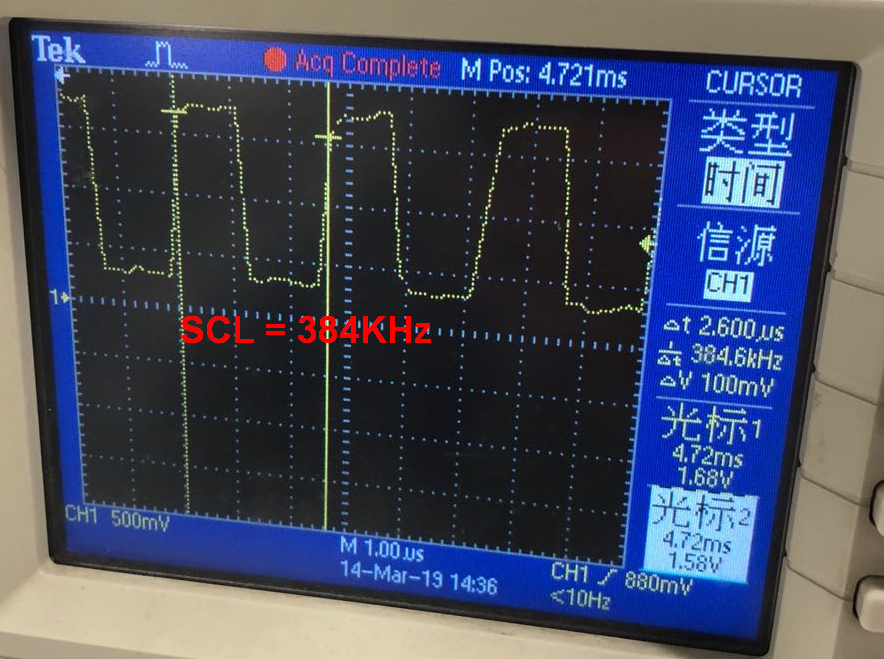

- 实际测量DVP信号

什么是DVP

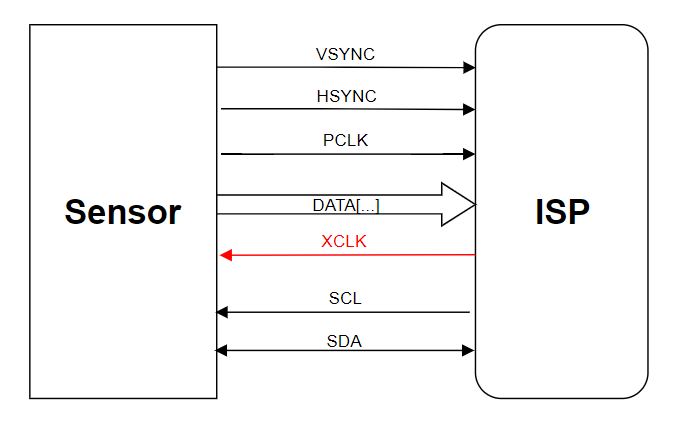

DVP(Digital Video Port) 是传统的sensor输出接口,采用并行输出方式,d数据位宽有8bit、10bit、12bit、16bit,是CMOS电平信号(重点是非差分信号),PCLK最大速率为96MHz,接口如下图:

PCLK:pixel clock ,像素时钟,每个时钟对应一个像素数据;

HSYNC:horizonal synchronization,行同步信号

VSYNC:vertical synchronization,帧同步信号;

DATA:像素数据,视频数据,具体位宽要看ISP是否支持;

XCLK:或者MCLK,ISP芯片输出给驱动sensor的时钟;

SCL,SDA:IIC用来读写sensor的寄存器,配置sensor。

DVP时序

PCLK、HSYNC、VSYNC对应关系

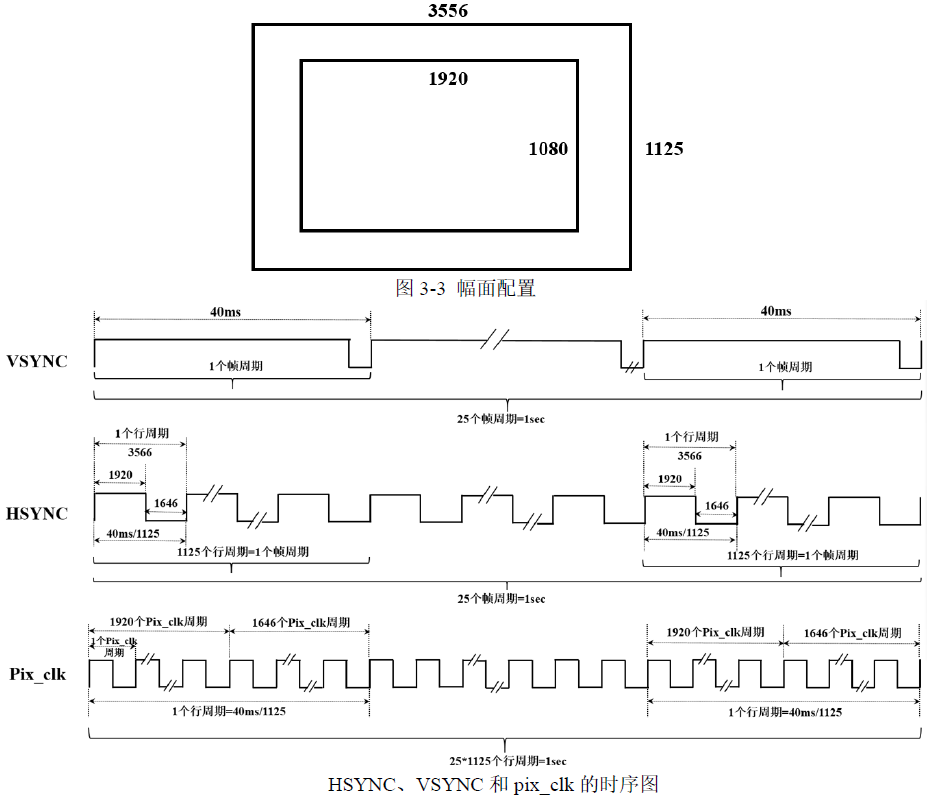

ISP与sensor通过DVP接口连接,ISP首先会给sensor一个XCLK,sensor内部的PLL会对计算,产生PCLK,PCLK由幅面(F_W、F_H)、帧率(FPS)决定,并存在如下关系:

以F_W = 3556,F_H = 1125,A_W = 1920, A_H = 1080,FPS = 25(1080P25)为例,说明几个对应关系:

注意:上图中标有错误,对照下文说明可以找出错误

-

PCLK是一个像素传输的时间,所以HSYNC时间是PCLK的3556倍;

-

在这3556个像素中,只有1920个像素是有效的(A_W大小),在剩下的1636个像素点时间内sensor是不传输数据的;

-

VSYNC是帧同步信号,所以VSYNC时间是PCLK的3556*1125倍;

-

同样只有在1920*1080个有效像素时间内,sensor在传输数据;

sensor并行输出说明

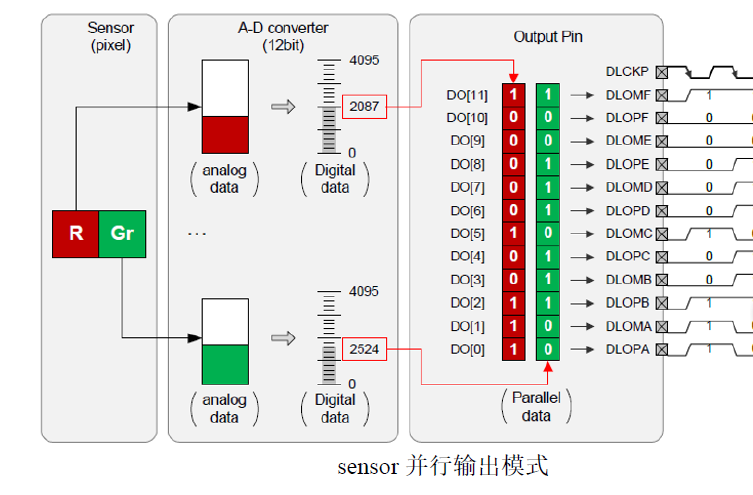

图中有12bit通道传输像素数据,但有些ISP芯片只能接受并行输入,会丢弃sensor端输出的低两位,这会造成低照条件下,颜色之间过度明显。

实际测量DVP信号

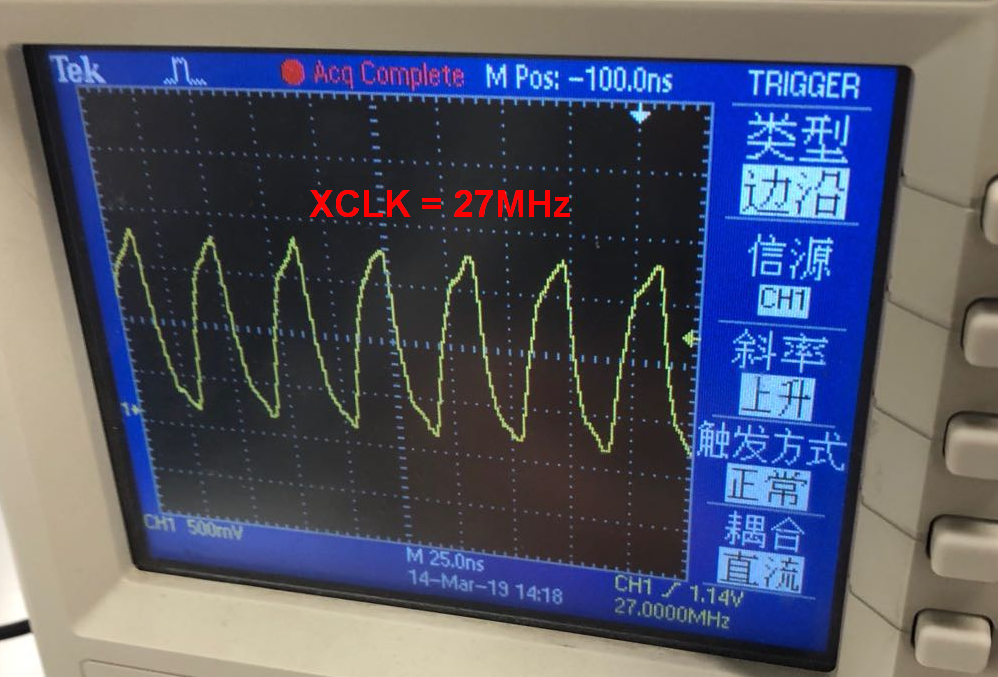

- XCLK

- PCLK

- HSYNC

- VSYNC

- SCL

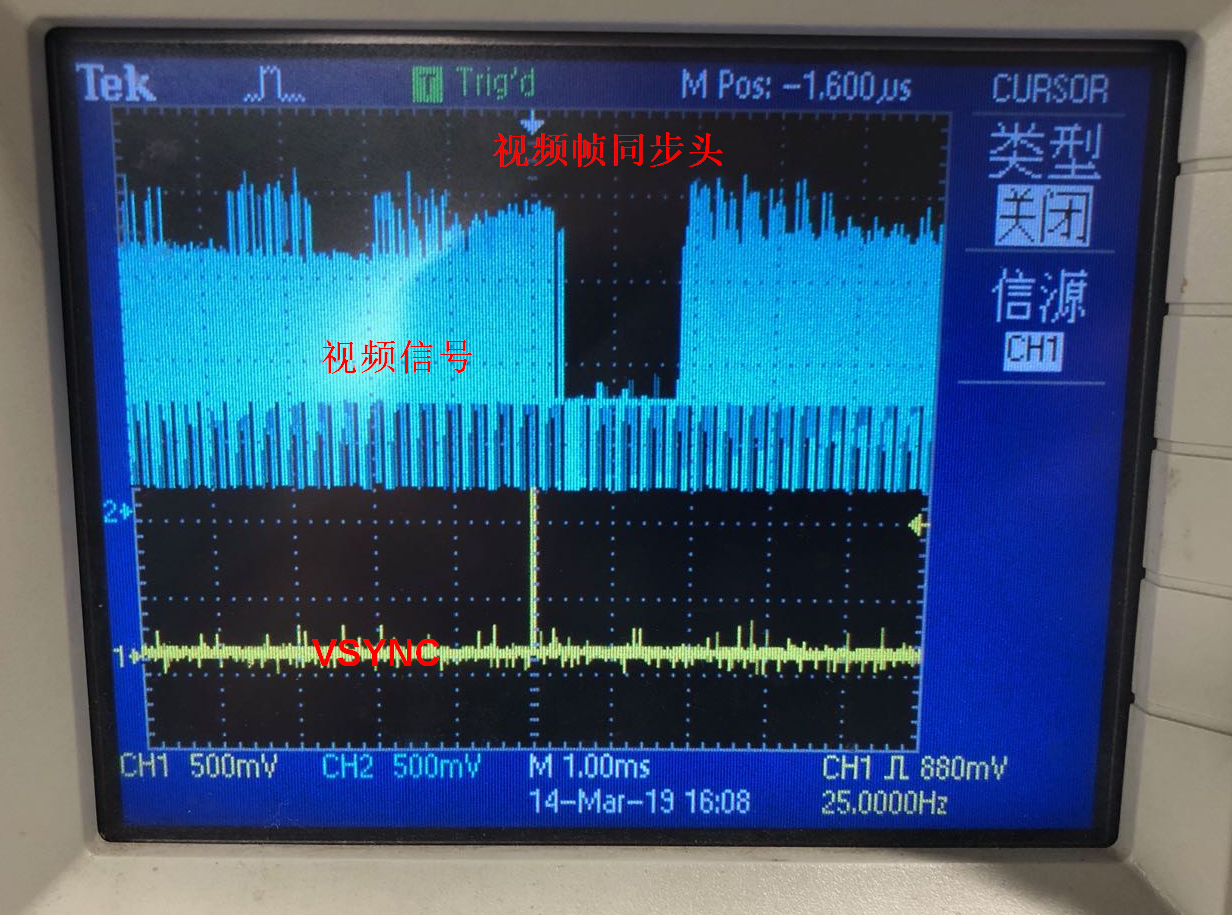

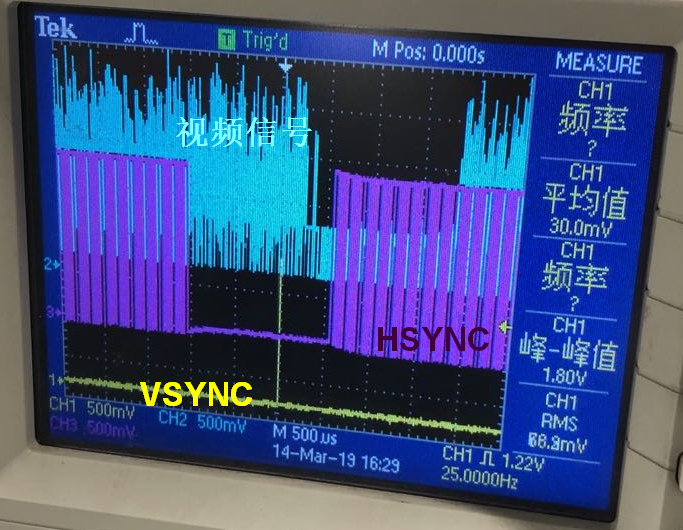

- 视频帧同步头波形

- 多波形图

最后

以上就是无私芝麻最近收集整理的关于sensor接口之DVP什么是DVPDVP时序实际测量DVP信号的全部内容,更多相关sensor接口之DVP什么是DVPDVP时序实际测量DVP信号内容请搜索靠谱客的其他文章。

发表评论 取消回复