2 实现格雷码与二进制码的相互转换

Verilog代码(用一个函数实现):

// 定义函数 完成 二进制和格雷码的相互转换

function [WIDTH:0] data_out(input op, input [WIDTH:0] data_in);

integer i;

begin

if(op == 1'b0) // ENCODE = 1'b0 二进制转为格雷码

data_out = (data_in >> 1) ^ data_in;

else if(op == 1'b1) begin // DECODE = 1'b1 格雷码转为二进制

data_out[WIDTH] = data_in[WIDTH];

for(i=WIDTH-1; i>=0; i=i-1)

data_out[i] = data_out[i+1] ^ data_in[i];

end

end

endfunction

testbench仿真代码:

module GRAY_tb();

// 定义函数 完成 二进制和格雷码的相互转换

function [WIDTH:0] data_out(input op, input [WIDTH:0] data_in);

integer i;

begin

if(op == 1'b0) // ENCODE = 1'b0 二进制转为格雷码

data_out = (data_in >> 1) ^ data_in;

else if(op == 1'b1) begin // DECODE = 1'b1 格雷码转为二进制

data_out[WIDTH] = data_in[WIDTH];

for(i=WIDTH-1; i>=0; i=i-1)

data_out[i] = data_out[i+1] ^ data_in[i];

end

end

endfunction

parameter WIDTH = 4;

parameter ENCODE = 1'b0;

parameter DECODE = 1'b1;

reg clk;

reg rst;

reg [WIDTH-1:0] data_in;

wire [WIDTH-1:0] data_encode;

wire [WIDTH-1:0] data_decode;

initial begin

clk = 0;

rst = 1;

#5 rst = 0;

#15 rst = 1;

end

initial begin

forever #2 clk = ~clk;

end

always@(posedge clk or negedge rst) begin

if(!rst)

data_in <= 0;

else begin

data_in = data_in + 1'b1;

end

end

assign data_encode = data_out(ENCODE, data_in);

assign data_decode = data_out(DECODE, data_encode);

endmodule

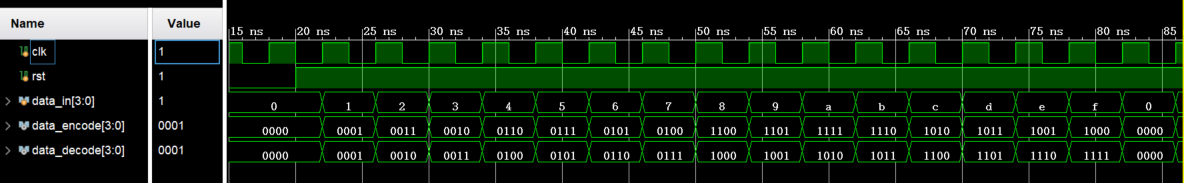

仿真波形:

最后

以上就是文艺大侠最近收集整理的关于手撕Verilog面试题专题——(2)格雷码与二进制码的相互转换2 实现格雷码与二进制码的相互转换的全部内容,更多相关手撕Verilog面试题专题——(2)格雷码与二进制码的相互转换2内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复