在我们学习中,常常需要对时钟进行分频处理,本文将介绍几种常用分频方法。

一、2的整数次幂分频

这种分频很简单,只需要设置一个计数器,对计数器进行计数,计数器的第i位则对应的2的i-1次幂分频。此方法适用于占空比为1/2,如果占空比不为1/2,则可用下面讲述的偶分频方法实现。

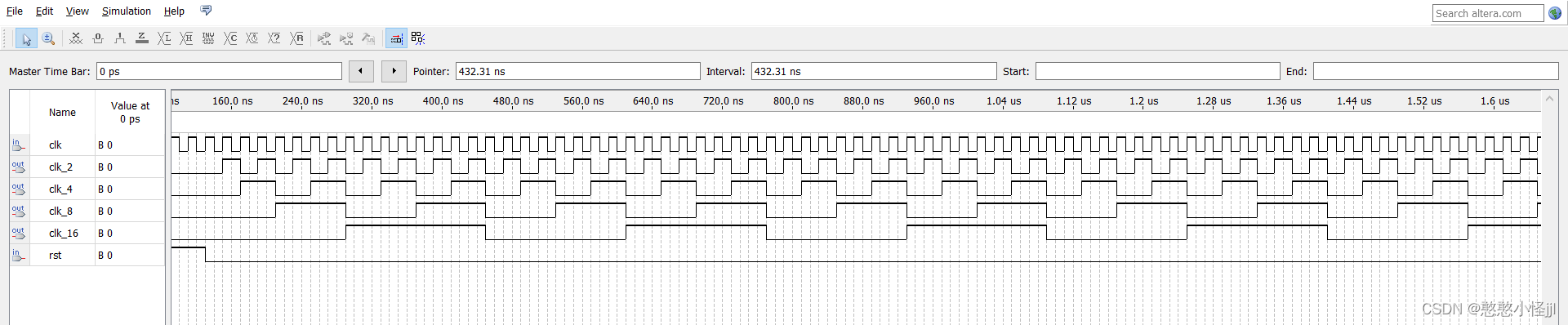

例如:现在对时钟进行2,4,8,16分频

module div_24816(

input clk,rst,

output clk_2,clk_4,clk_8,clk_16);

reg [3:0] count;

always@(posedge clk or posedge rst)

begin

if(rst)

count <= 4'd0;

else if(&count) //判断计数器的四位是否全为1

count <= 4'd0;

else

count <= count + 1'b1;

end

assign clk_2 = count[0]; //2分频

assign clk_4 = count[1]; //4分频

assign clk_8 = count[2]; //8分频

assign clk_16 = count[3]; //16分频

endmodule 仿真结果如下:

二、偶分频

首先设置一个计数器,计数器的位数根据分频系数来定,然后根据计数器的值来确定分频的占空比即可。

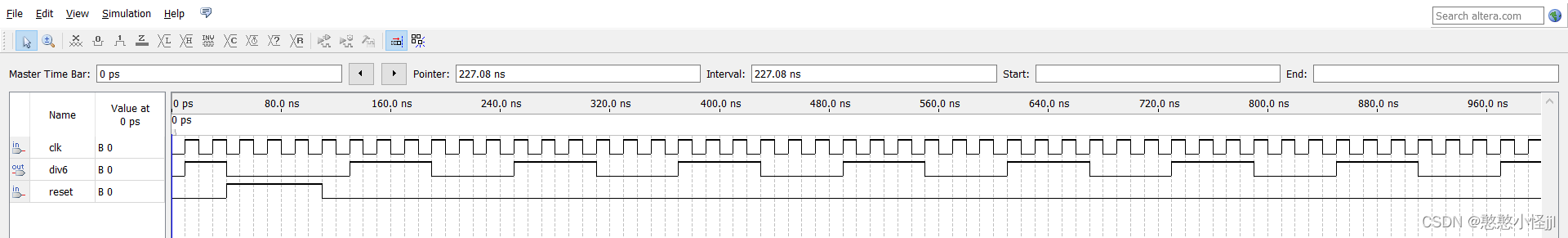

例如:现在对时钟进行6分频,要求占空比1/2

module div(

input reset,clk,

output div6);

reg div6;

reg [2:0] counter;

always @(posedge clk or posedge reset)

begin

if(reset)

counter<=0;

else

begin

if(counter==5)

counter<=0;

else

counter<=counter+1;

end

end

always @(posedge clk or posedge reset)

begin

if(reset)

div6<=0;

else if(counter<3) //设置占空比1/2

div6<=1;

else

div6<=0;

end

endmodule 仿真结果如下:

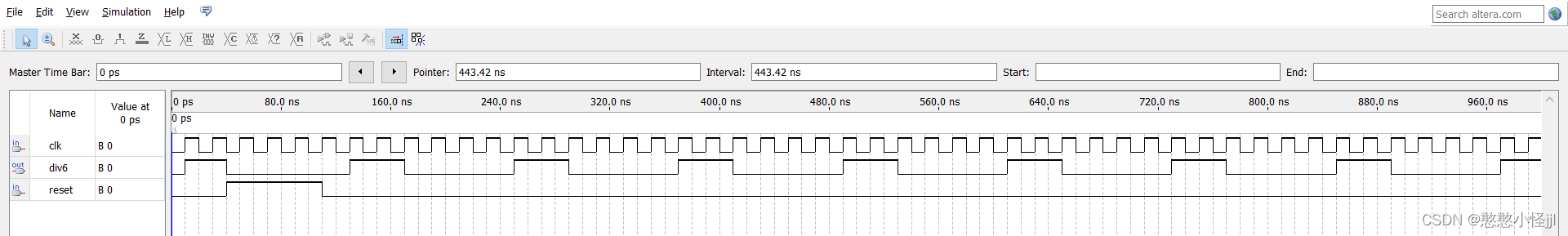

例如 :现在对时钟进行6分频,要求占空比1/3

module div(

input reset,clk,

output div6);

reg div6;

reg [2:0] counter;

always @(posedge clk or posedge reset)

begin

if(reset)

counter<=3'd0;

else

begin

if(counter==3'd5)

counter<=3'd0;

else

counter<=counter+1'b1;

end

end

always @(posedge clk or posedge reset)

begin

if(reset)

div6<=1'b0;

else if(counter<3'd2) //设置占空比1/3

div6<=1'b1;

else

div6<=1'b0;

end

endmodule 仿真结果如下:

三、奇分频

对于占空比不为1/2的奇分频,其步骤与占空比不为1/2的偶分频一样,这里不再重复说明。对于占空比为1/2的奇分频,我们的主要思想就是利用两个占空比不为1/2的信号相或得到。具体请看如下例子:

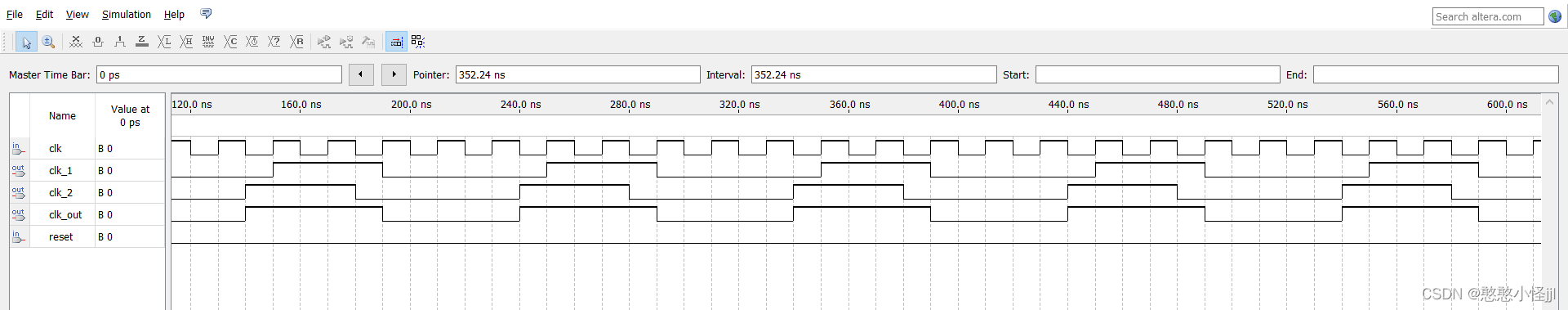

要求5分频,占空比1/2

module div(clk,clk_out,clk_1,clk_2,reset);

input clk;

input reset;

output clk_out,clk_1,clk_2;

reg clk_1;

reg clk_2;

reg [2:0] cnt;

always@(posedge clk)

begin

if(reset)

cnt <= 1'd0;

else if(cnt == 3'd4)

cnt <= 3'd0;

else

cnt <= cnt + 1'd1;

end

always@(posedge clk)

begin

if(reset)

clk_1 <= 1'd0;

else if(cnt == 3'd2)

clk_1 <= 1'd1;

else if(cnt == 3'd4)

clk_1 <= 1'd0;

else

clk_1 <= clk_1;

end

always@(negedge clk)

begin

if(reset)

clk_2 <= 1'd0;

else if(cnt == 3'd2)

clk_2 <= 1'd1;

else if(cnt == 3'd4)

clk_2 <= 1'd0;

else

clk_2 <= clk_2;

end

assign clk_out = (clk_1 | clk_2);

endmodule 仿真结果如下;

文章到此就结束了,希望上述的方法能够帮到大家!!!

最后

以上就是自信草莓最近收集整理的关于几种常用时钟分频实现方法的全部内容,更多相关几种常用时钟分频实现方法内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复