makefile 带来的好处就是——“自动化编译”。

基本语法

target ... : prerequisites ...

(tab)command

应用

巧妙利用命令,可以简化编译细节,下面是测试 makefile(源码)

CXX = g++

CPPFLAGS = -g -O0 -Wall

TARGETS = main

CPP_SRCS = $(foreach dir, ., $(wildcard $(dir)/*.cpp))

OBJS = $(patsubst %.cpp, %.o, $(CPP_SRCS))

$(TARGETS): $(OBJS)

$(CXX) $(CPPFLAGS) $(OBJS) -o $@

%.o: %.cpp

$(CXX) $(CPPFLAGS) $< -c -o $@

clean:

rm -f $(OBJS)

rm -f $(TARGETS)

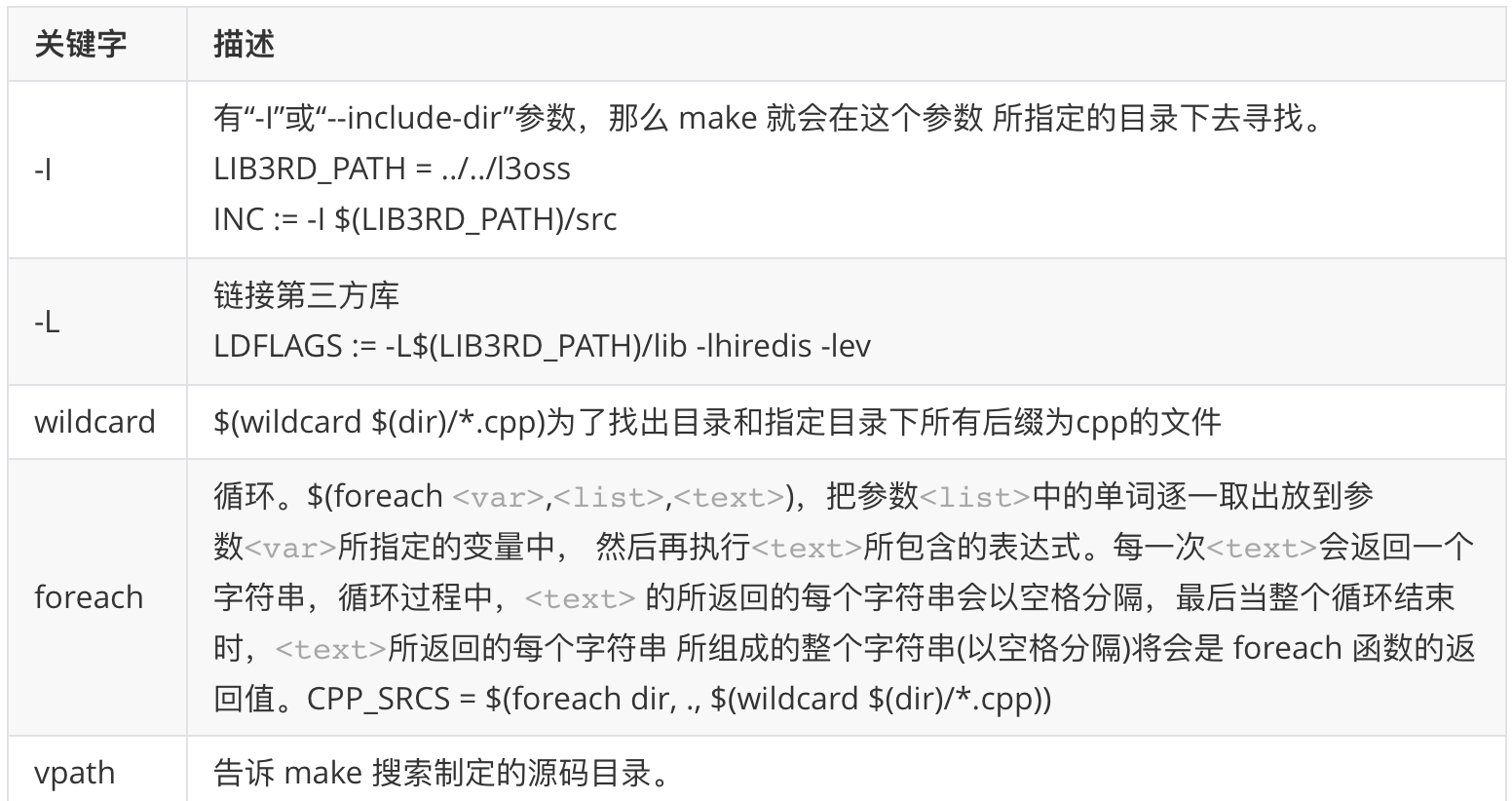

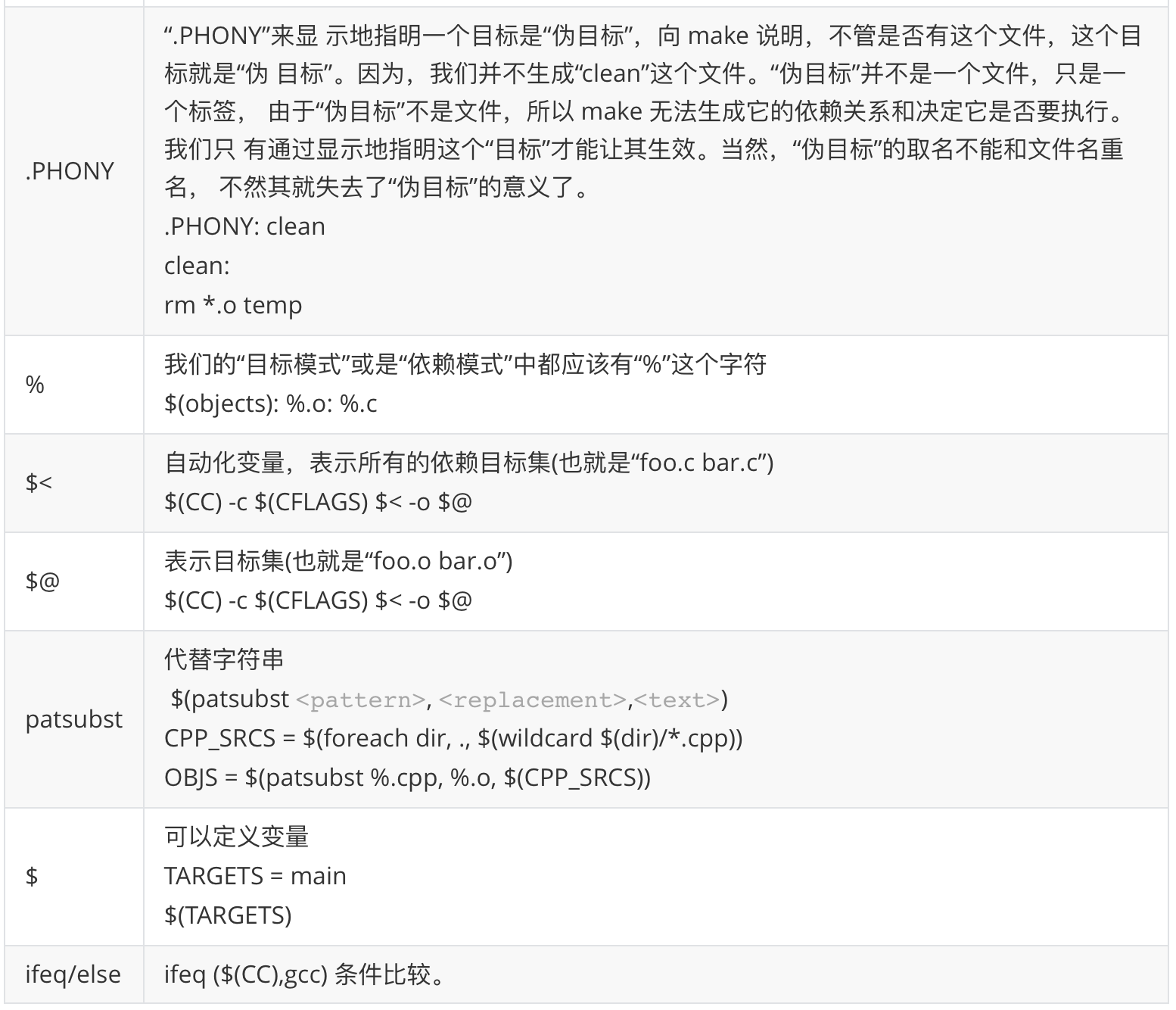

常用命令

参考

《跟我一起学 makefile》

后记

最近重温了不少基础知识,发现东西不常用,容易忘记,即便当时很明白,过后难免需要重复翻阅资料。对于核心知识点,每次重温最好结合实践把关键部分整理提取出来进行落地,不明白的地方再复盘——学习,实践,归纳,这大抵是前人说的:书会越读越薄。

最后

以上就是搞怪马里奥最近收集整理的关于makefile 常用命令的全部内容,更多相关makefile内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

![[Makefile]-1.Makefile一些常用指令](https://www.shuijiaxian.com/files_image/reation/bcimg25.png)

发表评论 取消回复