EDA(Electronic Design Automation)即电子设计自动化。EDA技术指的是以计算机硬件和系统软件为基本工作平台,以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统设计的主要表达方式,自动完成集成电子系统设计的一门新技术。EDA旨在帮助电子设计工程师在计算机上完成电路的各种设计,使得硬件设计如同软件设计一样方便快捷,为数字系统设计带来了极大的灵活性。

电子设计自动化EDA 技术, 是一种以计算机为基本工作平台, 利用计算机图形学、拓扑逻辑学、计算数学以至人工智能学等多种计算机应用学科的最新成果而开发出来的一整套软件工具。现代EDA技术是采用高级语言描述, 具有系统级仿真和综合能力。它主要采用并行工程和自顶向下的设计方法, 从系统设计入手, 在顶层进行功能方框图的划分和结构设计, 在方框图一级进行仿真、纠错, 并用VHDL、Verilog HDL 等硬件描述语言对高层次的系统行为进行描述, 在系统一级进行验证, 最后再用逻辑综合优化工具生成具体的门级逻辑电路的网表, 其对应的物理实现级可以是印刷电路板或专用集成电路ASIC。

与早期的电子CAD软件相比,EDA软件的自动化程度更高,功能更完善,运行速度更快,而且操作界面友好,有良好的数据开放性、互换性和兼容性。因此,EDA技术很快在世界各地的电子电路设计领域得到了广泛应用,并已成为新一代电子技术发展的重要方向。

现代EDA技术的基本特征是采用高级语言描述,具有系统级仿真和综合能力。以VHDL语言为代表的硬件描述语言是各种描述方法中最能体现EDA优越性的描述方法,并于1984年被IEEE确定为标准化的硬件描述语言。它有强大的行为描述能力和多层次的仿真模拟,程序结构规范,VHDL综合器性能日益完善,设计效率较高。

数字频率计是数字电路中的一个典型应用,实际的硬件设计用到的器件较多,连线比较复杂,而且会产生比较大的延时,造成测量误差、可靠性差。随着复杂可编程逻辑器件(CPLD)的广泛应用,以EDA工具作为开发手段,运用VHDL语言。将使整个系统大大简化。提高整体的性能和可靠性。

本设计用VHDL在FPGA器件上实现一种8 b数字频率计测频系统,能够用十进制数码显示被测信号的频率,不仅能够测量正弦波、方波和三角波等信号的频率,而且还能对其他多种物理量进行测量。具有体积小、可靠性高、功耗低的特点。

频率测量的方法常用的有测频法和测周法两种。

·测频法

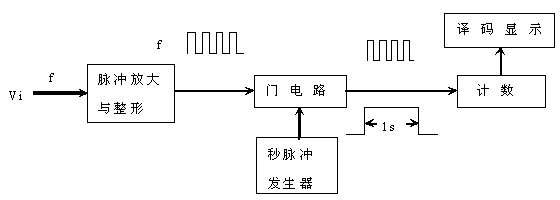

测频法的基本思想是让计数器在闸门信号的控制下计数1秒时间,计数结果是1秒内被测信号的周期数,即被测信号的频率。若被测信号不是矩形脉冲,则应先变换成同频率的矩形脉冲。测频法的原理框图如图3-1所示。

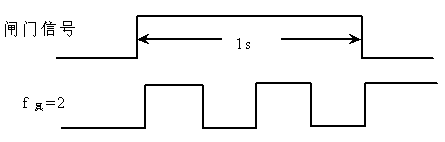

图中,秒脉冲作为闸门信号,当其为高电平时,计数器计数;低电平时,计数器停止计数。显然,在同样的闸门信号作用下,被测信号的频率越高,测量误差越小。当被测频率一定时,闸门信号高电平的时间越长,测量误差越小。但是闸门信号周期越长,测量的响应时间也越长。例如,闸门信号高电平时间为1秒,被测信号频率的真值为2Hz,如图3-2所示。

图3-1频率测量原理框图

可知,无论被测信号的频率是多少,测量时可能产生的最大绝对误差均为±1Hz,即

f测-f真=±1Hz

所以,最大相对误差为:σmax= (f测-f真)/ f真=±1/ f真

由上式可知,在闸门信号相同时,测频法的相对误差与被测信号的频率成反比。因此测频法适合于测量频率较高的信号。

图3-2 测频法的误差

·测周法

当被测信号频率较低时,为保证测量精度,常采用测周法。即先测出被测信号的周期,再换算成频率。测周法的实质是把被测信号作为闸门信号,在它的高电平的时间内,用一个标准频率的信号源作为计数器的时钟脉冲。若计数结果为N,标准信号频率为f1,则被测信号的周期为

T = T1·N

被测信号的频率为

f = 1/T1·N = f1/N

利用测周法所产生的最大绝对误差,显然也等于±1个标准信号周期。如果被测信号周期的真值为T真= T1·N,则T测= T1·(N±1)

σmax= (f测-f真)/ f真= T真/T测 – 1=±1/(N±1)

由上式可知,对于一定的被测信号,标准信号的频率越高,则N的值越大,因而相对误差越小。

3.2 数字频率计的基本设计方案

频率信号易于传输,抗干扰性强,可以获得较好的测量精度。因此,频率检测是电子测量领域最基本的测量之一。本文的数字频率计是按照计算每秒内待测信号的脉冲个数的基本原理来设计,此时取闸门时间为1秒。

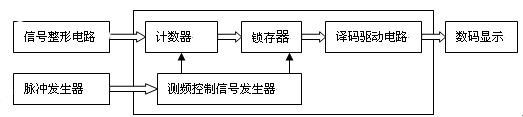

数字频率计的关键组成部分包括一个测频控制信号发生器、一个计数器和一个锁存器,另外包含信号整形电路、脉冲发生器、译码驱动电路和显示电路,其原理框图如图1所示。

工作过程:系统正常工作时,脉冲信号发生器输入1Hz的标准信号,经过测频控制信号发生器的处理,2分频后即可产生一个脉宽为1秒的时钟信号,以此作为计数闸门信号。测量信号时,将被测信号通过信号整形电路,产生同频率的矩形波,输入计数器作为时钟。当计数闸门信号高电平有效时,计数器开始计数,并将计数结果送入锁存器中。设置锁存器的好处是显示的数据稳定,不会由于周期性的清零信号而不断闪烁。最后将锁存的数值由外部的七段译码器译码并在数码管上显示。

4.2.2 分频器设计

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity jjj is

port(clkk:in std_logic;

cnt_en:out std_logic;

rst_ent:out std_logic;

load:out std_logic);

end jjj;

architecture behave of jjj is

signal div2clk:std_logic;

begin

process(clkk)

begin

if(clkk'event and clkk='1')then

div2clk<=not div2clk;

end if;

end process;

process(clkk,div2clk)

begin

if(clkk='0' and div2clk='0')then

rst_ent<='1';

else rst_ent<='0';

end if;

end process;

load<=not div2clk;

cnt_en<=div2clk;

end behave;

4.2.3计数器模块的设计

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity jjj2 is

port(fin:in std_logic;

clr:in std_logic;

enabl:in std_logic;

dout :out std_logic_vector(31 downto 0));

end jjj2;

architecture beha of jjj2 is

signal cq:std_logic_vector(31 downto 0);

begin

process(fin,clr,enabl)

begin

if(clr='1')then cq<=(others=>'0');

elsif(fin'event and fin='1') then

if(enabl='1')then cq<=cq+'1';

if cq(3 downto 0)="1001" then cq(3 downto 0)<="0000";cq(31 downto 4)<=cq(31 downto 4)+1;

if cq(7 downto 4)="1001" then cq(7 downto 4)<="0000";cq(31 downto 8)<=cq(31 downto 8)+1;

if cq(11 downto 8)="1001" then cq(11 downto 8)<="0000";cq(31 downto 12)<=cq(31 downto 12)+1;

if cq(15 downto 12)="1001" then cq(15 downto 12)<="0000";cq(31 downto 16)<=cq(31 downto 16)+1;

if cq(19 downto 16)="1001" then cq(19 downto 16)<="0000";cq(31 downto 20)<=cq(31 downto 20)+1;

if cq(23 downto 20)="1001" then cq(23 downto 20)<="0000";cq(31 downto 24)<=cq(31 downto 24)+1;

if cq(27 downto 24)="1001" then cq(27 downto 24)<="0000";cq(31 downto 28)<=cq(31 downto 28)+1;

if cq(31 downto 28)="1001" then cq(31 downto 28)<="0000";

end if;

end if;

end if;

end if;

end if;

end if;

end if;

end if;

end if;

end if;

end process;

dout<=cq;

end beha;

4.2.4 锁存器模块设计

当系统正常工作时,脉冲发生器提供的1 Hz的输入信号,经过测频控制信号发生器进行信号的变换,产生计数信号,被测信号通过信号整形电路产生同频率的矩形波,送入计数模块,计数模块对输入的矩形波进行计数,将计数结果送入锁存器中,保证系统可以稳定显示数据。

library ieee;

use ieee.std_logic_1164.all;

entity jjj1 is

port(lk:in std_logic;

din:in std_logic_vector(31 downto 0);

dout:out std_logic_vector(31 downto 0) );

end jjj1;

architecture beha of jjj1 is

begin

process(lk,din)

begin

if(lk'event and lk='1')then

dout<=din;

end if;

end process;

end beha;

·系统仿真:

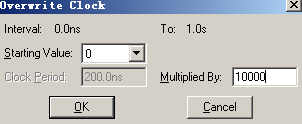

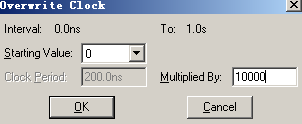

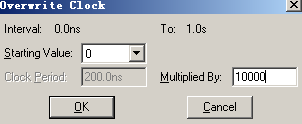

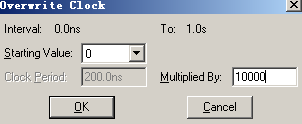

最后我们开始系统的仿真,由于在仿真过程中,1S钟时间将会仿真很长时间,所以我们考虑缩短仿真时间,我们首先假设系统时钟频率1hz对于设置参数为如下所示(左图),而输入的被测试信号的频率为(右图):

图4-5 参数设置一

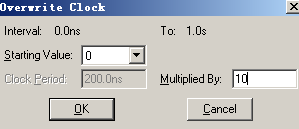

这里表示输入的时钟是系统时钟的10倍,即10hz,那么其仿真结果为:

图4-6 系统仿真结果

检测到信号的频率为10hz。

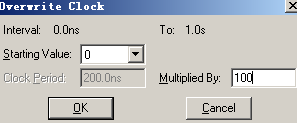

下面再做两次仿真:

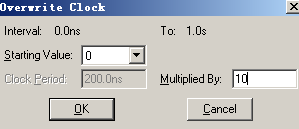

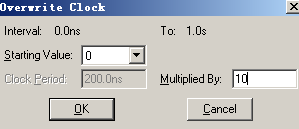

图4-7 参数设置二

这里表示输入的时钟是系统时钟的100倍,即100hz,那么其仿真结果为:

图4-7 系统仿真结果

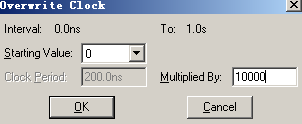

图4-8 参数设置三

这里表示输入的时钟是系统时钟的1000倍,即1khz,那么其仿真结果为:

图4-9 系统仿真结果

由于MAXPLUSII软件内部其最大设置为32000,因此在该系统中,我们无法仿真10Mhz的效果,但是其实际上由于显示的是8位,即10M。那么在实际的应用中,我们可以测量到10Mhz的信号。

最后

以上就是温柔豌豆最近收集整理的关于基于EDA技术的频率计系统设计的全部内容,更多相关基于EDA技术内容请搜索靠谱客的其他文章。

发表评论 取消回复