本文首发于个人博客

1.AXI总线结构

AXI总线由5个通道构成:

| 通道名称 | 通道功能 | 数据流向 |

|---|---|---|

| read address | 读地址通道 | 主机->从机 |

| read data | 读数据通道(包括数据通道和读响应通道) | 从机->主机 |

| write address | 写地址通道 | 主机->从机 |

| write data | 写数据通道(包括数据通道和每8bit一个byte的写数据有效信号) | 主机->从机 |

| write response | 写响应通道 | 从机->主机 |

1.1.AXI通道

读操作的通道如下图所示

写操作的通道如下图所示

1.2.AXI系统

常见的标准AXI系统如下图所示,通常包括:

- AXI master:AXI通信主机

- AXI slave:AXI通信从机

- AXI interconnect:AXI通信通路

AXI接口协议可用于:

- AXI master - AXI interconnect的连接

- AXI slave - AXI interconnect的连接

- AXI master - AXI slave的连接

1.3.AXI接口

1.3.1.全局信号

| 信号名 | 来源 | 描述 |

|---|---|---|

| ACLK | system clock | 全局时钟信号 |

| ARESTn | system reset | 全局复位信号,低有效 |

1.3.2.写地址通道

| 信号名 | 来源 | 描述 |

|---|---|---|

| AWID | master | 写地址ID(用于区分该地址属于哪个写地址组) |

| AWADDR | master | 写地址 |

| AWLEN | master | 突发长度 |

| AWSIZE | master | 突发尺寸(每次突发传输的最长byte数) |

| AWBURST | master | 突发方式(FIXED,INCR,WRAP) |

| AWCACHE | master | 存储类型(标记系统需要的传输类型) |

| AWPROT | master | 保护模式 |

| AWQOS | master | QoS标识符 |

| AWREGION | master | region标识符(当slave有多种逻辑接口时标识使用的逻辑接口) |

| AWUSER | master | 用户自定义信号 |

| AWVALID | master | 写地址有效信号(有效时表示AWADDR上地址有效) |

| AWREADY | master | 写从机就绪信号(有效时表示从机准备好接收地址) |

1.3.3.写数据通道

| 信号名 | 来源 | 描述 |

|---|---|---|

| WDATA | master | 写数据 |

| WSTRB | master | 数据段有效(标记写数据中哪几个8位字段有效) |

| WLAST | master | last信号(有效时表示当前为突发传输最后一个数据) |

| WUSER | master | 用户自定义信号 |

| WVALID | master | 写有效信号(有效时表示WDATA上数据有效) |

| WREADY | slave | 写ready信号(有效时表示从机准备好接收数据) |

1.3.4.写响应通道

| 信号名 | 来源 | 描述 |

|---|---|---|

| BID | slave | 响应ID |

| BRESP | slave | 写响应 |

| BUSER | slave | 用户自定义信号 |

| BVALID | slave | 写响应信号有效 |

| BREADY | master | 写响应ready(主机准备好接受写响应信号) |

1.3.5.读地址通道

| 信号名 | 来源 | 描述 |

|---|---|---|

| ARID | master | 读地址ID |

| ARADDR | master | 读地址 |

| ARLEN | master | 突发长度 |

| ARSIZE | master | 突发尺寸(每次突发传输的byte数) |

| ARBURST | master | 突发类型(FIXED,INCR,WRAP) |

| ARCACHE | master | 存储类型 |

| ARPROT | master | 保护类型 |

| ARQOS | master | QoS标识符 |

| ARREGION | master | 区域标识符 |

| ARUSER | master | 用户自定义 |

| ARVALID | master | 读地址有效(有效时表示ARADDR上地址有效) |

| ARREADY | slave | 写有效信号(有效时表示从机准备好接收读地址) |

1.3.6.读数据通道

| 信号名 | 来源 | 描述 |

|---|---|---|

| RID | slave | 读ID标签 |

| RDATA | slave | 读数据 |

| RRESP | slave | 读响应 |

| RLAST | slave | 有效时表示为突发传输的最后一个 |

| RUSER | slave | 用户自定义 |

| RVALID | slave | 读数据有效信号 |

| RREADY | master | 主机就绪信号(有效时表示) |

1.3.7.低功耗接口信号

| 信号名 | 来源 | 描述 |

|---|---|---|

| CSYSREQ | Clock controller | 该信号有效时,系统退出低功耗模式 |

| CSYSACK | Peripheral device | 退出低功耗模式应答信号 |

| CACTIVE | Peripheral device | 外设申请时钟信号 |

2.AXI接口时序

2.1.复位

复位信号可以异步复位,但必须同步释放,复位时,信号要求如下:

- 主机驱动的所有VALID信号(ARVALID, AWVALID和WVALID)必须被拉低

- 从机驱动的所有VALID信号(RVALID和BVALID)必须被拉低

- 其他信号无要求

2.2.基本传输

2.2.1.握手信号

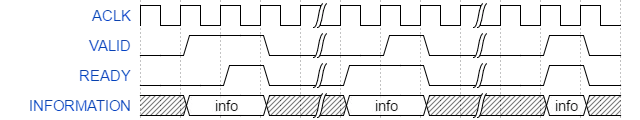

握手信号包括VALID和READY信号,传输行为仅在VALID和READY同时有效时发生。其中:

- VALID信号表示地址/数据/应答信号总线上的信号是有效的,由传输发起方控制

- READY信号表示传输接收方已经准备好接收,由传输接收方控制

VALID和READY的先后关系具有三种情况:

- VALID先有效,等待READY有效后完成传输(VALID一旦有效后在传输完成前不可取消)

- READY先有效,等待VALID有效后完成传输(READY可以在VALID有效前撤销)

- VALID和READY同时有效,立刻完成传输

此外,需要注意的是允许READY信号等待VALID信号再有效,即即使从机准备好,也可以不提供READY信号,等到主机发送VALID信号再提供READY信号。对应的VALID信号不允许等待READY信号,即不允许VALID等待READY信号拉高后再拉高,否则容易产生死锁现象。

2.2.1.1.命令通道握手(读地址,写地址,写响应)

- 仅当地址等信息有效时,才拉高VALID,该VALID必须保持直到传输完成(READY置位)

- READY默认状态不关心,仅当准备好接收时拉高READY

2.2.1.2数据通道握手(写数据和读地址)

- 突发读写模式下,仅数据信息有效时才拉高VALID,该VALID必须保持直到传输完成。当突发传输最后一个数据发送时拉高LAST信号

- READY默认状态不关心,仅当准备好接收时拉高READY

2.2.2.通道顺序

传输中,通道传输的先后有以下规定

- 写响应通道传输必须在写操作完成以后进行

- 读数据通道传输必须在读地址通道传输后进行

- 必须遵循一系列的状态依赖关系

下文中会使用一些图描述依赖关系。图表中,单箭头表示可以等待有效再置位,双重箭头表示必须等待有效再置位

2.2.2.1.读操作顺序

上图为读操作的依赖关系,ARREADY可以等待ARVALID信号,RVALID必须等待ARVALID和ARREADY同时有效后(一次地址传输发生)才能能有效

2.2.2.2.写操作顺序

AXI3中写操作中唯一的强依赖关系是写响应通道BVALID,仅当WVALID和WREADY信号同时有效(数据传输完成)且WLAST信号有效(突发传输的最后一个数据传输完成)后才会被置位。

在AXI4中,定义了额外的依赖关系,即BVALID必须依赖AWVALID、AWREADY、WVALID和WREADY信号。

3.数据结构

3.1.地址通道数据结构

AXI总线是基于突发传输的总线,若主机要开始一次突发传输,需要传输一次地址和相关控制信号,之后从机自动计算地址,但一次突发传输的地址范围不能跨越4KB。

3.1.1.突发传输信息

3.1.1.1.突发长度(AxLEN)

突发长度为每次突发传输的传输次数,范围限制1~16(AXI4增量模式1~256)且不能跨越4kb的地址空间,每次突发传输不允许提前终止(可以通过关闭所有数据字段的方式使一段传输数据无效,但传输行为必须完成)。每次传输的突发长度为AxLEN[3:0] + 1(AXI增量模式AxLEN[7:0] + 1)

- ARLEN[7:0]:读地址通道的突发长度接口

- AWLEN[7:0]:写地址通道的突发长度接口

对于回卷模式突发传输,突发长度仅能是2,4,8或16。

3.1.1.2.突发尺寸(AxSIZE)

突发尺寸为每次传输的byte数量,与突发传输的地址预测相关性很强。每次的突发尺寸不能超过数据通道的宽度;若突发尺寸小于数据通道宽度,需要指定哪些位数是有效的。突发尺寸为2AxSIZE[2:0]。

- ARSIZE[2:0]:读地址通道突发尺寸

- AWSIZE[2:0]:写地址通道突发尺寸

3.1.1.3.突发类型(AxBURST)

AXI支持三种突发类型:

- FIXED(AxBURST[1:0]=0b00):固定突发模式,每次突发传输的地址相同

- INCR(AxBURST[1:0]=0b01):增量突发模式,突发传输地址递增,递增量与突发尺寸相关

- WRAP(AxBURST[1:0]=0b10):回卷突发模式,突发传输地址可溢出性递增,突发长度仅支持2,4,8,16。地址空间被划分为长度【突发尺寸*突发长度】的块,传输地址不会超出起始地址所在的块,一旦递增超出,则回到该块的起始地址。

3.1.2.存储类型(AxCACHE)

AXI4可支持不同的存储类型,AxCACHE[3:0]用于描述不同的存储类型,如下图所示

| ARCACHE[3:0] | AWCACHE[3:0] | Memory type |

|---|---|---|

| 0000 | 0000 | Device Non-bufferable |

| 0001 | 0001 | Device Bufferable |

| 0010 | 0010 | Normal Non-cacheable Non-bufferable |

| 0011 | 0011 | Normal Non-cacheable Bufferable |

| 1010 | 0110 | Write-through No-allocate |

| 1110 (0110) | 0110 | Write-through Read-allocate |

| 1010 | 1110 (1010) | Write-through Write-allocate |

| 1110 | 1110 | Write-through Read and Write-allocate |

| 1011 | 0111 | Write-back No-allocate |

| 1111 | (0111) 0111 | Write-back Read-allocate |

| 1011 | 1111 (1011) | Write-back Write-allocate |

| 1111 | 1111 | Write-back Read and Write-allocate |

3.1.3.Qos标识符(AxQOS)

AXI4总线支持QoS,该标识符AxQOS[3:0]表示服务的优先级

3.1.4.REGION标识符(AxREGION)

region标识符用于指定选用的高级逻辑接口类型,当使用该标识符AxREGION[3:0]时,表示有多个逻辑接口共享该物理接口

3.1.5.权限标识符(AxPROT)

权限标识符AxPROT[2:0]用于防止非法传输

3.1.6.用户自定义(AxUSER)

用户自定义数据

3.2.数据通道数据结构

3.2.1.数据选通(WSTRB)

WSTRB的每一位对应数据中的8位(1字节),用于标志数据中的对应字节是否有效。即当WSTRB[n] = 1时,标志数据中WDATA[(8n)+7: (8n)]部分有效。

3.2.2.数据(xDATA)

3.2.2.1.窄带传输(Narrow transfers)

当传输的数据位宽小于xDATA总线带宽时,为窄带传输,每次使用的数据位数不同:

- 固定地址的突发下,使用同一段数据信号线

- 在递增地址和包装地址的突发下,使用不同段信号线

上图为地址递增突发下,在32位数据信号下使用8bit传输的窄带传输使用的位数图。第一次传输使用0~7位,第二次使用8~15位,依次递增;在第五次传输时回到开头使用0~7位

3.2.2.2.不对齐传输(Unaligned transfers)

当传输位宽超过1byte,起始地址不为数据总线硬件带宽(byte单位)整数倍时,为不对齐传输。不对齐传输的时候需要配合数据选通在第一次传输时将某几个byte置为无效,使第二次突发传输的起始地址(从机自动计算)为突发尺寸的整数倍。

如图,突发尺寸为4byte,若要对齐传输,起始地址要为4的整数倍。图中起始地址为0x07,因此为非对齐传输。第一次传输时,前3个数据为无效字段,可以使用数据选通WSTRB将前3个byte置为无效。

上图是在窄带传输下的非对齐传输启动。传输带宽为32bit,每次传输使用16bit,由于是窄带传输,因此每次交替使用低字节和高字节。现在关注启动状态,由于启动地址为7,而硬件带宽为8bit,则必须由地址0启动,设置前7个字段为无效,那么下次传输从地址8开始,满足不对齐传输。

3.2.3.用户自定义(*USER)

用户自定义数据

3.3.应答通道数据结构

3.3.1.响应信号(*RESP)

针对读和写均有响应的响应信号:

- BRESP[1:0]写响应信号,每次突发传输完成后

- RRESP[1:0]读响应信号(位于读数据通道)

响应信号含义如下:

- OKAY(00):正常访问正确/特权访问失败/不支持特权访问

- EXOKAY(01):特权访问成功

- SLVERR(10):从机错误,传输失败

- DECERR(11):互连解码错误,传输失败

3.3.2.用户自定义

用户自定义数据

4.传输特性

AXI从机分为两种:

- 存储器从机(Memory Slave):需要支持所有传输特性

- 外设从机(Peripheral Slave):仅需要支持指定的操作,但是可以保证所有类型的传输完成(不要求非指定的操作响应正确)

AxCACHE用于指定传输特性,传输特性用于标定传输如何在系统中进行和系统级缓存如何处理传输。

4.1.存储器特性

存储器特性包括4个位,如下所示:

AxCACHE[0](Bufferable):AxCACHE[0]表示传输过程中是否有缓存,当该位置为1时,表示表示传输路径上具有buffer(可延迟transaction到达最终点的时间)

-

AxCACHE[1](Modifiable):标记传输是否可以被修改/优化,当其置0时,每个传输将不会被更改,具体来说,AxADDR、AxSIZE、AxLEN、AxBURST、AxLOCK和AxPROT信号不会被修改(地址,突发传输信息,传输隐私信息不被修改)。但是AxCACHE[0]、ID和QoS可能被修改,同时,一个突发长度长于16的突发传输可能被切开,但是保证传输效果相同。当该位置1时,除了以上可能发生的改变,另外:

- 多个传输可能被合并为一个传输,一个传输可能被切分为多个传输

- 读传输在从机端读出的数据可能多于主机的请求(多的数据被保存在cache中用于优化数据访问)

- 写传输可能访问到超过主机请求的地址范围,妥善使用WSTRB保证仅有需要的地址被覆盖

另外,AxLOCK和AxPROT信号仍然不能被改变,同时需要注意的是:AxCACHE[0]=0,具有相同的AXI ID和指向相同的从机的一系列传输的顺序不能改变。

AxCACHE[2](Read-allocate)和AxCACHE[3](Write-allocate):读写操作前是否检查缓存以优化传输

4.2.存储器类型

通过ARCACHE和AWCACHE的不同定义不同的存储器类型

最后

以上就是碧蓝小松鼠最近收集整理的关于AXI学习笔记-11.AXI总线结构2.AXI接口时序3.数据结构4.传输特性的全部内容,更多相关AXI学习笔记-11内容请搜索靠谱客的其他文章。

发表评论 取消回复