首先感谢知乎用户ljgibbs的文章,本文部分摘自《深入 AXI4 总线(一)握手机制》,主要用于自己查漏补缺。

原文链接:https://zhuanlan.zhihu.com/p/44766356

1 双向流控制传输速率

VALID/READY 机制作为一种双向流控机制,可以使发送接收双方都有能力控制传输速率。

发送方置高 VALID 信号表示发送方已经将数据,地址或者控制信息放到的写总线上,并保持。接收方置高 READY 信号表示接收方已经做好接收的准备。所谓的双向流控机制,指的是发送方通过 VALID 信号置起控制发送速度的同时,接收方也可以通过 READY 信号的置起与否控制接收速度,反压发送方的发送速度。

当双方的信息同时为高,时钟上升沿到达后,一次数据传输完成,在 1 到 n 次时钟上升沿后,双方传完了要传的信息后,两信号同时拉低。

2 VALID和READY信号

2.1 VILID相关特性

协议规定:VALID 信号一旦置起就不能拉低,直到此次传输完成。对于接收方编程来说,检测到 VALID 信号置起,如果系统正忙,完全可以让发送方等待,发送方在完成传输之前都不会置低 VALID 信号,不需要考虑发送方撤销传输的可能。

协议另外规定:发送方不能在置起 VALID 信号之前就光等待 READY 信号。

这句阅读理解有点难,原文为:![]()

作者个人从总线接口编程的角度理解,READY 信号可能先到达,如下图的情况。但是发送方编程时,不能依赖 READY 信号先到达的情况。不能将 READY 信号置高作为置高 VALID 的条件,比如将 READY 信号通过组合逻辑生成 VALID 信号。

换句话说,发送方准备发送,置起 VALID 信号是完全主动的过程。接收方按照协议可以依赖发送方,但如果此时发送方也依赖接收方,就会造成死锁的情况,所以协议在这里规定了 VALID 信号的主动性。

2.2 READY相关特性

READY 信号很自由,可以等待 VALID 信号到来再做响应,但也完全可以在 VALID 信号到来前就置高,表示接收端已经做好准备了。

READY 信号与 VALID 不同,接收方可以置起 READY 之后发现:其实我好像还挺忙,然后拉低 READY 信号。只要此时 VALID 信号没有置起,这种操作是完全可以。

3.读写操作

3.1写操作

首先主机在写地址通道上写地址和控制信息。在写地址操作结束之后,即主机确保从机已经获得了此次传输的地址和控制信息后,才开始在写数据通道上写数据。从机在写回复通道上,将此次写传输的状态回复给主机。一般来说,写数据都发生在写地址操作之后,但也不是绝对的,在有些情况下,可以先写数据。但是,所有情况下,写回复必然是在写数据之后,是对此次写数据的状态回复。

3.2读操作

读操作只涉及两个通道,首先主机在读地址通道上写入想要读取的数据的地址以及控制信息。从机在接收到地址后,将该地址上的数据通过读数据通道发送给主机。

小结:在读数据以及写数据两条数据通道中,传输一次突发传输中的最后一个数据,必须要给出 LAST 信号,来标识这是此次突发传输中的最后一个数据。如果缺少 LAST 信号会破坏 AXI 总线的工作状态。

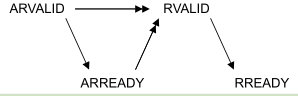

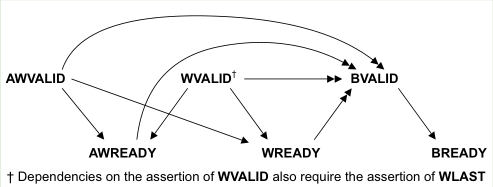

4 通道握手信号依赖关系

为防止死锁,通道握手信号需要遵循一定的依耐关系。①VALID信号不能依耐READY信号。②AXI接口可以等到检测到VALID才断言对应的READY,也可以检测到VALID之前就断言READY。下面有几个图表明依耐关系,单箭头指向的信号能在箭头起点信号之前或之后断言;双箭头指向的信号必须在箭头起点信号断言之后断言。

读传输握手信号依赖关系

读的数据必须在跟读的地址后面,对于读操作,没有地址,就没有数据。

以AXI4_LITE源代码分析,印证上面依赖关系

if (~axi_arready && S_AXI_ARVALID)

begin

// indicates that the slave has acceped the valid read address

axi_arready <= 1'b1;

// Read address latching

axi_araddr <= S_AXI_ARADDR;

end if (axi_arready && S_AXI_ARVALID && ~axi_rvalid)

begin

// Valid read data is available at the read data bus

axi_rvalid <= 1'b1;

axi_rresp <= 2'b0; // 'OKAY' response

end

写传输握手信号依赖关系

写数据可以比写地址先传,但是BVALID必须在写地址和写数据都完成后才能被声明

以AXI4_LITE源代码分析,印证上面依赖关系

if (~axi_awready && S_AXI_AWVALID && S_AXI_WVALID && aw_en)

begin

// slave is ready to accept write address when

// there is a valid write address and write data

// on the write address and data bus. This design

// expects no outstanding transactions.

axi_awready <= 1'b1;

aw_en <= 1'b0;

end if (~axi_wready && S_AXI_WVALID && S_AXI_AWVALID && aw_en )

begin

// slave is ready to accept write data when

// there is a valid write address and write data

// on the write address and data bus. This design

// expects no outstanding transactions.

axi_wready <= 1'b1;

end

if (axi_awready && S_AXI_AWVALID && ~axi_bvalid && axi_wready && S_AXI_WVALID)

begin

// indicates a valid write response is available

axi_bvalid <= 1'b1;

axi_bresp <= 2'b0; // 'OKAY' response

end // work error responses in future5 复位初始化

(1)在复位的时候,Master必须把ARVALID,AWVALID,WVALID拉低。

(2)在复位的时候,Slave必须把RVALID和BVALID拉低

最后

以上就是迅速小懒猪最近收集整理的关于AXI总线(一):握手机制 首先感谢知乎用户ljgibbs的文章,本文部分摘自《深入 AXI4 总线(一)握手机制》,主要用于自己查漏补缺。原文链接:https://zhuanlan.zhihu.com/p/447663561 双向流控制传输速率2 VALID和READY信号3.读写操作的全部内容,更多相关AXI总线(一):握手机制 首先感谢知乎用户ljgibbs的文章,本文部分摘自《深入内容请搜索靠谱客的其他文章。

发表评论 取消回复