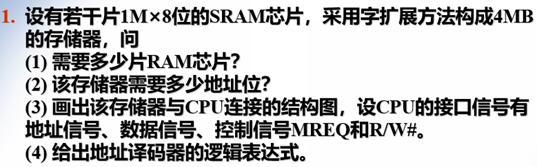

考点:字位扩展;地址译码器的逻辑表达式;存储器与CPU连接图

解:(1)因为采用了字扩展,片数

=

4

/

1

=

4

=4/1=4

=4/1=4 片

(2)地址位

=

l

o

g

2

4

M

=

22

=log_2^4M=22

=log24M=22

(3)

(4)因此,地址译码器表达式为

A

21

′

A

20

′

Y

0

′

+

A

21

′

A

20

Y

1

′

+

A

21

A

20

′

Y

′

2

+

A

21

A

20

Y

3

′

A '_{21} A'_{20} Y'_0+A'_{21} A_{20} Y'_1+A_{21} A'_{20} Y' 2+A_{21} A_{20} Y'_3

A21′A20′Y0′+A21′A20Y1′+A21A20′Y′2+A21A20Y3′(设

A

21

A_{21}

A21 为最高位)

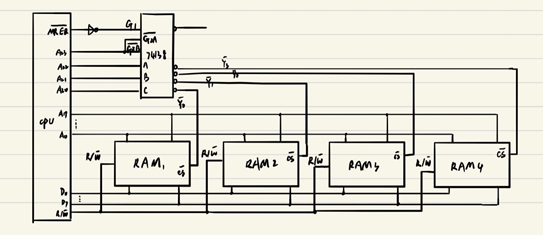

考点:字位扩展;存储器与CPU连接图

解:(1)需要字位扩展,其中

2048

K

256

K

=

8

frac{2048K}{256K}=8

256K2048K=8个作字扩展,

32

8

=

4

frac{32}{8}=4

832=4个作位扩展

(2)共需要

8

×

4

=

32

8×4=32

8×4=32个 RAM 芯片

(3)地址位

=

l

o

g

2

2048

K

=

21

=log_2^{2048K}=21

=log22048K=21位

(4)

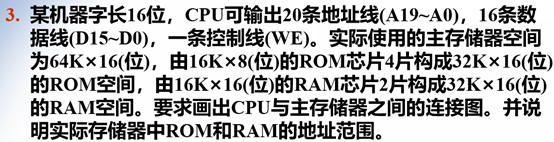

考点:字位扩展;存储器与CPU连接图;地址范围

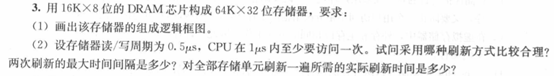

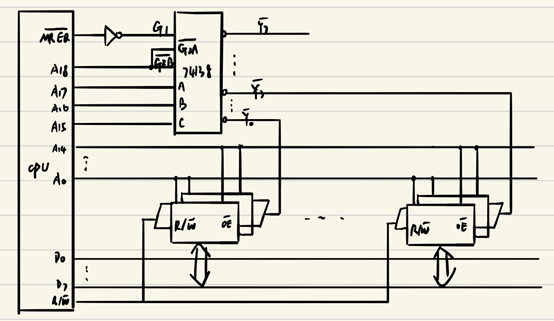

解:由题意可知,CPU与主存储器的连接图为:

ROM地址范围为:0000H-7FFFH(0~32K)

RAM地址范围为:8000H-FFFFH(32K~64K)

课本P111 1、2、3、4(1)(2)、5、6、7、8、9、11、13、14、15、19、20、21、22、24

考点:字位扩展

解:(1)32位字长为4字节,因此可存储字节数

=

2

20

×

4

=

2

22

=

4

M

=2^{20}×4=2^{22}=4M

=220×4=222=4M

(2)存储器容量为

1

M

×

32

1M×32

1M×32位,则需要进行字位扩展。字扩展需

1

M

512

K

=

2

frac{1M}{512K}=2

512K1M=2 片,位扩展需

32

8

=

4

frac{32}{8}=4

832=4 片。总共需要

2

×

4

=

8

2×4=8

2×4=8 片

(3)字扩展需要 2 片,因此只需 1 位地址进行芯片选择

考点:字位扩展

解:(1)需要进行字扩展,需要内存条数

=

2

26

16

M

=

4

=frac{2^{26}}{16M}=4

=16M226=4

(2)需要进行字位扩展。字扩展需要

16

M

4

M

=

4

frac{16M}{4M}=4

4M16M=4 片,位扩展需要

64

8

=

8

frac{64}{8}=8

864=8 片。共需要

4

×

8

=

32

4×8=32

4×8=32 片

(3)共需

32

×

4

=

128

32×4=128

32×4=128 片 DRAM 芯片。内存条容量为

16

M

×

64

16M×64

16M×64位,需要 24 根地址线(A23-A0)完成内存条内存储单元寻址。一共有4个内存条,使用2根高位地址线(A25-A24),通过译码器译码产生片选信号对各模块进行选择

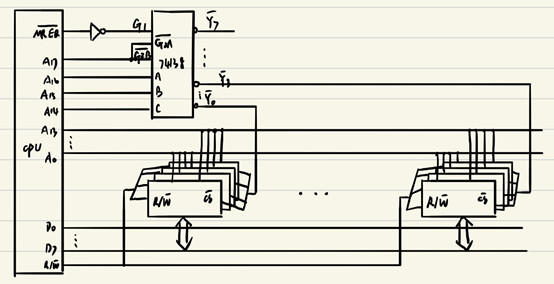

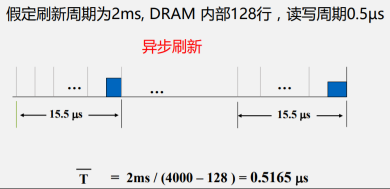

考点:字位扩展;存储器刷新

解:(1)需要进行字位扩展。字扩展需要

64

K

16

K

=

4

frac{64K}{16K}=4

16K64K=4 片,位扩展需要

32

8

=

4

frac{32}{8}=4

832=4 片。共需要

4

×

4

=

16

4×4=16

4×4=16 片

(2)矩阵存储元规模为

128

×

128

×

16

128×128×16

128×128×16 位,存储行数

=

128

=128

=128行,刷新周期 2ms,则 1 个刷新周期含

2

m

s

0.5

μ

s

=

4000

frac{2ms}{0.5μs}=4000

0.5μs2ms=4000个读写周期。

若采用集中式刷新,128 个读写周期用来刷新,死时间

=

128

×

0.5

μ

s

=

64

μ

s

=128×0.5μs=64μs

=128×0.5μs=64μs,死时间过长不可取;

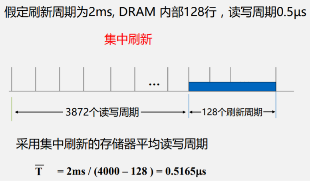

若采用分布式(分散)刷新,每行刷新插入到读写周期中,则读写周期变为

2

×

0.5

μ

s

=

1

μ

s

2×0.5μs=1μs

2×0.5μs=1μs,但每 1μs 只能访存一次,无法使用;

因此采用异步刷新,刷新间隔

=

2

m

s

128

=

15.6

μ

s

=frac{2ms}{128}=15.6μs

=1282ms=15.6μs,取刷新周期为 15μs,则刷新一遍所用时间

=

15

μ

s

×

128

=

1.92

m

s

=15μs×128=1.92ms

=15μs×128=1.92ms

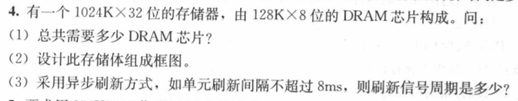

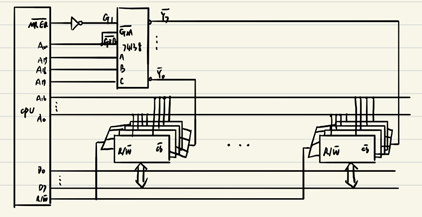

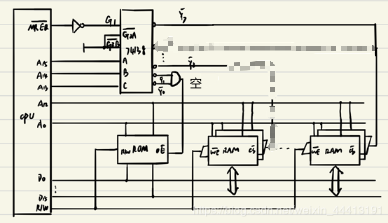

解:(1)需要进行字位扩展。字扩展需

1024

K

128

K

=

8

frac{1024K}{128K}=8

128K1024K=8 片,位扩展需

32

8

=

4

frac{32}{8}=4

832=4 片,共需

8

×

4

=

32

8×4=32

8×4=32 片

(2)

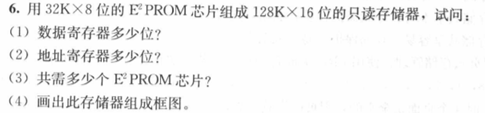

解:(1)数据寄存器 16 位

(2)地址寄存器位数

=

l

o

g

2

128

k

=

17

=log_2^{128k}=17

=log2128k=17

(3)需要进行字位扩展。字扩展需

128

K

32

K

=

4

frac{128K}{32K}=4

32K128K=4 片,位扩展需

16

8

=

2

frac{16}{8}=2

816=2 片,共需

4

×

2

=

8

4×2=8

4×2=8 片E²PROM

(4)

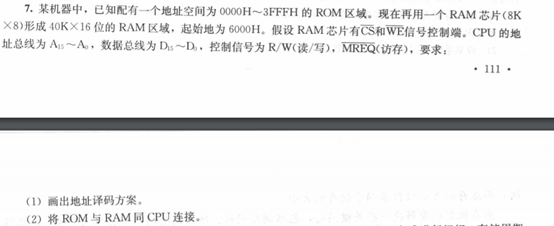

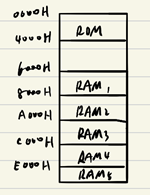

考点:地址分配;字位扩展

解:(1)ROM为

16

k

×

16

16k×16

16k×16 位。RAM区域需要进行字位扩展,字扩展需

40

k

/

8

k

=

5

40k/8k=5

40k/8k=5 片,位扩展需

16

/

8

=

2

16/8=2

16/8=2 片,共需

5

×

2

=

10

5×2=10

5×2=10 片RAM。两片 RAM 组成一个 RAM 区域。

(2)根据地址得到连接图:

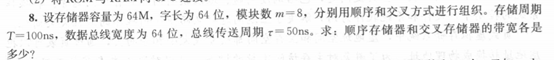

考点:顺序与交叉存储器

解:存储器连续读出

m

=

8

m=8

m=8个字的信息总量

q

=

64

×

8

=

512

b

q=64×8=512b

q=64×8=512b,顺序和交叉存储器连续读出8个字所需时间分别为:

t

1

=

m

T

=

8

×

100

n

s

=

800

n

s

=

8

×

1

0

−

7

s

t_1=mT=8×100ns=800ns=8×10^{-7} s

t1=mT=8×100ns=800ns=8×10−7s

t

2

=

T

+

(

m

−

1

)

τ

=

100

+

(

8

−

1

)

×

50

=

450

n

s

=

4.5

×

1

0

−

7

s

t_2=T+(m-1)τ=100+(8-1)×50=450ns=4.5×10^{-7} s

t2=T+(m−1)τ=100+(8−1)×50=450ns=4.5×10−7s

顺序和交叉存储器的带宽分别为:

W

1

=

q

t

1

=

512

b

8

×

1

0

−

7

s

=

640

M

b

p

s

W_1=frac{q}{t_1}=frac{512b}{8×10^{-7}s}=640Mbps

W1=t1q=8×10−7s512b=640Mbps

W

2

=

q

t

2

=

512

b

4.5

×

1

0

−

7

s

=

1138

M

b

p

s

W_2=frac{q}{t_2}=frac{512b}{4.5×10^{-7} s}=1138Mbps

W2=t2q=4.5×10−7s512b=1138Mbps

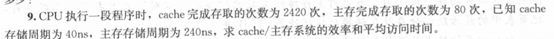

考点:cache 命中率

解:cache命中率 h = N c N c + N m = 2420 2420 + 80 = 0.968 h=frac{N_c}{N_c+N_m}=frac{2420}{2420+80}=0.968 h=Nc+NmNc=2420+802420=0.968,

主存慢于cache的倍率 r = t m t c = 240 40 = 6 r=frac{t_m}{t_c}=frac{240}{40}=6 r=tctm=40240=6,

访问效率 e = 1 r + ( 1 − r ) h = 1 6 + ( 1 − 6 ) × 0.968 = 86.2 % e=frac{1}{r+(1-r)h}=frac{1}{6+(1-6)×0.968}=86.2% e=r+(1−r)h1=6+(1−6)×0.9681=86.2%,

平均访问时间

t

a

=

t

c

e

=

40

86.2

%

=

46.4

n

s

t_a=frac{t_c}{e}=frac{40}{86.2%}=46.4ns

ta=etc=86.2%40=46.4ns

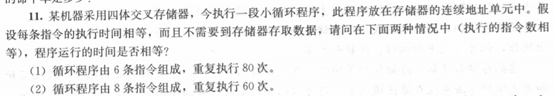

考点:交叉存储器

解:全过程分为取指和执行。设取指周期为

T

T

T,总线传送周期为

τ

τ

τ,指令执行时间为

t

0

t_0

t0

(1)

t

=

(

T

+

(

6

−

1

)

τ

+

6

t

0

)

×

80

=

80

T

+

400

τ

+

480

t

0

t=(T+(6-1)τ+6t_0 )×80=80T+400τ+480t_0

t=(T+(6−1)τ+6t0)×80=80T+400τ+480t0

(2)

t

=

(

T

+

(

8

−

1

)

τ

+

8

t

0

)

×

60

=

60

T

+

420

τ

+

480

t

0

t=(T+(8-1)τ+8t_0 )×60=60T+420τ+480t_0

t=(T+(8−1)τ+8t0)×60=60T+420τ+480t0

因此不相等。

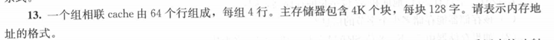

考点:cache 内存地址格式;cache 地址映射

解:字块中含有 128 字,字号位数

b

=

l

o

g

2

128

=

7

b=log_2^{128}=7

b=log2128=7。cache 中含有 64 行,每组 4 行,有 16 组,所以组地址位数

q

=

4

q=4

q=4。主存容量为 4K 个块,总容量

=

4

K

×

128

=

512

K

=4K×128=512K

=4K×128=512K 字,总位数为 19,主存字块标记位数

t

=

19

−

7

−

4

=

8

t=19-7-4=8

t=19−7−4=8.

因此内存地址格式为:

| 标记 8 位 | 组号 4 位 | 字号 7 位 |

|---|

考点:cache 内存地址格式;cache 地址映射

解:首先计算地址各部分的位数。块大小16B,因此块内地址位数 b = 4 b=4 b=4。cache容量为 64KB,字块数 = 64 K B 16 B = 4 K =frac{64KB}{16B}=4K =16B64KB=4K,则 cache 行号位数 c = 12 c=12 c=12。主存容量为1MB,总位数为 20,主存块群标记 tag 位数 t = 20 − 4 − 12 = 4 t=20-4-12=4 t=20−4−12=4。则地址格式为:

| tag 4 位 | 行号 12 位 | 字号 4 位 |

|---|

一个块群共有

2

4

=

16

2^4=16

24=16 块,则块号为 0 和 16 的地址映射到第 0 行,则内存地址可表示为:0000 000000000000 0000和0000 000000010000 0000

考点:cache 内存地址格式;cache 地址映射

解:cache 块内地址位数按照字节计算。每块 16B,则块内地址为 4 位。cache 容量为 64K 字,cache 行数 = 64 K 4 = 16 K =frac{64K}{4}=16K =464K=16K,因此 cache 行号位数 c = 14 c=14 c=14。内存总容量为 64MB,总位数为 26,主存字块标记位数 t = 26 − 4 − 14 = 8 t=26-4-14=8 t=26−4−14=8。则主存地址格式为:

| 标记 8 位 | 行号 14 位 | 字号 4 位 |

|---|

考点:页式替换策略

解:页面访问过程如下:

| 访问序号 | 说明 | 1号 | 2号 | 3号 | 4号 |

|---|---|---|---|---|---|

| 1 | 1进入 | 0 | 1 | 1 | 1 |

| 8 | 8进入 | 1 | 0 | 2 | 2 |

| 1 | 命中 | 0 | 1 | 3 | 3 |

| 7 | 7进入 | 1 | 2 | 0 | 4 |

| …… | …… | …… | …… | …… | …… |

| 7 | 命中 | 2 | 0 | 1 | 7 |

未命中的进入和替换都为页面失效,则页面失效的次数为6

考点:虚拟存储

解:虚存使用虚地址,位数为 30,主存使用物理地址,位数为 22。页面大小为 4KB,则页表长度

=

1

G

B

4

K

B

=

2

18

=

256

K

=frac{1GB}{4KB}=2^{18}=256K

=4KB1GB=218=256K

考点:TLB 表;内存访问时间

解:(1)若页表放在主存中,则访问一次主存需要两次访问主存,一次为访问页表,确定页面物理地址,第二次为根据地址存取页面数据,因此一次访问主存需要时间

=

50

n

s

×

2

=

100

n

s

=50ns×2=100ns

=50ns×2=100ns

(2)查找 TLB 时只需 1 次访存,因此内存有效访问时间

=

75

%

×

50

n

s

+

(

1

−

75

%

)

×

2

×

50

n

s

=

62.5

n

s

=75%×50ns+(1-75%)×2×50ns=62.5ns

=75%×50ns+(1−75%)×2×50ns=62.5ns

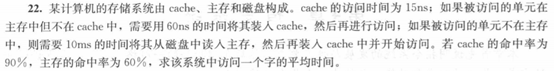

考点:cache 存储器

解:访问一个字的平均时间

=

90

%

×

15

n

s

+

(

1

−

90

%

)

×

60

%

×

60

n

s

+

(

1

−

90

%

)

×

(

1

−

60

%

)

×

(

10

m

s

+

60

n

s

)

=

4.000195

×

1

0

5

n

s

=90%×15ns+(1-90%)×60%×60ns+(1-90%)×(1-60%)×(10ms+60ns)=4.000195×10^5ns

=90%×15ns+(1−90%)×60%×60ns+(1−90%)×(1−60%)×(10ms+60ns)=4.000195×105ns

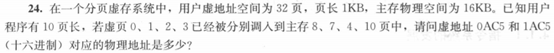

考点:页式存储管理;虚实地址映射

解:页长为 1KB,则页内地址为 10 位,主存物理页面数 = 16 K B 1 K B = 16 =frac{16KB}{1KB}=16 =1KB16KB=16页,共 4 位页面号。地址码 = 10 + 4 = 14 =10+4=14 =10+4=14位;用户虚地址空间为 32 页,有 5 位页面号,共 10 + 5 = 15 10+5=15 10+5=15位地址码。

0AC5=00010 1011000101,页面号为2,被调入主存页面4,因此物理地址中页面号为 4,页内地址与虚地址相同,因此此物理地址为00100 1011000101。

1AC5=00110 1011000101,页面号为6,未调入主存页中,无物理地址,会发生缺页中断。

最后

以上就是俊逸蜻蜓最近收集整理的关于计算机组成原理(白中英) 第三章 课后题答案的全部内容,更多相关计算机组成原理(白中英)内容请搜索靠谱客的其他文章。

发表评论 取消回复