我是靠谱客的博主 谦让树叶,这篇文章主要介绍FPGA串口任意长度字节发送前言一、任意长度字节串口发送模块端口图二、时序仿真图三、代码四、代码解释开发过程中遇到过的问题,现在分享给大家,希望可以做个参考。

前言

- 此模块的优点是顶层模块例化时可以通过传参的方法,例化任意长度的数据发送模块。在可移植性方面更加的灵活。

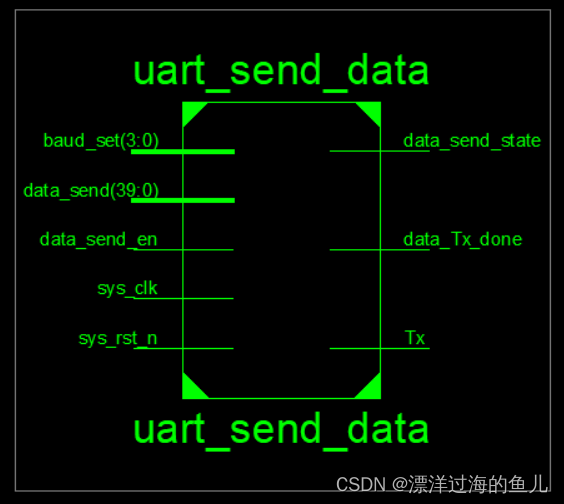

一、任意长度字节串口发送模块端口图

module uart_send_data

#( parameter data_length = 5 )

(

input [ 3: 0 ] baud_set,

input [ 8 * data_length - 1: 0 ] data_send,

input data_send_en,

input sys_clk,

input sys_rst_n,

output reg data_send_state,

output Tx,

output reg data_Tx_done

);

| 输入 | |

|---|---|

| baud_set[ 3: 0 ] | 波特率选择,提供9600、19200、38400、57600、115200以供选择 |

| data_send [ 8 * data_length - 1: 0 ] | 要发送的数据,设计此模块的star为输入数据长度可由上层模块例化时指定。 |

| data_send_en | 数据发送使能,在需要发送时,外部提供一个时钟周期长的高脉冲 |

| sys_clk | 50MHz外部时钟输入 |

| sys_rst_n | 复位信号,低电平复位,高电平系统开始运行 |

模块的二维输入端口网络定义参见我的另外一篇文章《FPGA关于二维数组端口的定义》

| 输出 | |

|---|---|

| data_send_state | 数据的发送状态指示,send_en信号产生以后到发送完要发送length的数据期间,该信号一直保持高电平 |

| Tx | 串口数据输出线 |

| data_Tx_done | 数据发送完成以后会产生一个时钟周期的高脉冲 |

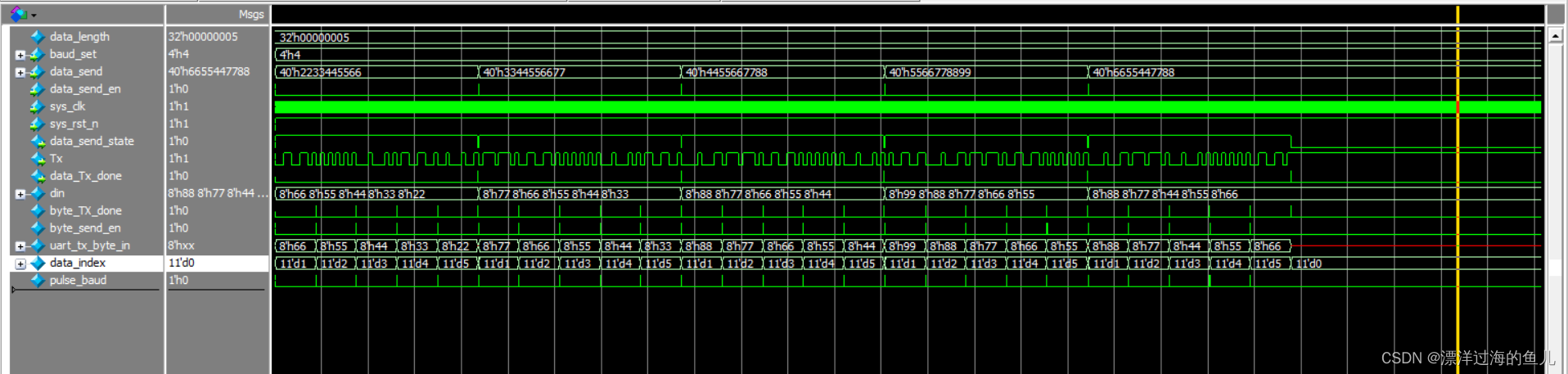

二、时序仿真图

三、代码

源文件

仿真文件

四、代码解释

1、把外部输入的一维数组的数据转化成位宽为8的二维数组数据。参考上一篇文章《FPGA关于二维数组端口的定义》。

2、send_state信号状态由data_send_en和data_Tx_done确定。当data_Tx_done输入一个时钟的高电平的时候,send_state信号变为高电平,此时模块进入到数据发送的状态。当data_Tx_done产生一个时钟的高电平的时候,send_state变为低电平,此时模块进入空闲状态,继续等待发送使能信号。

3_1、模块的内部脉冲信号pulse_baud产生的情况包括:

- 顶层模块发来send_en使能信号。

- 接收到子模块uart_send_byte发来的字节接收完成信号byte_TX_done高电平信号。但是如果所有要发送的数据全部发送完成,pulse信号就不要继续产生了。

3_2、模块的内部脉冲信号pulse_baud产生的作用包括:

- 更新data_index,使得待发送字节更新,以及发送完成信号(data_Tx_done)的产生。

- 在数据还没发送完成的情况下,为子模块产生发送使能信号(byte_send_en)。

开发过程中遇到过的问题

1.模块的端口传参不能使用二维数组,只能使用一维数组。在顶层模块与串口数据发送模块中分别要加入加包和解包的步骤。在顶层模块中可以对二维数组中的某一个byte单独进行赋值,在uart_send_data子模块中可以对二维数组的指数进行移位的方法确定要发送的数据。

2.调用数据时,数据的位宽不能用reg变量限定。

最后

以上就是谦让树叶最近收集整理的关于FPGA串口任意长度字节发送前言一、任意长度字节串口发送模块端口图二、时序仿真图三、代码四、代码解释开发过程中遇到过的问题的全部内容,更多相关FPGA串口任意长度字节发送前言一、任意长度字节串口发送模块端口图二、时序仿真图三、代码四、代码解释开发过程中遇到过内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复