原文:《A Reduced Size Look Up Table for Sinusoidal Wave Generation in Digital Modulators Applications》

首先翻译。

ABSTRACT

由于射频前端和片上系统(SoC)体系结构的巨大发展,数字调制器是近年来备受关注的领域之一。使用诸如ZYBO之类的soc型现场可编程门阵列(FPGA)构建任何类型的数字调制器,在很大程度上取决于载波信号的产生方式,因为它消耗了大量的利用资源。本文提出了一种基于直接数字合成器( Direct Digital Synthesize,DDS)概念,使用小尺寸查找表(LUT)生成正弦载波信号的新方法。将四分之一周期的正弦波信号的64个样本以定点格式存储在小型LUT中,以生成所需频率的载波。该论文在没有DSP Builder工具或XILINX System Generator的帮助下使用了超高速集成电路硬件描述语言(VHDL)。通过构建简单的调制器,如开关键控(OOK)和幅移键控(ASK),对所提出的方法进行了测试。与其他实现方法相比,利用率较低。

1 Introduction

软件无线电(SDR)或简称软件无线电(SR)是约瑟夫·梅托拉(Joseph Metola)在20世纪90年代首次提出的一种构建通信系统的新方法[1]-[2],现已成为实现各种通信系统的一种广泛使用的技术。它已经成为一种众所周知的方法,可以对现有实现的方法进行扩充,甚至取代现有的方法。基于软件无线电的系统研究领域之一是数字发射机。近年来,由于可重构硬件资源的巨大发展,数字发射机受到了极大的关注。可重构硬件资源是任何基于SDR的系统的主干。构建任何基于软件无线电的数字发射机的主要思想是使用低成本的终端(terminals),如专用集成电路(ASIC)器件或现场可编程门阵列(FPGA)作为实现的基础。

在过去的几年中,从诸如频移键控(FSK)、幅移键控(ASK)和相移键控(PSK)的简单调制方案的实现,到诸如正交幅度调制(QAM)和正交PSK(QPSK)[3]-[5]的最先进的调制方案的实现,在这个方向上取得了长足的进步。遗憾的是,几乎所有这些论文都使用MATLAB和Xilinx system Generator或DSP Builder Tools(协同仿真工具,Co Simulation Tools)作为主要实现软件[5]。使用此类软件意味着更高的成本。问题不仅在于高成本,而且它也不能让设计工程师直接控制他们实现的系统。为了解决这些问题,Al-Safi和Bazuin[6]-[7]已经发表了几篇论文,他们的工作使用VHDL作为主要的实现工具,而不使用任何Co仿真工具或知识产权(IP)模块。

本文的主要目的是通过寻找一种替代方案来降低设计成本,特别是载波产生带来的利用率提高,从而探讨减少利用率资源的可能性。利用ASK和OOK对基于新载波产生方法的系统性能进行了测试。

论文的其余部分安排如下,第二节将介绍主要的研究陈述,第三节说明目前使用的实现方法以及建议的方法。第四节介绍了取得的实施结果,第五节给出了结论和对下一步工作的建议。

2 Problem Statement 问题陈述

构建基于软件无线电概念的基于FPGA的数字发射机的主要部件是FPGA、模数转换器(ADC)、数模转换器(DAC)和射频混频器。到目前为止,常用的软件工具是带有联合仿真工具的MATLAB。在这些情况下,协同仿真工具(Co simulation tools)必须根据仿真的MATLAB模型生成基于硬件描述语言(HDL)的实现。协同仿真工具通常使用可用的IP块来构建仿真模型,这使得设计成本非常高。另一种构建基于FPGA的系统的方法是直接使用超高速集成电路硬件描述语言(VHDL)或Verilog。这种实现方式意味着对已建系统的低成本、直接控制,但可能不如使用MATLAB和Co仿真工具构建的系统效率高。

为了得到最佳的设计,我们必须寻找一种替代的设计方案,以降低使用成本,提高性能效率。载波产生、相移和乘法指令通常导致较高的使用成本。al-Safi和Bazuin提出了几篇论文,利用Feher调制概念降低了乘法指令和相移引起的实现成本 [7][8]。

本文提出了一种通过减小查找表(LUT)来降低载波产生成本的新方法。基于查找表的载波产生是实现正弦波载波的主要方式,它可以给出高分辨率的信号[9],而不是坐标旋转数字计算机(COordinate Rotation DIgital Computer,CORDIC ONE)[10]。

3 建议的实现方法

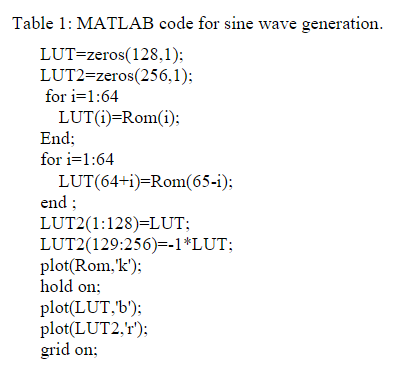

该实现方法使用FPGA内部的随机存取存储器(RAM)来存储正弦信号四分之一周期的64个定点表示值,仅用于生成整个载波。假设我们使用MATLAB以定点格式生成完整周期的正弦波信号。 从这256个样本中,我们只能使用64个样本(四分之一波)来生成整个波载波,如表中的代码所示。

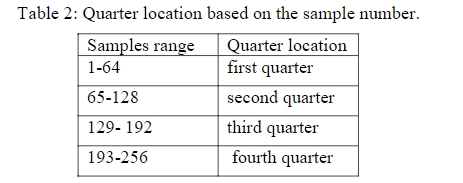

如果我们用256个样本来表示整个波浪,那么每个四分之一可以用64个样本来表示,如表所示。

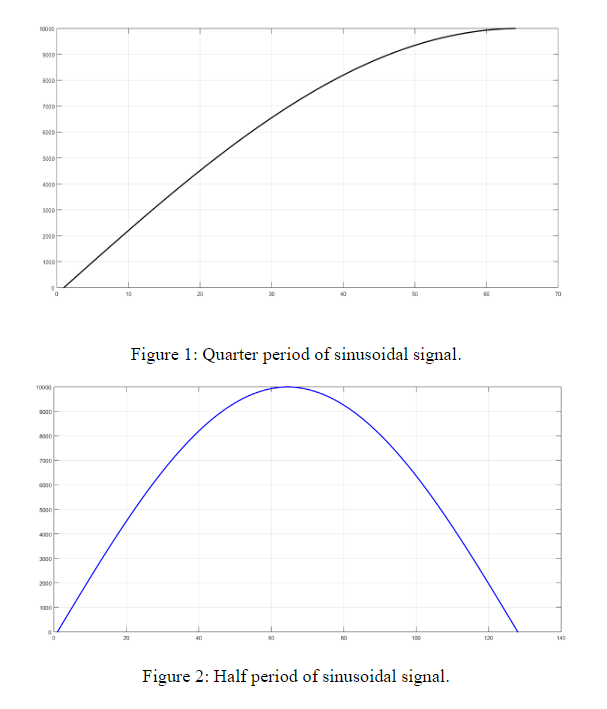

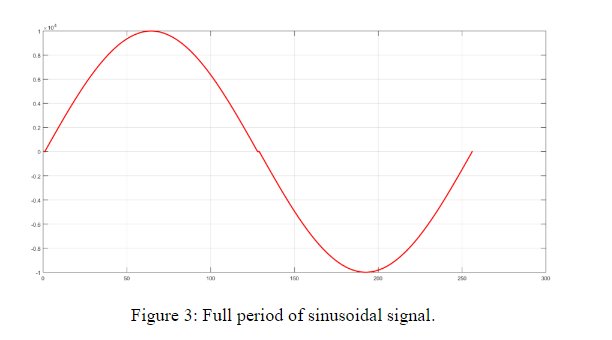

但是,如表1中的MATLAB代码所示,2-4个四分之一可以根据第一个问题中可用的样本进行计算。这背后的主要思想可以通过下面的图1-3来解释。

图1表示我们需要存储在LUT中的64个样本,以产生如图2所示的半波或如图3所示的任意所需频率的整个波形。图1:正弦信号的四分之一周期。图2:正弦信号的半周期。

在MATLAB中,此过程看起来非常简单,但在VHDL中,此过程要复杂得多。

4 Implementation and Results 实施与结果

采用第三节提出的基于DDS直接数字合成器( Direct Digital Synthesize,DDS),概念的减小尺寸LUT产生正弦波的方法,实现了两种数字调制器。所选择的调制器是二进制ASK(BASK)和OOK,因为OOK和ASK是最简单的调制方案,如图4所示。

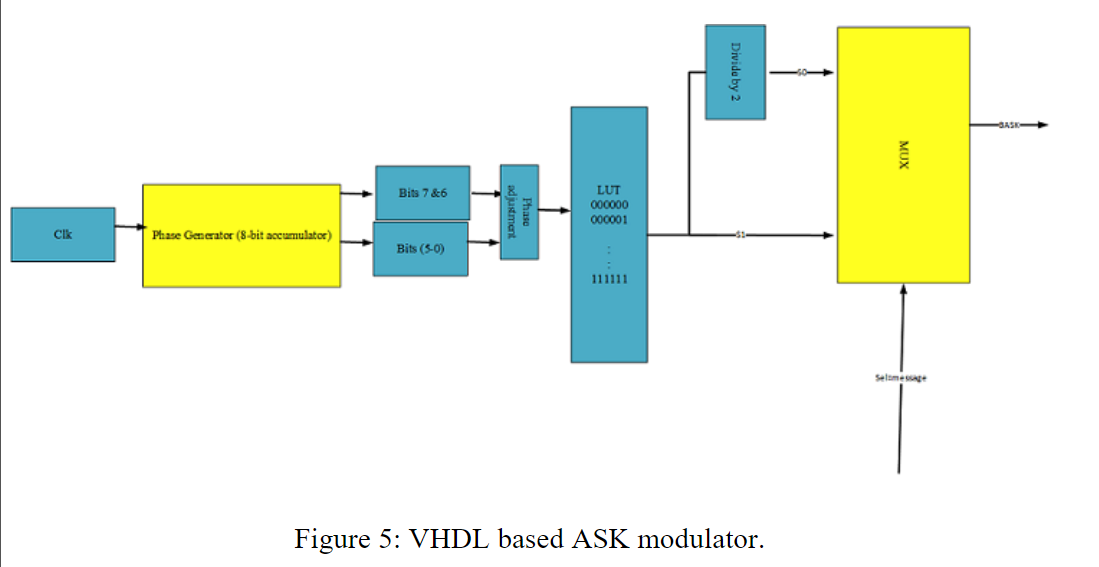

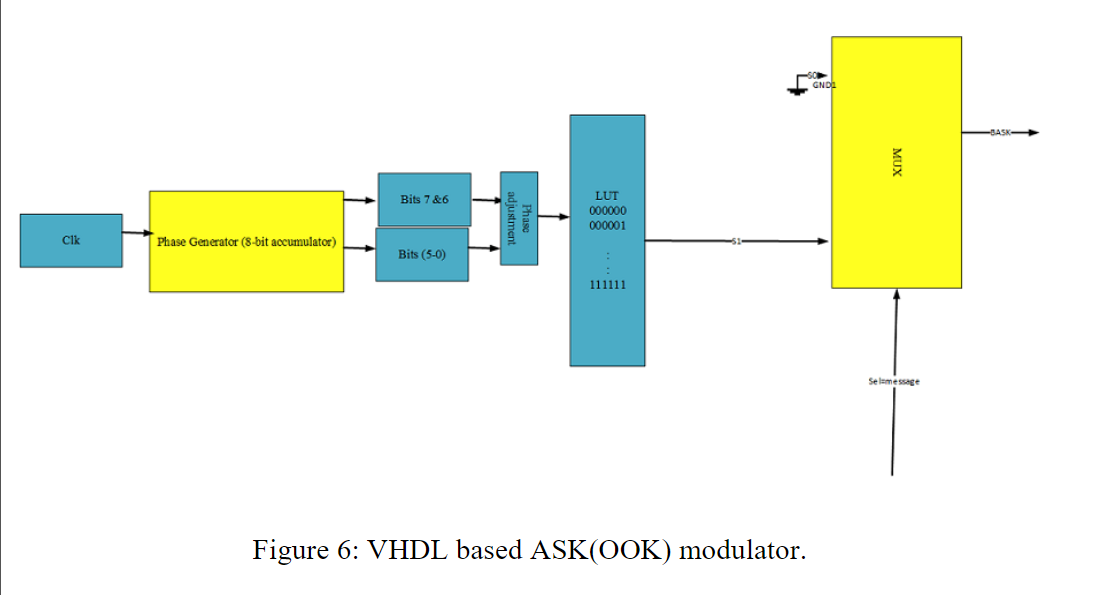

对于ASK调制器实现,使用了工作在时钟上升沿的8位相位累加器。该累加器生成所需的相位以覆盖0-360之间的角度。累加器的两个最高有效位用于选择角度位于哪个四分之一。 累加器的其余6位用于查找LUT,以查找该角度对应的正弦波固定值。必须使用表1中MATLAB代码中介绍的相同概念来调整获得的正弦值,以反映角度的位置。现在,所生成的正弦波可以分别用于实现如图5-6所示的BASK或OOK调制器。

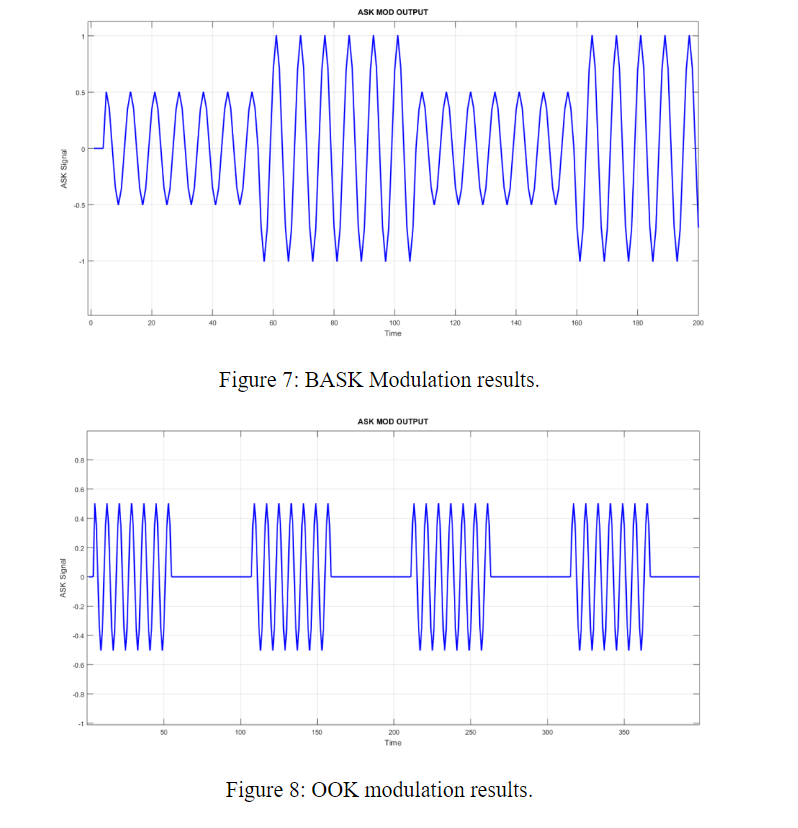

而不是使用256个样本LUT,这次64个样本将足以产生载波。信息信号用作MUX电路选择器,如图5所示。多路复用器MUX电路的输入是两个正弦信号,而信息信号将作为选择器工作。这两个正弦波可以由相同的64值LUT和8位累加器产生。生成的正弦波信号指的是消息位“1”,而第二个信号指的是消息位“0”是将其幅度除以2后生成的正弦波。在VHDL中进行幅度划分的最好方法是使用向右移位操作,如图5所示。输出正弦波和BASK调制信号的宽度选择为16位。8位宽度也可以,但我们正在寻找更平滑、更清晰的信号。仿真和实现中使用的消息信号是由主板时钟驱动的简单计数器产生的。

在OOK调制器中,根据信息信号的不同,调制后的输出信号可以是正弦波,也可以是零。实现这种形式的ASK几乎与前一种类似。我们现在要做的唯一改变是在多路复用器电路中给它一个地信号,而不是图6所示的一个正弦波信号。调制的BASK和OOK信号分别如图7-8所示。

要将设计下载到FPGA板上(ZYBO),我们需要编写.xdc文件,该文件解释了使用的输入和输出引脚。实现的目标板是Digilent[11]的ZYBO板,如图9所示。ZYBO板是基于Xilinx Zynq-7000(Z-7010)系列设备构建的入门级嵌入式平台。Z-7010基于Xilinx可编程SoC架构,将双核ARM Cortex-A9处理器与Xilinx 7系列FPGA集成。ZYBO板具有丰富的多媒体和连接外设,包括: 视频和音频I / O,双角色USB,板载内存,以太网和SD插槽。 除这些外设外,它还包含六个PMOD端口,其引脚连接到Xilinx器件,可以连接到一系列可用器件。 不幸的是,要获得具有16位的终端并不容易。 因此,我们使用JEpmod输出之一,该输出具有8个引脚,并使用了输出结果的八个最高有效位,只是为了查看资源利用率报告。

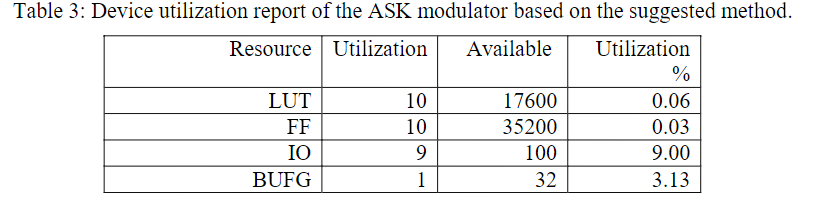

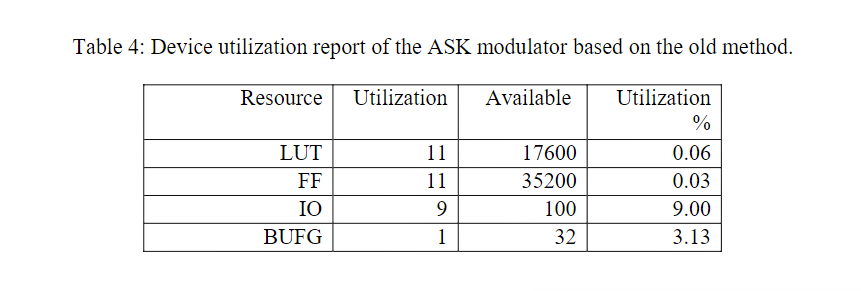

将设计下载到板上后,我们获得了内置ASK调制器的项目利用率报告,如表所示。 3看起来比基于全周期正弦波的利用率更好,如表4所示。

5 结论与未来工作

本文提出了一种用于数字调制器的正弦波生成新方法。 通过实现简单的OOK和ASK调制器对提出的方法进行了测试。 减少了资源利用。 即使不是很明显,但对于大型系统设计而言,资源利用率的降低将对整体设计产生巨大影响。 作为未来的工作,作者建议使用提出的方法来构建其他类型的数字调制器,以检查其性能并遵循参考文献[12]。 比较新的实现方法与旧的实现方法的性能,尤其是在资源利用率和IP块使用方面。

最后

以上就是聪慧蛋挞最近收集整理的关于一种用于数字调制器中正弦波产生的小尺寸查找表ABSTRACT1 Introduction2 Problem Statement 问题陈述3 建议的实现方法4 Implementation and Results 实施与结果5 结论与未来工作的全部内容,更多相关一种用于数字调制器中正弦波产生的小尺寸查找表ABSTRACT1内容请搜索靠谱客的其他文章。

发表评论 取消回复