Scan Synthesis practice

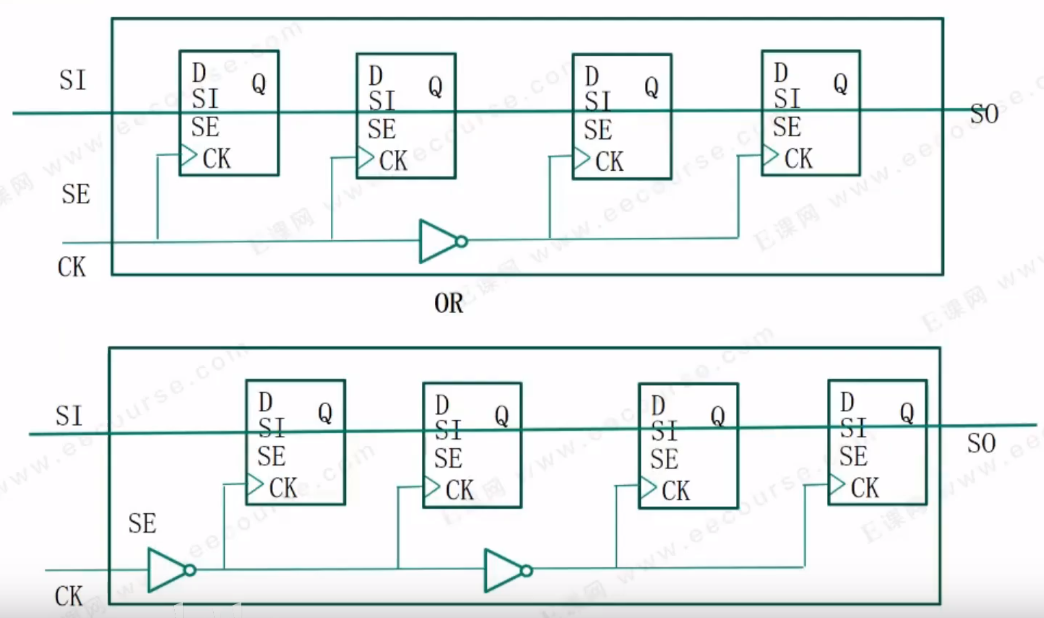

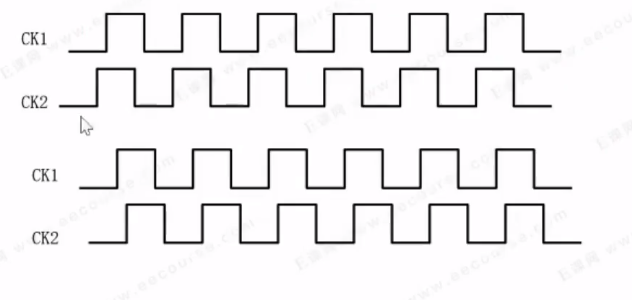

- 时钟负沿和正沿的顺序

一般选择下面的第二种,负沿在前,正沿在后

主要分析方法:

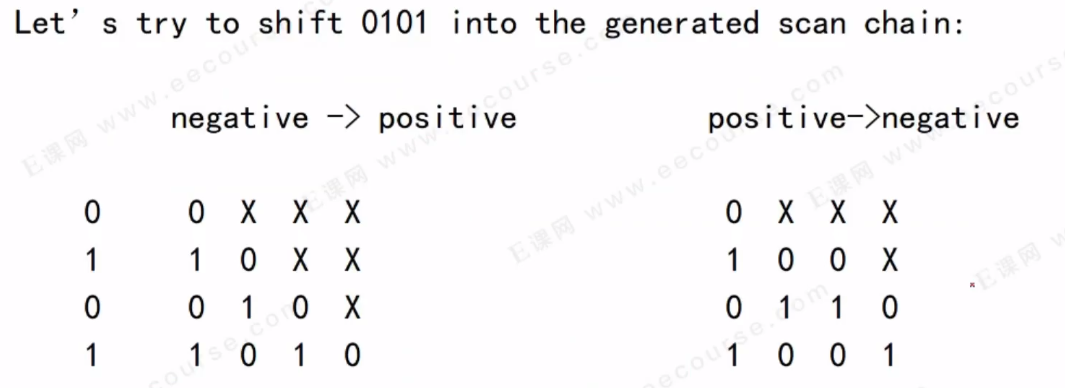

shift in 角度:

先正沿后负沿的结果,在传01时,第三个正沿会拿到前面一个负沿的值。 造成负沿总会和正沿采到的值一样。

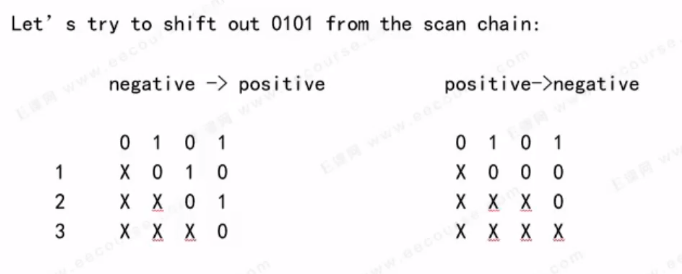

shift out 角度:

两种结构的优劣:

采用先正后负的情况:在shift in的情况,会出现两个寄存器在一个周期的出现一样的值;

对于shift out 的情况,会出现第二个负寄存的值出现丢失的情况,没办法shift 出来。

所以采用先负沿后正沿的时钟结构

遵循的规则: 越最后capture的值的cell 越放在前面,保证不会caputre前面的一个值。

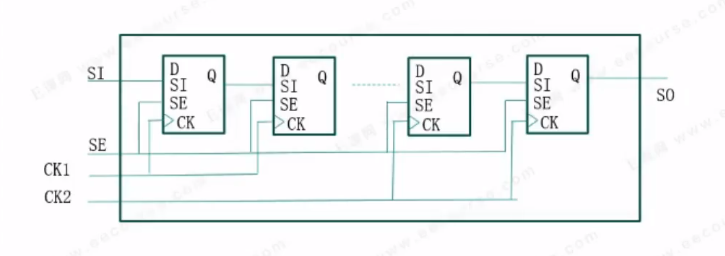

- 多个clock设计

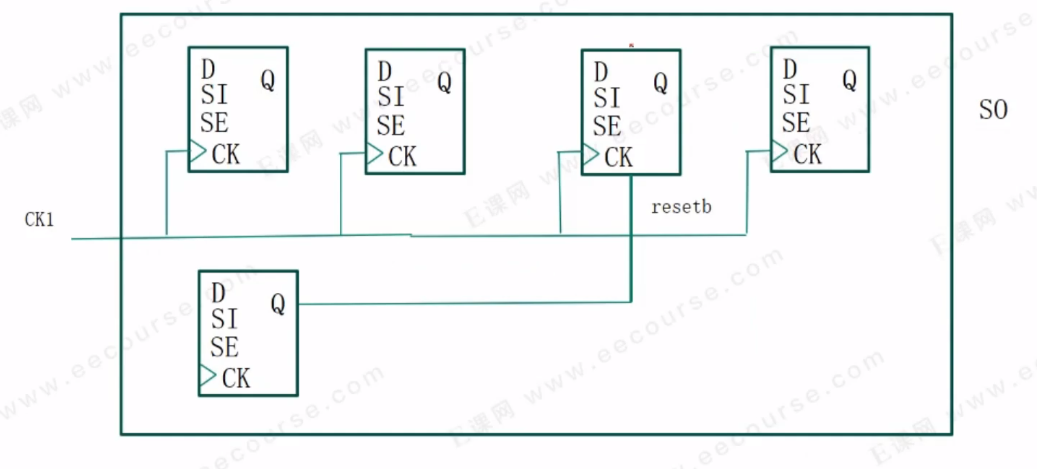

对于如下的四个cell,是否是简单的前后连接?(如下图)

clock到达各个寄存器的时间不一样,会导致不同的时间前后。

尤其是clk1 和clk2 之间的时钟沿(clock tree):

第三个总是capture第二个寄存器的值(涉及到时钟问题)

第一种:clk1 后,clk2前(uesful skew)

第一种:clk1 先,clk2后(不采用)

会提前capture 新值,导致值丢失。

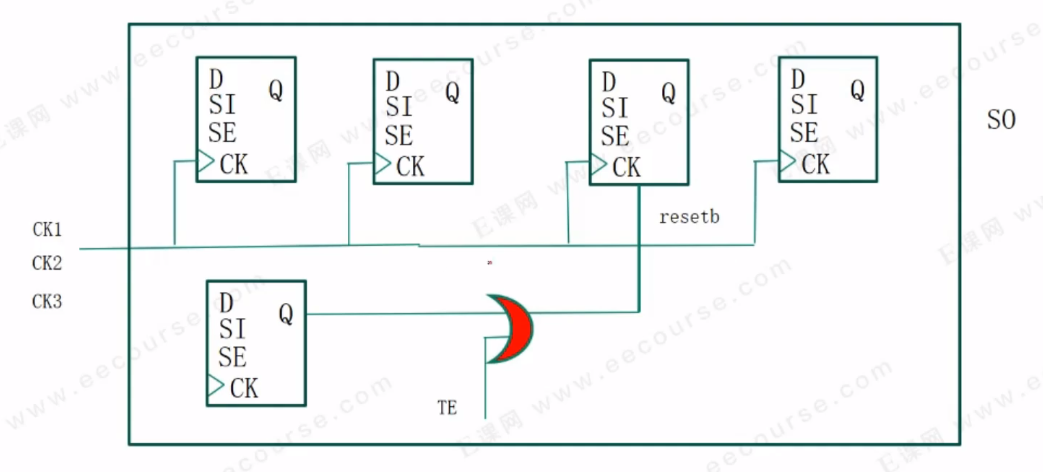

解决办法:

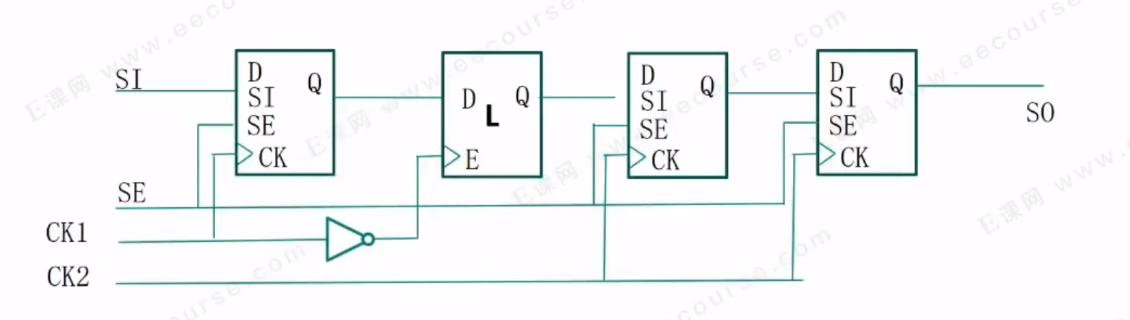

对于以下情况,不能简单的串连接

第二个增加 lock up cell(latch)(反的时钟沿),相当于在下降沿取值,相当于前面的一个clk capture值更晚,及改善第二种时钟关系为第一种(半个clk)牺牲setup 换取hold 时间(hold比较难满足)

-

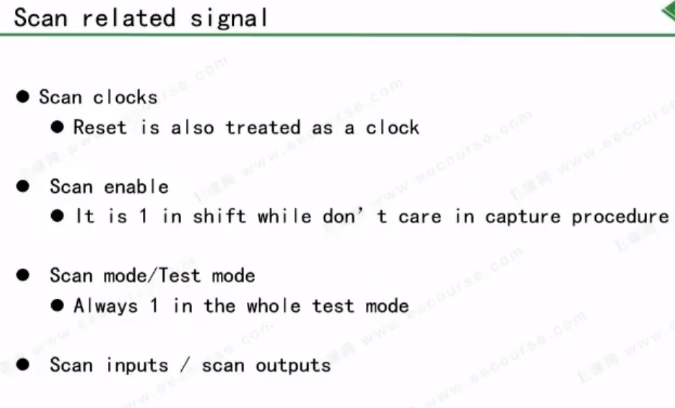

SCan related siganl

scan mode 在测试的时候始终为1

scan enable 可以变化

scan input /scan output -

设计规则——时钟

check cell 是否能放在chain 链,如果不能改变设计

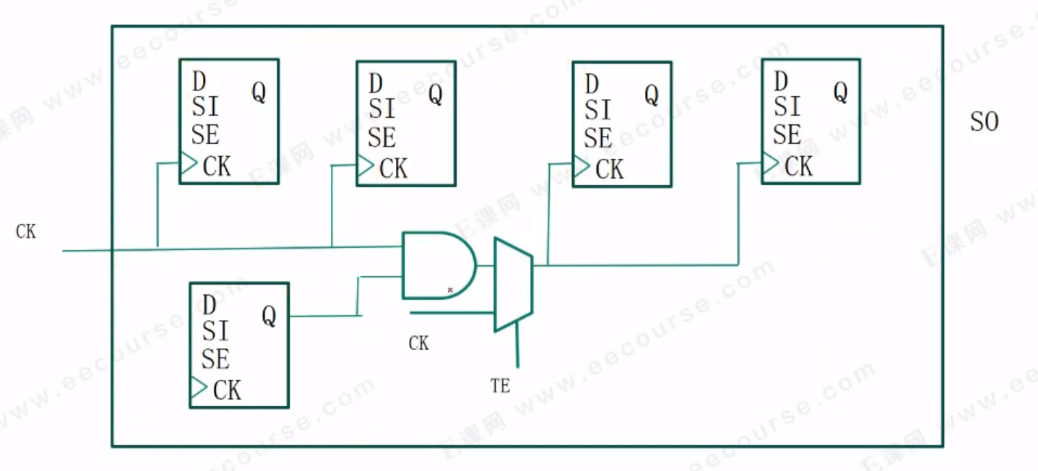

添加test mode ,添加MUX,mode = 0 处于function mode mode =1,处于chain 链

该设计的两种方法:RTL更改(主流);工具,自动修复

-

设计规则——复位(set/reset)

更改后的结果:

-

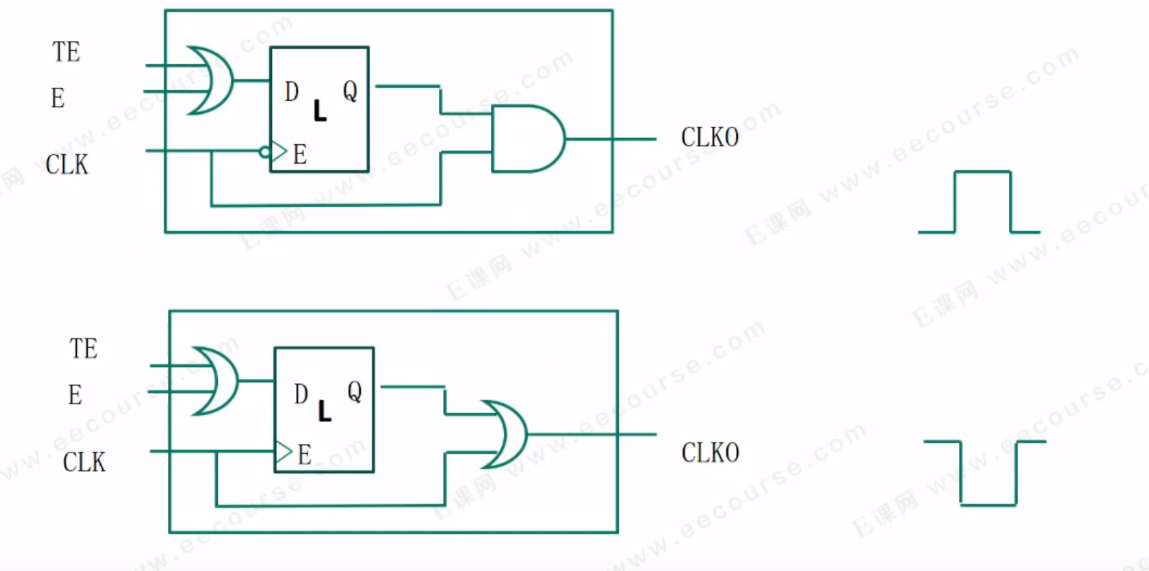

Clock gating cell

主要目的:节省power

E:由function logic 控制

TE: test mode

最后

以上就是威武芝麻最近收集整理的关于SOC Scan Synthesis practice(扫描链scan chain分析)的全部内容,更多相关SOC内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复