验证方法的分类

验证的方法大体可以分为两类:动态验证和静态验证

动态验证

动态验证也叫仿真,是指从电路的描述提取模型,然后将外部激励信号或数据施加于此模型,通过观察该模型在外部的激励信号作用下的实时响应来判断该电路系统是否实现了预期的功能。

静态验证

静态验证通过采用分析电路的某些特性是否满足设计要求的方法,来验证电路的正确与否。

形式验证就是常见的静态验证。

形式验证是近几年来兴起的一种验证方法,它需要一个正确的模型作为参考,把待验证的电路与正确的模型进行比较,并给出不同版本的电路是否在功能上等效的结论,它利用理论证明的方法来验证设计结果的正确性。

动态验证 vs 静态验证

动态仿真验证主要是模拟电路的功能行为,必须给出适当的激励信号,然而很难选择激励来达到覆盖电路所有功能的目的,同时动态仿真很耗费时间。

静态验证是针对模拟电路所有的工作环境,检查电路是否满足正常的性能指标,此类验证只限于数字逻辑电路,其准确性低于动态仿真,偶尔还会提供错误信息。

动态验证及相关工具

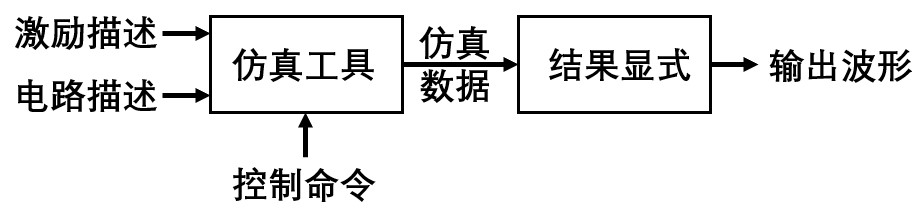

如下图所示,仿真环境包括 电路描述的输入、仿真控制命令和仿真结果的显式等3部分。

仿真工具首先要把用户的描述转换为内部表示,即建立模型。激励波形可以同电路一起输入,也可以在仿真开始之后通过控制命令输入,或者单独建立激励波形文件输入。

控制命令包括:初始值设置、仿真时间指定、仿真过程控制、仿真中断设置、观察仿真状态、设置某些信号或者变量值,以及指定继续仿真 等。在交互式仿真方式下,控制命令交互输入;在批量处理式仿真方式下,控制命令常由控制命令文件(脚本)一次输入。仿真结果主要为各外部输出端和其他观察点的输出波形,以及其他一些检查结果信息。

验证工程师应该根据所验证的电路的应用环境给出足够多的激励信号,以验证该电路是否可以正确的工作。但是当所验证的电路非常复杂时,很难把电路在各种工作条件下的工作情况都验证到,并且验证的时间将直接影响项目的开发周期。这时,就要验证人员凭经验给出比较具有代表性的激励信号,以尽量少的激励来验证电路的全部功能。

- 动态仿真工具-VCS

Synopsys的VCS是编译型Verilog模拟器,它完全支持标准的Verilog HDL语言和SDF,其出色的内存管理能力足以支持千万门级的ASIC设计,而其模拟精度也完全满足深亚微米ASIC Sign-Off的要求。VCS结合了周期算法和时间驱动算法,具有高性能、大规模和高精度的特点,适用于从行为级、RTL到反标的门级电路仿真。

静态仿真及相关工具

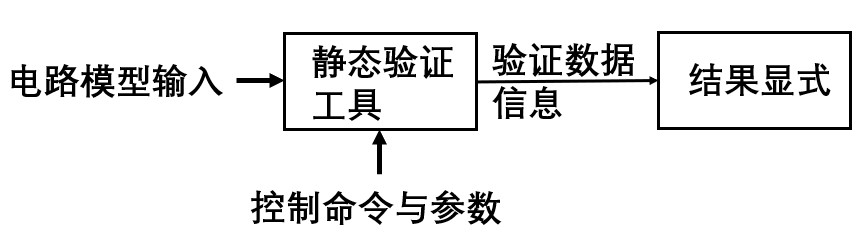

如图为静态验证流程。静态验证不需要输入激励信息,只需要输入电路模型和相关参数及命令,验证工具会自动对该电路模型进行分析,并显示出分析的结果。

由于静态验证是由工具自动完成的,不需要人工过多的干预,所以通常对所设计的电路首先进行静态验证,以纠正一些比较明显的错误,然后再动态仿真,确定其具体行为是否正确。

形式验证

对于某些电路设计的移植,一般不需要对新电路进行仿真,而直接通过EDA工具来分析该电路的功能是否与原电路一致,此种验证方法可以大量减少验证时间,提高电路设计的效率。

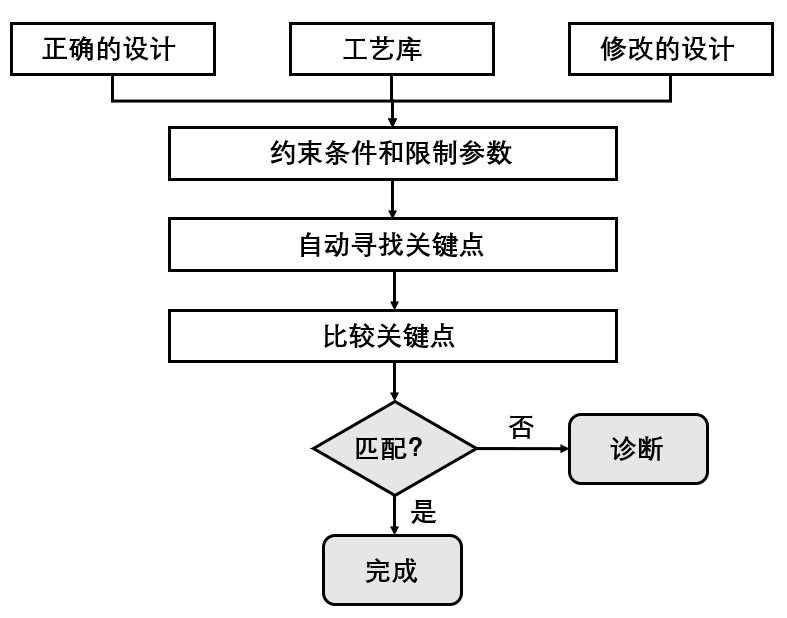

如下图为形式验证流程

目前形式验证的主流为 等效性检查(Equivalence Check),用于比较两个电路逻辑功能的一直行。它通过采用匹配点并比较这些点之间的逻辑来完成等效性检查。其生成一种数据结构,并将其与相同输入特性曲线条件下的输出数值特性曲线进行比较。如果它们不同,则表示被比较的两个电路是不等效的。

- 形式验证工具-Synopsys公司的Formality

- 工具的使用流程

首先需要给工具提供完整正确的设计、相关的工艺库及准备验证的设计;其次需要对检查过程给定约束条件和设置参数,并确定比较范围和匹配点,如果结果不相等则需要进行诊断。它通常用来比较RTL代码与布局布线后提取的网表逻辑功能是否一致,加入扫描链之前与之后的网表在正常工作模式下的功能是否一致,并对ECO修正之前的网表与ECO修正之后的网表比较。

参考:《SoC设计方法与实现》

最后

以上就是痴情丝袜最近收集整理的关于数字IC验证方法的分类验证方法的分类的全部内容,更多相关数字IC验证方法内容请搜索靠谱客的其他文章。

发表评论 取消回复