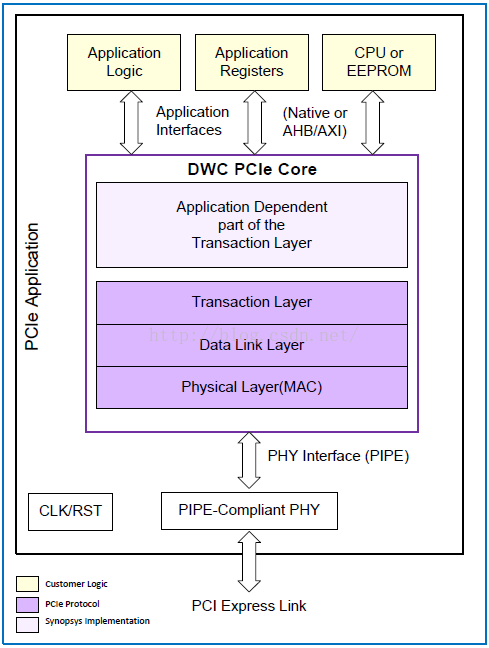

(1). PCIe 协议栈总览

上图是整个 PCIe 的软件框架、PIPE-CompliantPHY 部分的 SERDES 模块、DWC PCIe Core 包含 Physical Layer (MAC)、 DATA Link Layer、 Transaction Layer 和 Application Dependent part of the Transaction Layer,此部分为 PCIe Core 内容。用户驱动部分内容是 Application Logic、Application Registers 内容。

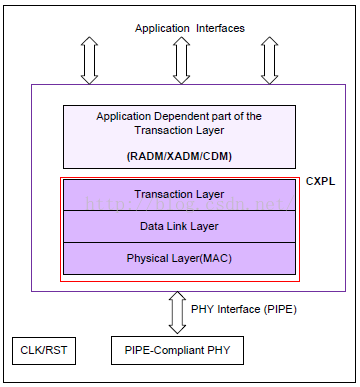

(2)、PCIe 组件定义

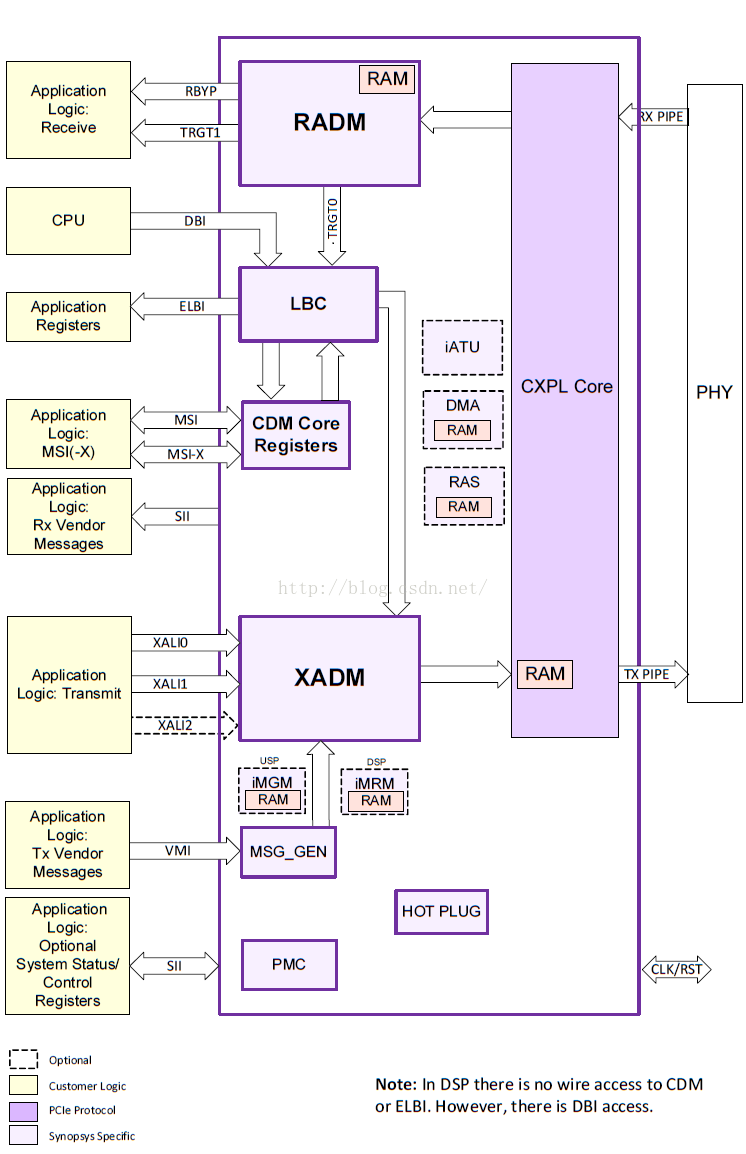

包含4个重要的模块,CXPL、RADM、XADM、CDM。

(2.1) CXPL: Common ExpressPort Logic (CXPL) Module

CXPL是整个协议的核心部分,包含了物理层、数据链路层和传输层。

(2.2) XADM: TransmitApplication-Dependent Module

面向数据包发送的应用模块,主要包括以下3个功能:

a、 TLP(Transaction Layer Packet) arbitration,传输报仲裁

b、 TLP formation , 传输包格式

c、 Flow control credit checking, 流控审计

(2.3) RADM: ReceiveApplication-Dependent Module

面向数据包接收的应用模块,主要包括以下3个功能:

a、 Sorting/filtering of received TLPs. The filtering rules and routing are configurable.

b、Buffering and queuing of the received TLPs.

c、Routing of received TLP to the core’s receive interfaces.

(2.4) CDM : Configuration-Dependent Module

a、 Standard PCI Express configuration space

b、Core-specific register space (Port Logic Registers)

(3)、PCIe 的内部结构关系

作为用户,我认为需要知道以上各个接口的作用和用法,并且知道每个接口需要在整个传输中扮演的角色,对应驱动调试是非常有帮助的。

此框架的用户接口逻辑部分、更利于我们理解 PCIe 驱动程序的框架。

模块定义说明:

PMC: Power Management Controller

LBC : Local Bus Controller

DBI : Data Bus Interface

MSG_GEN: MessageGeneration Module

HOT PLUG:Hot Plug ControlModule

RBYP: Receive Bypass Interface

TRGT1: Receive Request Interface

ELBI: External Local Bus Interface

MSI: Message Signaled Interrupt (MSI) Interface,

MSI-X Interface,在DPDK中选择的中断模式,使用此接口。

XALI 0/1/2 : Transmit Interfaces 0/1/2

VMI : Vendor Message Interface

SII : System Information Interface

以上模块接口、在驱动中都有相应部分。

(4) Core operation 、驱动 初始化

1、 先disable link training

2、 通过DBI(data bus interface)配置core的stickyregisters,需要配置什么目前不知道??????

3、 Enable link training

4、 等待link完成。

5、 root Complex枚举Downstream Device(什么是Downstreamdevice????)

Ø 读取 Downstream device的配置空间

Ø 配置device的capabilites(具体配置什么???)

Ø 配置switch ports(???) 的base和limit寄存器,以反映devices enumerated downstream的BAR(Base Address Register)的范围。

Ø 配置endpoint的BAR。

6、 使能BME、MSE、ISE。

7、 开始传输数据。

参考连接:

https://www.synopsys.com/designware-ip/interface-ip/pci-express.html

https://blog.csdn.net/yijingjijng/article/details/48028809

最后

以上就是爱笑电话最近收集整理的关于2 --> PCIE 协议栈的框架详解的全部内容,更多相关2内容请搜索靠谱客的其他文章。

发表评论 取消回复